Abstract

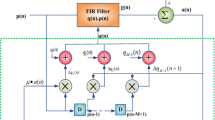

Variable digital filter (VDF) plays a significant role in communication and signal processing field. Any prototype filter's preferred frequency response is attained by creating All Pass Transformation (APT) based filter to maintain complete control over the cut-off frequency. However, the speed, power, and area usage of the digital filter are constrained by its performance. Therefore, in this manuscript, All Pass Transformation based Variable digital filters (APT-VDF) using Error Reduced Carry Prediction Approximate Adder (ERCPAA) andSandpiper Optimization fostered Approximate Multiplier (SO-AM) is proposed. The proposed APT-VDF-ERCPAA-SOAM filter design is utilized for enhancing the filter efficiency by reducing noise in the sensor nodes. The proposed ERCPAA design is incorporated with carry prediction and constant truncation for diminishing the path delay and area utilization. Moreover, the proposed SO-AM is used for minimizing the design complexity and power utilization. The simulation of the proposed method is activated in Verilog and the design is synthesized in FPGA uses Xilinx ISE 14.5. The proposed APT-VDF- ERCPAA- SO-AM filter design has attained 35.6%, 21.75%, 28.69% lower power and 46.58%, 12.3%, 38.07% lower delay than the existing approaches, like Very Large-Scale Integration design of All Pass Transformation based Variable digital filters uses a new variable block sized ternary adder (VBSTA) and ternary multiplier (APTVDF-VBSTA-TM), Finite Impulse Response (FIR) adaptive filter design by hybridizing canonical signed digit (CSD) and approximate booth recode (ABR) algorithm in DA architecture (FIR- CSDABR-DA) and digital FIR filter design using Carry Save Adder (CSA) and Structured Tree Multiplier (FIR-CSA-STM) respectively.

Similar content being viewed by others

Data availability

Data sharing is inappropriate to this article as no new data were created examined in this study.

References

Shrivastava, P., Kumar, P., Tiwari, M., & Dhawan, A. (2020). Efficient architecture for the realization of 2-D adaptive FIR filter using distributed arithmetic. Circuits Systems and Signal Processing, 40(3), 1458–1478. https://doi.org/10.1007/s00034-020-01539-y

Niveditha, V., Palaniappan, S., Naresh, K., Nayak, C., & Swapna, B. (2021). High speed low area decimation filter for hearing aid application. International Journal of Speech Technology. https://doi.org/10.1007/s10772-021-09857-5

Bose, S., De, A., & Chakrabarti, I. (2021). Area-delay-power efficient VLSI architecture of FIR filter for processing seismic signal. IEEE Transactions on Circuits and Systems II: Express Briefs, 68(11), 3451–3455. https://doi.org/10.1109/tcsii.2021.3081257

Pathan, A., & Memon, T. (2020). Sigma-delta modulation based single-bit adaptive DSP algorithms for efficient mobile communication. Circuits Systems and Signal Processing, 40(4), 1788–1801. https://doi.org/10.1007/s00034-020-01553-0

Chandra Inguva, S., & Seventiline, J. (2021). Implementation of FPGA design of FFT architecture based on CORDIC algorithm. International Journal of Electronics, 108(11), 1914–1939. https://doi.org/10.1080/00207217.2020.1870750

Rammohan, S. R., Jayashri, N., Bivi, M. A., Nayak, C. K., & Niveditha, V. R. (2020). High performance hardware design of compressor adder in DA based FIR filters for hearing aids. International Journal of Speech Technology, 23(4), 807–814. https://doi.org/10.1007/s10772-020-09759-y

Li, F., Wang, D., Wang, Y., Yu, X., Wu, N., Yu, J., & Zhou, H. (2020). Wireless communications and mobile computing blockchain-based trust management in distributed internet of things. Wireless Communications and Mobile Computing, 2020, 1–12. https://doi.org/10.1155/2020/8864533

Jyothi, G., Sanapala, K., & Vijayalakshmi, A. (2020). ASIC implementation of distributed arithmetic based FIR filter using RNS for high speed DSP systems. International Journal of Speech Technology, 23(2), 259–264. https://doi.org/10.1007/s10772-020-09683-1

Rajesh, P., Shajin, F. H., Rajani, B., & Sharma, D. (2022). An optimal hybrid control scheme to achieve power quality enhancement in micro grid connected system. International Journal of Numerical Modelling: Electronic Networks, Devices and Fields. https://doi.org/10.1002/jnm.3019

Christilda, V., & Milton, A. (2021). Speed, power and area efficient 2D FIR digital filter using vedic multiplier with predictor and reusable logic. Analog Integrated Circuits and Signal Processing, 108(2), 323–333. https://doi.org/10.1007/s10470-021-01853-8

Shajin, F. H., Rajesh, P., & Raja, M. R. (2022). An efficient VLSI architecture for fast motion estimation exploiting zero motion prejudgment technique and a new quadrant-based search algorithm in HEVC. Circuits Systems and Signal Processing, 41(3), 1751–1774. https://doi.org/10.1007/s00034-021-01850-2

Rajesh, P., Shajin, F. H., Mouli Chandra, B., & Kommula, B. N. (2021). Diminishing energy consumption cost and optimal energy management of photovoltaic aided electric vehicle (PV-EV) by GFO-VITG approach. Energy Sources Part A: Recovery Utilization and Environmental Effects. https://doi.org/10.1080/15567036.2021.1986606

Shajin, F. H., & Rajesh, P. (2022). FPGA realization of a reversible data hiding scheme for 5G MIMO-OFDM system by chaotic key generation-based paillier cryptography along with LDPC and its side channel estimation using machine learning technique. Journal of Circuits Systems and Computers, 31(05), 2250093. https://doi.org/10.1142/S0218126622500931

Sakthimohan, M., & Deny, J. (2020). WITHDRAWN: An Optimistic Design of 16-Tap FIR Filter with Radix-4 Booth Multiplier Using Improved Booth Recoding Algorithm. Microprocessors and Microsystems. https://doi.org/10.1016/j.micpro.2020.103453

Coutinho, V. A., Ariyarathna, V., Coelho, D. F., Pulipati, S. K., Cintra, R. J., Madanayake, A., & Dimitrov, V. S. (2020). A low-SWaP 16-beam 2.4 GHz digital phased array receiver using DFT approximation. IEEE Transactions on Aerospace and Electronic Systems, 56(5), 3645–3654. https://doi.org/10.1109/taes.2020.2987094

Prakash, M., & Ahamed, S. (2021). A distributed arithmetic based realization of the least mean square adaptive decision feedback equalizer with offset binary coding scheme. Signal Processing, 185, 108083. https://doi.org/10.1016/j.sigpro.2021.108083

Gul, S., Siddiqui, M., & Rehman, N. (2020). FPGA-based design for online computation of multivariate empirical mode decomposition. IEEE Transactions on Circuits and Systems I: Regular Papers, 67(12), 5040–5050. https://doi.org/10.1109/tcsi.2020.3012351

Das, P., Naskar, S., & Narayan Patra, S. (2019). Fast converging cuckoo search algorithm to design symmetric FIR filters. International Journal of Computers and Applications, 43(6), 547–565. https://doi.org/10.1080/1206212x.2019.1588512

Coelho, L., Lovisolo, L., & Tcheou, M. (2022). Adaptive filtering with reduced computational complexity using SOPOT arithmetic. IEEE Transactions on Circuits and Systems I: Regular Papers, 69(2), 746–756. https://doi.org/10.1109/tcsi.2021.3119285

Di Meo, G., De Caro, D., Saggese, G., Napoli, E., Petra, N., & Strollo, A. (2022). A novel module-sign low-power implementation for the DLMS adaptive filter with low steady-state error. IEEE Transactions on Circuits and Systems I: Regular Papers, 69(1), 297–308. https://doi.org/10.1109/tcsi.2021

Lee, J., Seo, H., Seok, H., & Kim, Y. (2021). A novel approximate adder design using error reduced carry prediction and constant truncation. IEEE Access, 9, 119939–119953. https://doi.org/10.1109/access.2021.3108443

Kaur, A., Jain, S., & Goel, S. (2019). Sandpiper optimization algorithm: A novel approach for solving real-life engineering problems. Applied Intelligence, 50(2), 582–619. https://doi.org/10.1007/s10489-019-01507-3

Chinnusamy, G., & Shanmugasundaram, D. (2021). Genetic fuzzy optimized approximate multiplier design based non-linear anisotropic diffusion image denoising in VLSI. Journal of Ambient Intelligence and Humanized Computing. https://doi.org/10.1007/s12652-021-03027-w

Mandloi, A., & Pawar, S. (2020). VLSI design of APT-VDF using novel variable block sized ternary adder and multiplier. Microprocessors and Microsystems, 78, 103266. https://doi.org/10.1016/j.micpro.2020.103266

Satish Reddy, K., & Suresh, H. (2019). A low-power VLSI implementation of RFIR filter design using radix-2 algorithm with LCSLA. IETE Journal of Research, 66(6), 741–750. https://doi.org/10.1080/03772063.2019.1620644

Katnam, R., & Penumutchi, B. (2021). High performance IIR filter design with MOD-GDI based array multiplier. Materials Today Proceedings. https://doi.org/10.1016/j.matpr.2021.01.476

Samyuktha, S., & Chaitanya, D. (2020). VLSI design of efficient FIR filters using Vedic mathematics and ripple carry adder. Materials Today Proceedings, 33, 4828–4832. https://doi.org/10.1016/j.matpr.2020.08.391

Mandloi, A., & Pawar, S. (2021). Power and delay efficient fir filter design using ESSA and VL-CSKA based booth multiplier. Microprocessors and Microsystems, 86, 104333. https://doi.org/10.1016/j.micpro.2021.104333

Arumugam, N., & Paramasivan, B. (2021). An integrated FIR adaptive filter design by hybridizing canonical signed digit (CSD) and approximate booth recode (ABR) algorithm in DA architecture for the reduction of noise in the sensor nodes. Multidimensional Systems and Signal Processing, 32(4), 1277–1311. https://doi.org/10.1007/s11045-021-00783-y

Aathilakshmi, S., Vimala, R., & Britto, K. (2021). Anelegance of novel digital filter using majority logic on pipelined architecture for SNR improvement in signal processing. Journal of Ambient Intelligence and Humanized Computing. https://doi.org/10.1007/s12652-021-03197-7

Acknowledgements

The authors extend their appreciation to the Deanship of Scientific Research at King Khalid University for funding this work through Research Project under grant number (RGP.1 / 311/44).

Funding

The author(s) disclosed receipt of the following financial support for the research, authorship article: This research was funded by the Deanship of Scientific Research at King Khalid University, grant number RGP.1 / 311/44.

Author information

Authors and Affiliations

Contributions

MRR Conceptualization, Methodology, Writing- Original draft preparation. RN Supervision. CADD Supervision. MU Supervision. NKS Supervision. MAM Supervision.

Corresponding author

Ethics declarations

Competing interests

The authors declare no competing interests.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Raja, M.R., Naveen, R., Durai, C.A.D. et al. Energy efficient enhanced all pass transformation fostered variable digital filter design based on approximate adder and approximate multiplier for eradicating sensor nodes noise. Analog Integr Circ Sig Process 118, 399–413 (2024). https://doi.org/10.1007/s10470-023-02201-8

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-023-02201-8