Abstract

In three-phase four-wire systems, unbalanced loads can cause grid currents to be unbalanced, and this may cause the neutral point potential on the grid side to shift. The neutral point potential shift will worsen the control precision as well as the performance of the three-phase four-wire unified power quality conditioner (UPQC), and it also leads to unbalanced three-phase output voltage, even causing damage to electric equipment. To deal with unbalanced loads, this paper proposes a matching-ratio compensation algorithm (MCA) for the fundamental active component of load currents, and by employing this MCA, balanced three-phase grid currents can be realized under 100% unbalanced loads. The steady-state fluctuation and the transient drop of the DC bus voltage can also be restrained. This paper establishes the mathematical model of the UPQC, analyzes the mechanism of the DC bus voltage fluctuations, and elaborates the interaction between unbalanced grid currents and DC bus voltage fluctuations; two control strategies of UPQC under three-phase stationary coordinate based on the MCA are given, and finally, the feasibility and effectiveness of the proposed control strategy are verified by experiment results.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

At present, the three-phase four-wire power supply network has been widely used in the 380 V low-voltage power supply system [1, 2], in which each phase can operate independently. If there is no effective compensation, unbalanced grid currents will emerge because of a single-phase load or unbalanced loads, and these will cause a zero sequence current flow in the neutral line of the grid side. The more unbalanced the loads are, the greater neutral line current is. Usually, the neutral line of the grid side is selected as a reference ground for both the power and control circuit in a three-phase four-wire system. The neutral potential is not zero when a larger current flows through the neutral line, and this will lead to an offset over the reference ground. As a result of this ground offset, the control precision and performance of the overall UPQC will be deteriorated, and then three-phase load voltages become unbalanced. Each phase voltage may be above or below the rated voltage to a different extent, and this will tend to cause damage to the electrical equipment [3].

To overcome the influence of unbalanced loads on the grid side neutral potential shift, it is necessary to control the three-phase grid currents to keep them in a sinusoidal and balanced state under unbalanced loads. The unified power quality conditioner (UPQC) [4,5,6,7,8,9,10,11,12,13] has the ability to compensate for unbalanced load currents and to realize the balance control of the grid currents.

In terms of grid current control, three independent H-bridges are used to form a parallel active power filter, and the single-phase p-q theory is employed to control the grid currents, so as to keep them in a balanced state [4, 5]. However, in this structure six more IGBTs are needed compared with a three-phase half-bridge inverter, and this will increase the control complexity and the cost. In [6], the grid current and load voltage references in both dq and αβ coordinates are calculated, and then hysteresis control is used to achieve grid current balance. However, the switching frequency of hysteresis control is not constant, and in [6] the design of appropriate LC filters is not considered. In [7], the grid currents are controlled as balanced sinusoidal currents in the positive and negative sequence double synchronous rotating coordinates under unbalanced loads. However, the implementation of this method requires multiple coordinate transformations, and the number of controllers in the closed-loop control is relatively larger, so control complexity is increased. The reactive power compensation and admittance calculation method are used to realize grid current balance control based on the balanced component method [8, 9]. In using this method, the unbalanced loads need to be decomposed, and the admittance calculation is also necessary. This makes the calculation rather complicated.

In a direct control scheme [10, 11] for UPQC, the DC bus voltage will be involved in the generation process of the grid current reference. The output result of the DC bus voltage loop is directly used as the grid current reference generation in [12, 13]. However, the DC bus voltage will produce a larger fluctuation under unbalanced loads, and this may cause the current reference to be distorted and thus the sine and balance degrees of the grid currents to be poor. Because of the low bandwidth and slow response of the DC bus voltage loop, the DC bus voltage will produce a large transient drop with a load step-up, exacerbating the deterioration of the control effect of the grid currents. To overcome the above shortcomings, a matching-ratio compensation algorithm (MCA) for the fundamental active component of load currents is proposed to calculate the grid current reference, so as to optimize the sine and balance degrees of the grid currents, reduce the steady-state fluctuation of the DC bus voltage, and improve the dynamic response speed of the DC bus loop. At the same time, the mutual influence between DC bus voltage fluctuations and unbalanced grid currents can also be weakened.

When a system is controlled in the three-phase stationary coordinate, the traditional proportional-integral (PI) controller [14] cannot achieve the zero steady-state error control. Therefore, a resonant (R) controller is employed to achieve zero steady-state error in [15]. The nonlinear loads may cause the output voltages of the inverter to be distorted, and thus multi-resonant (MR) controllers are employed to effectively control several low-order harmonics with high content in the nonlinear load currents in [16], so as to improve the waveform quality of the inverter voltage. In this paper, the UPQC is controlled in the three-phase stationary coordinate. The references of both converters are the fundamental sine quantities, considering the influence of the nonlinear loads, the PI + MR control method is employed to improve the waveform qualities of the grid currents and load voltages for the UPQC.

This paper aims to realize the balance control of three-phase grid currents under unbalanced loads. Compared with the aforementioned control strategies in [4,5,6,7,8,9,10,11,12,13], the control strategy based on the proposed MCA possesses a better control performance and can be realized more easily.

This paper is organized as follows. After this introduction and in Section 2, the mathematical model of UPQC is established, and the mechanism of DC bus voltage fluctuation is analyzed thoroughly; then the control strategy based on the MCA is given under the three-phase stationary coordinate, and the essence of the mutual influence between the DC bus voltage fluctuations and the unbalanced grid currents is revealed. To reduce the steady-state errors of PI controllers in the three-phase stationary coordinate, the MR controllers are added to the control loop of the two converters. Considering the most serious unbalanced loads (a single-phase load), the operation state of UPQC is thoroughly described and three important conclusions are obtained in Section 3. Finally, experimental results show that three-phase grid currents can be maintained in a sinusoidal and balanced state under the single-phase resistive and nonlinear load by using the proposed MCA strategy. The neutral line current on the grid side fluctuates slightly around zero. The steady-state fluctuation and the transient drop of the DC bus voltage can be reduced. The correctness of the theoretical analysis and the feasibility of the given strategy are verified by experiment results.

2 Theoretical analysis

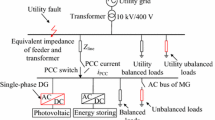

The three-phase four-wire UPQC mainly consists of two bidirectional converters connected back-to-back sharing a common DC bus, as shown in Fig. 1.

It should be noted that Sabc are turned on at the positive and negative half cycles of the grid voltage. Once the grid short circuit, Sabc can cut off the connection between the UPQC and grid in time, so as to prevent the UPQC from generating a large short circuit current to feed back to the grid. The primary and secondary sides of Trabc are connected to the grid and series converter, with turn ratio n = N1:N2 = 1:5.

The direct control scheme [10, 11] employed is described as follows: (a) The series converter is controlled to operate as a sinusoidal current source. It has the current source characteristic with impedance high enough for harmonic voltages, and thus mutual pollution between the source and load can be avoided [17]. The grid currents are controlled by the series converter to be sinusoidal, balanced and always in phase with the grid voltages, and the DC bus voltage is stabilized at a desired level; (b) The parallel converter is controlled to operate as a sinusoidal voltage source. It has the voltage source characteristic with impedance small enough to harmonic currents, and it provides the reactive power and harmonic currents for loads [11]. The load voltages are controlled by the parallel converter to be sinusoidal, balanced and in phase with the grid voltages.

2.1 Modeling and control of series converter

-

1)

Mathematical model of series converter

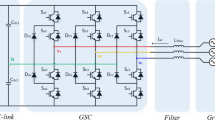

The series converter topology is shown in Fig. 2, where idco2 is the zero sequence current generated by the unbalanced loads and load voltages, and iso is the zero sequence current generated by the output currents of the series converter iserabc. Since the grid currents iSabc are controlled by the currents iserabc, the current iso is equivalent to the neutral current of the grid side iSN.

The main reason for the unbalanced grid currents is the DC bus voltage fluctuations caused by the unbalanced loads. Therefore, it is necessary to establish the mathematical model of the series converter and analyze the mechanism of DC bus voltage fluctuations.

Let Lserabc = Lser, and the state space average model of the series converter is as follows:

where Rser is the equivalent resistance of Lser.

The relationship among the secondary side voltages of series transformers ucnabc, grid voltages uSabc and load voltages uLabc is:

If output currents of the series converter iserabc are unbalanced, they can be expressed as:

The zero sequence current idco2 generated by the unbalanced loads ZLabc and load voltage uLo can be expressed as:

The switching states of the series converter are represented by the switching function S1j: (1) S1j = 1 when jth leg upper switch is turned on and jth leg lower switch is turned off, (2) S1j = − 1 when jth leg lower switch is turned on and jth leg upper switch is turned off.

where subscript 1 represents the series converter.

Based on (5), the three-leg voltages of the series converter u1abc can be expressed as:

The positive and negative DC bus currents idc± can be expressed as:

Based on the instantaneous power theory [18], ignoring the inductance resistance Rser, an energy expression is derived from (1) to (7):

where \(a_{ 1} = i_{\text{sera}}^{2} + i_{\text{serb}}^{2} + i_{\text{serc}}^{2}\).

The left side of (8) is the instantaneous output power of the series converter pser, and it can be expressed as:

The positive and negative DC capacitor currents idc1± can be expressed as:

Substituting (9) and (10) into (8), pser can be further expressed as:

The expressions of positive and negative DC bus voltages udc± can be derived from (10):

where Udco+ and Udco− are the initial voltages of capacitors Cdc+ and Cdc− respectively.

Let Cdc+ = Cdc− = Cdc and Udco+ = Udco− = Udco, the difference of udc+ and udc− can be derived from (12):

It can be derived from (11) that:

where Wo is the initial energy stored on the capacitor Cdc.

The total DC bus voltage udc can be obtained based on (13) and (14):

From (13) and (15), the expressions of positive and negative DC bus voltages udc± can be rewritten as:

The mechanism of DC bus voltage fluctuations can be revealed by (15) and (16). That is, the DC bus voltage udc and udc± will fluctuate with the changes of the power pser, currents iserabc and neutral current idco.

However, udc will be involved in the generation process of the grid current reference. If the fluctuation of udc is larger than a certain level, it will deteriorate with the sine and balance degrees of the grid currents, leading to increasing the neutral current iSN, which exacerbates the DC bus voltage fluctuation in turn. Thus, based on the above analysis, it can be clearly seen that there is a mutual influence between the DC bus voltage fluctuation and the neutral currents. In addition, in the topology proposed, the neutral current of the load side flows into the neutral point of the positive and negative DC capacitors, resulting in a larger DC bus voltage fluctuation which is proportional to the load unbalance degree.

-

2)

Control strategy of series converter

To overcome the adverse influence of DC bus voltage fluctuation on the balance control of grid currents, this paper proposes the MCA to calculate the grid current reference. Three ways for improvement are presented: (a) it can suppress influence of the DC bus voltage fluctuation on the sine and balance degrees of the grid currents; (b) it can reduce the steady-state fluctuation of the DC bus voltage; (c) it can improve the response speed of the DC bus voltage loop, so as to reduce a large transient drop of DC bus voltage with a load step-up. Considering (a), (b) and (c), the MCA can finally reduce the mutual influence between the DC bus voltage fluctuation and unbalanced grid currents.

The proposed MCA is described as follows: First the grid voltages uSabc, load voltages uLabc and load currents iLabc are transformed by dq transformation:

where \(\bar{u}_{\text{Sd}}\), \(\bar{u}_{\text{Ld}}\) and \(\bar{i}_{\text{Ld}}\) are the DC components, and they represent the fundamental active components. \(\tilde{u}_{\text{Sd}}\), \(\tilde{u}_{\text{Ld}}\) and \(\tilde{i}_{\text{Ld}}\) are the AC components, and they represent the harmonic components.

Generally, certain harmonics and imbalance usually exist in the grid voltages, so the AC component \(\tilde{u}_{\text{Sd}}\) obtained after dq transformation is not zero. In addition, the load voltages and currents after dq transformation must contain the ac components \(\tilde{u}_{\text{Ld}}\) and \(\tilde{i}_{\text{Ld}}\) with the nonlinear loads. The above ac components will bring in an error during the grid current reference calculation process, and to solve this problem, low pass filters (LPFs) are employed to eliminate these ac components.

In (17), (18) and (19), \(\bar{u}_{\text{Sd}}\), \(\bar{u}_{\text{Ld}}\) and \(\bar{i}_{\text{Ld}}\) represent the fundamental amplitude of grid voltages, load voltages and load currents, respectively, and they can be obtained by filtering uSd, uLd and iLd with LPFs.

According to the instantaneous power theory, ignoring the system loss, the fundamental active powers on the grid side and load side are equal, as follows:

The proposed MCA for load fundamental active current can be expressed as:

It can be seen from (21) that \(\bar{i}_{\text{Sd}}\) can adjust the magnitude of the grid current with the changes of the load active power \(\bar{u}_{\text{Ld}} \bar{i}_{\text{Ld}}\) and the grid voltage \(\bar{u}_{\text{Sd}}\), and thus \(\bar{i}_{\text{Sd}}\) has adaptability to grid voltages.

Based on the proposed MCA and mathematical model of the series converter, the control block diagram of the series converter in a three-phase stationary coordinate is given, as shown in Fig. 3. It can be seen that there is a mutual influence between the DC bus voltage fluctuation and unbalanced grid currents.

The DC bus voltage loop can compensate for the UPQC internal loss, and is also a link of cooperative work between serial and parallel converters.

The transfer function of PI controller Gdc(s) for the DC voltage loop can be expressed as:

where kdcp and kdci are the proportional and integral coefficient of Gdc(s), respectively.

The output signal of the DC voltage loop \(\Delta i_{\text{d}}^{ * }\) can be expressed as:

The grid current reference amplitude is obtained by adding the value of \(\bar{i}_{\text{Sd}}\) calculated by the MCA and the output signal \(\Delta i_{\text{d}}^{ * }\):

In contrast, there is no the MCA part in [12, 13], and the reference Idref is implemented only by the output signal of the DC bus voltage loop, i.e. Idref = \(\Delta i_{d}^{ * }\). The DC bus voltage udc with a larger fluctuation will make the grid currents iSabc unbalanced or even distorted, but after adding the MCA, it can be found that the reference Idref is shared by \(\bar{i}_{\text{Sd}}\) and \(\Delta i_{\text{d}}^{ * }\), where \(\bar{i}_{\text{Sd}}\) takes most of the current reference from (21) and (24), so as to reduce the influence of the DC bus voltage fluctuation on iSabc.

The a-phase of the series converter is designed as an example. Its control block diagram is shown in Fig. 4, where kPWM is the equivalent gain of the converter, Gsam(s) is the current sampling link and isera_s is the sampling value of the current isera.

The current sampling link can be equivalent to a first-order inertia link, and its transfer function Gsam(s) is:

where ksam_ser and Tsam_ser are the current isera sampling coefficient and filter delay time (s), respectively.

The current loop of the series converter is controlled by the PI + MR controllers, where the PI controller can correct the current loop to a type II system to improve the system’s anti-jamming performance; the MR controllers are used to control the fundamental and harmonics components to improve the control accuracy of the series converter and the waveform qualities of the grid currents.

With the increase of the harmonic order, the harmonic components will decrease rapidly, and thus the influence of the high harmonic components on the load voltages is limited. Therefore, the MR controllers mainly control for the lower harmonics. Taking into account the cost of digital control computation, the fundamental and 3th, 5th and 7th harmonics are selected in this paper.

The transfer function of PI + MR controllers GPIMR(s) can be expressed as:

where kserp and kseri are the proportional and integral coefficient, respectively. kr is the resonant coefficient, ωc is the cut-off frequency (rad/s), ωo is the resonant frequency ωo = 100π (rad/s), and h is the harmonic order.

The design method of MR controllers can be found in [16]. The parameters of the GMR(s) controller are as follows: kr = 50 and ωc = 5rad/s.

Figure 5 is the bode plot of GPIMR(s). The gain of the low frequency-band is determined by the gain of the PI controller. The PI controller plays a major role in the overall regulation process. The MR controllers will generate a large gain at the desired resonant points, and the performance of the PI controller is reflected at other frequency-bands outside the resonant points, so the parameters of GPI(s) will be designed accordingly.

The design process of the PI controller in [14] is now applied. Let the shear frequency of the current loop ωseri_cut = 3340π rad/s (1/10 of the switching frequency 16.7 kHz), and then the turning frequency Rser/Lser is much smaller than ωseri_cut, so the resistor Rser can be ignored in Fig.4. The current loop is corrected to a type II system, and the transfer function of the current open-loop Gop_seri(s) can be expressed as:

where the current open-loop gain kop_seri = kPWM ksam_ser/Lser.

The turning frequency of the zero point of Gop_seri(s) is 1/5 of ωseri_cut, and thus the relation between kserp and kseri can be expressed as:

The modulus of the transfer function Gop_seri(s) at the shear frequency ωseri_cut is equal to 1, and the following equation can be obtained:

According to (28) and (29), the parameters of GPI(s) are as follows: kserp = 6.43 and kseri = 819.

The modulation signals of the series converter \(u_{\text{serabc}}^{ * }\)can be expressed as:

The three-phase grid current references irefabc can be derived from the grid current reference amplitude using the inverse dq transformation:

where ωt is obtained by a phase-locked loop (PLL) [19].

Under the control of the series converter, the neutral current of the grid side iSN is equal to zero.

2.2 Modeling and control of parallel converter

-

1)

Mathematical model of parallel converter

The main task of the parallel converter is to ensure that the load voltages uLabc are sinusoidal and balanced, and also to provide the required harmonic and reactive currents for loads. The parallel converter topology is shown in Fig. 6.

The modeling process of the parallel converter is the similar as that of the series converter, and the mathematical model expressions of the DC bus voltage in the parallel converter are given directly in this section.

The state space average model of the parallel converter is as follows:

where Rpar is the equivalent resistance of inductor Lpar.

The parallel converter will output a zero sequence current iLN under the unbalanced loads:

The total DC bus voltage udc can be expressed as:

where \(b_{ 1} = i_{{ 2 {\text{a}}}}^{2} + i_{{ 2 {\text{b}}}}^{2} + i_{{ 2 {\text{c}}}}^{2}\) and \(b_{2} = u_{\text{La}}^{2} + u_{\text{Lb}}^{2} + u_{\text{Lc}}^{2}\).

The expressions of positive and negative DC bus voltages udc± can be expressed as:

It can be seen from (35) and (36) that the DC bus voltage udc and udc± will fluctuate with the changes of the power ppar, currents i2abc, voltages uLabc and neutral current idco.

The unbalanced load voltages will also cause fluctuations in the DC bus voltage, and thus the control objective of the parallel converter is to keep the three-phase load voltages sinusoidal and balanced, so as to minimize the impact of the load voltages on the DC bus voltage.

-

2)

Control strategy of parallel converter

Based on the mathematical model of the parallel converter, a double closed-loop control strategy for the parallel converter under three-phase stationary coordinate is given, as shown in Fig. 7, where i2a_s and uLa_s are the sampling values of i2a and uLa, respectively. To reduce the steady-state errors of PI controllers, MR controllers are added in the voltage outer-loop.

The control block diagram of the current inner-loop is shown in Fig. 8. To eliminate the disturbance of the load voltage to the current loop, the load voltage (uLa) feedforward control is added to the current inner-loop.

The transfer function of the current sampling Gsami(s) in the parallel converter can be expressed as:

where ksam_pari and Tsam_pari are the sampling coefficient and filter delay time (s) of the current i2a, respectively.

The current inner-loop represents the tracking performance, so it is designed as a type I system. A PI controller is employed by the current inner-loop, and its transfer function GPIi(s) can be expressed as:

where kparip and kparii are the proportional and integral coefficient of GPIi(s), respectively.

After the zero point of GPIi(s) and the pole point of 1/(Lpars + Rpar) cancellation, the transfer function of the current open-loop Gop_pari(s) can be expressed as:

where the current open-loop gain kop_pari = kPWM ksam_pari km, and the proportional relationship km = kparip / Lpar = kparii / Rpar.

The parameter calculation of GPIi(s) is the same as that of the series converter. Let the shear frequency of the current loop ωpari_cut = 3340π rad/s, and the parameters of GPIi(s) are: kparip = 0.96 and kparii = 319.

The transfer function of the current closed-loop Gcl_pari(s) can be expressed as:

Ignoring the higher order term Tsam_paris2 in (40), Gcl_pari(s) can be reduced order to:

The control block diagram of the voltage outer-loop is shown in Fig. 9, where the PI + MR controllers are employed for the load voltages, and their transfer function is shown in (26).

The transfer function of the voltage sampling Gsamu(s) can be expressed as:

where ksam_paru and Tsam_paru are the sampling coefficient and filter delay time (s) of the voltage uLa, respectively.

The PI controller transfer function of the voltage outer-loop GPIu(s) can be expressed as:

where kparup and kparui are the proportional and integral coefficient of GPIu(s), respectively.

The transfer function of the voltage open-loop Gop_paru(s) can be expressed as:

where the voltage open-loop gain kop_paru = ksam_paru / (ksam_pari Cpar), and the sum of the small inertia time constants T∑paru = Tsam_paru + 1/ (kop_pari).

Let the shear frequency of the voltage loop ωparu_cut = 668π rad/s (1/5 of ωpari_cut), and the parameters of GPIu(s) are as follows: kparup = 0.16 and kparui = 77.6.

The load voltage references urefabc can be expressed as:

where Uref is the desired amplitude of load voltages.

The current loop references \(i_{\text{refabc}}^{ * }\) can be expressed as:

The modulation signals of the series converter \(u_{\text{parabc}}^{ * }\) can be expressed as:

3 Case analysis of single-phase load

By employing the proposed control strategies, UPQC can compensate for unbalanced load currents caused by unbalanced loads, so that the grid currents can be kept in sinusoidal and balanced state. Here we take the most serious unbalanced loads (100% unbalanced load) as an example to do some analysis. To better illustrate the compensation effect of the UPQC for the unbalanced load current, the operation schematic and phasor diagram only with a-phase load are shown in Fig. 10.

Under the control of the series converter, the a-phase load fundamental active current iLa can be evenly distributed to each phase on the grid side, so the three-phase grid currents iSabc are still maintained in a sinusoidal and balanced state. Seen from the grid side, the whole system is in a three-phase balanced state. iSabc can be expressed as:

From (48), each phase grid current is equal to 1/3 of the load fundamental active current.

Under the control of parallel converter, the a-phase current of the parallel converter ipara is in phase with the a-phase grid current iSa, and provides the 2/3 load current iLa for the load. The b- and c-phase grid currents iSb, iSc are absorbed by the b- and c-phase of the parallel converter. Therefore, the a-phase load current iLa is jointly provided by the grid and parallel converter.

The output currents of the parallel converter iparabc can be expressed as:

The three-phase load currents iLabc can be expressed as:

The neutral currents on both the grid and load side iSN, iLN can be obtained as:

Thus the following conclusions can be drawn on unbalanced loads: (1) Each phase grid current is 1/3 of the sum of three-phase load fundamental active currents; (2) The neutral current on the grid side is zero, whereas the neutral current on the load side is equal to the load unbalanced currents; (3) The parallel converter absorbs and converts the grid currents to ensure the operation of unbalanced loads.

4 Experimental validation

Two DSPs (TMS320F28335) are used as the controllers of the series and parallel converters. Experimental parameters are: the rms values of grid and load voltage are 220 V, their frequencies are 50 Hz; the switching frequencies of the two converters are 16.7 kHz; the positive and negative DC bus voltages are ±400 V; the a-phase rated load power is 9.35 kW; the a-phase rated load is 5.18 Ω.

The experimental results of the a-phase resistance load with the MCA are shown in Fig. 11. To verify the aforementioned important functions of the proposed MCA, the comparative experiments are carried out in terms of the sine and balance degrees of the grid currents, the neutral current of the grid side and the steady-state fluctuation and the transient drop of the DC bus voltage, as shown in Fig. 12.

The grid voltages uSabc, grid currents iSabc, load voltages uLabc and load currents iLabc are shown in Fig. 11a–d. The percentage of unbalanced load is 100% only with a-phase rated load. It can be seen from Fig. 11b, c that three-phase grid currents iSabc and load voltages uLabc remain in a good sinusoidal and balanced state under the proposed control strategies. Moreover, the grid currents iSabc with the system loss are controlled to be in phase with the grid voltages, and their rms values are 16.9 A, 16.6 A and 16.5 A, respectively, which are approximately 1/3 of the a-phase load current iLa (42.6 A rms). Compared with Fig. 12a, because of the influence of the DC bus voltage fluctuations (as described in Section 2.1), the sine and balance degrees of the grid currents iSabc without the proposed MCA are obviously poorer, and the rms values of the currents iSabc are 18.6 A, 19.7 A and 20.5 A, respectively.

The output currents of parallel converter iparabc are shown in Fig. 11e. The a-phase current ipara is in phase with the a-phase grid voltage uSa, indicating that the a-phase of the parallel converter supplies 2/3 of the load current for the a-phase load. The b- and c-phase currents iparb, iparc are reversed with the b- and c-phase grid voltage uSb, uSc, indicating that the b- and c-phase of the parallel converter absorb 1/3 of load current from the grid side.

The neutral current of the load side iSN is equal to the a-phase load current iLa in Fig. 11f. Under the control of series and parallel converters, the neutral current of the grid side iSN is very small, fluctuating in a small range around the zero axis, and its rms value is 2.72 A, which is much smaller than the neutral current of the load side iLN (44.8 A rms). Compared with Fig. 12b, the neutral current of the grid side iSN (4.77 A rms) without MCA is larger than that with MCA.

The steady-state positive and negative DC bus voltages udc± are shown in Fig. 11g. It should be noted that the neutral current of the load side flows into the neutral point of the positive and negative DC capacitors Cdc±, and this will result in the DC bus voltage fluctuations. The fluctuation frequencies of the positive and negative DC bus voltages are 50 Hz, which coincides with the a-phase load current frequency, and the fluctuation frequency of the total DC bus voltage is twice the fundamental frequency. Compared with Fig. 12c, the positive and negative DC bus voltage fluctuations without the MCA are larger than those with the MCA because of the increased unbalanced degree of the grid currents.

The grid currents iSabc cannot immediately respond to the sudden change of a-phase load from empty-load to full-load in Fig. 11h, so a certain adjustment time is needed. During this adjustment time, the positive or negative DC bus capacitor provides energy for the a-phase load, and thus the total DC bus voltage udc experiences a large drop. Fig. 11i is an enlarged view of Fig. 11h. Compared with Fig. 12d, it can be seen that the DC bus voltage transient drop without MCA is much larger.

The experimental results in Fig. 12 also prove that there is a mutual influence between the DC bus voltage fluctuation and the neutral current of the grid side.

To verify the robustness of the UPQC based on the proposed MCA control strategy, the experimental results of the a-phase nonlinear load (diode bridge rectifier with a capacitive load) are added in this section, as shown in Fig. 13. The sine degree of the grid currents iSbac will be deteriorated, as shown in Fig. 13a, but the UPQC is still able to control iSbac to be balanced, and the rms values of iSabc are 7.06 A, 7.27 A and 7.07 A. The a-phase load voltage uLa appears to be distorted because of the influence of the a-phase nonlinear load, as shown in Fig. 13b. Figure 13c shows the three-phase load currents iLabc, where the a-phase load current iLa has the characteristics of periodic load and no-load. The a-phase of the parallel converter provides a part of the fundamental active current and all of the harmonic currents ipara for the nonlinear load. Meanwhile the b- and c-phase absorb the grid currents, as shown in Fig. 13d. The neutral current iSN is obviously smaller than the current iLN, as shown in Fig. 13e. The unbalanced grid currents and the larger neutral current of the load side will cause the fluctuations in the DC bus voltage, as shown in Fig. 13f.

5 Conclusion

Tackling the problem of three-phase grid currents imbalance caused by three-phase unbalanced loads, first the mathematical model of a three-phase four-wire UPQC is established. The mechanism of DC bus voltage fluctuations is analyzed in detail, and the mutual influence between the DC bus voltage fluctuations and the unbalanced grid currents is described. Then the control strategy based on the MCA is given under a three-phase stationary coordinate. The experimental results show that:

-

1)

The balance control of the grid currents with 100% unbalanced load can be realized by the given control strategy based on the proposed MCA;

-

2)

The neutral current of the grid side fluctuates in a small range around zero;

-

3)

The steady-state fluctuation and the transient drop of the DC bus voltage can also be restrained;

-

4)

The system has a greater robustness under the single-phase nonlinear load.

Therefore, the correctness of the theoretical analysis and the feasibility of the control strategy based on the MCA are verified. On the basis of the theoretical analysis, we believe this paper also draws important conclusions, which are of significance to related academic research as well as engineering.

References

Kasal GK, Singh B (2011) Voltage and frequency controllers for an asynchronous generator-based isolated wind energy conversion system. IEEE Trans Energy Convers 26(2):402–416

Halevidis CD, Koufakis EI (2013) Power flow in PME distribution systems during an open neutral condition. IEEE Trans Power Syst 28(2):1083–1092

Shi H, Zhuo F, Yi H et al (2016) Control strategy for microgrid under three-phase unbalance condition. J Mod Power Syst Clean Energy 4(1):94–102

Khadkikar V, Chandra A (2008) An independent control approach for three-phase four-wire shunt active filter based on three H-bridge topology under unbalanced load conditions. In: Proceedings of the IEEE power electronics specialists conference, Rhodes, Greece, 15–19 June 2008, pp 4643–4649

Khadkikar V, Chandra A, Singh B (2011) Digital signal processor implementation and performance evaluation of split capacitor, four-leg and three H-bridge-based three-phase four-wire shunt active filters. IET Power Electron 4(4):463–470

Kesler M, Ozdemir E (2010) A novel control method for unified power quality conditioner (UPQC) under non-ideal mains voltage and unbalanced load conditions. In: Proceedings of the twenty-fifth annual IEEE applied power electronics conference and exposition, Palm Springs, USA, 21–25 February 2010, pp 374–379

Zhang Y (2016) New control strategy for VSIG grid-side converter. In: Proceedings of the international symposium on computer, consumer and control, Xi’an, China, 4–6 July 2016, pp 108–111

Czarnecki LS, Haley PM (2015) Unbalanced power in four-wire systems and its reactive compensation. IEEE Trans Power Del 3(1):53–63

Agarwal R K, Hussain I,Singh B (2016) Integration of single-stage SPV generation to grid using admittance based LMS technique. In: Proceedings of the international conference emerging trends in electrical, electronics and sustainable energy systems, Sultanpur, India, 11–12 March 2016, pp 308–313

Modesto RA, Silva SAO, Oliveira AA et al (2016) A versatile unified power quality conditioner applied to three-phase four-wire distribution systems using a dual control strategy. IEEE Trans Power Electron 31(8):5503–5514

Santos RJM, Cunha JC, Mezaroba M (2014) A simplified control technique for a dual unified power quality conditioner. IEEE Trans Ind Electron 61(11):5851–5860

Silva SAO, Modesto RA, Barriviera R et al (2012) A line-interactive UPS system operating with sinusoidal voltage and current references obtained from a self-tuning filter. In: Proceedings of 38th annual conference on IEEE industrial electronics society, Quebec, Canada, 25–28 October 2012, pp 74–79

Modesto RA, Barriviera R, Silva SAO et al (2013) A simplified strategy used to control the output voltage and the input current of a single-phase line-interactive UPS system. In: Proceedings of 2013 Brazilian power electronics conference, Gramado, Brazil, 27–31 October 2013, pp 420–426

Shuai Z, Luo A, Shen J et al (2011) Double closed-loop control method for injection-type hybrid active power filter. IEEE Trans Power Electron 26(9):2393–2403

Gong W, Hu S, Shan M et al (2014) Robust current control design of a three phase voltage source converter. J Mod Power Syst Clean Energy 2(1):16–22

Chen Z, Chen Y, Guerrero JM et al (2016) Generalized coupling resonance modeling, analysis, and active damping of multi-parallel inverters in microgrid operating in grid-connected mode. J Mod Power Syst Clean Energy 4(1):63–75

Yang H, Ren S (2008) A practical series-shunt hybrid active power filter based on fundamental magnetic potential self-balance. IEEE Trans Power Del 23(4):2089–2096

Mulla MA, Rajagopalan C, Chowdhury A (2013) Hardware implementation of series hybrid active power filter using a novel control strategy based on generalised instantaneous power theory. IET Power Electron 6(3):592–600

Lenos H, Elias K, Frede B (2013) A new hybrid PLL for interconnecting renewable energy systems to the grid. IEEE Trans Ind Appl 49(6):2709–2719

Acknowledgements

This work was supported by National Natural Science Foundation of China (No. 51477148).

Author information

Authors and Affiliations

Corresponding author

Additional information

CrossCheck date: 27 December 2017

Rights and permissions

Open Access This article is distributed under the terms of the Creative Commons Attribution 4.0 International License (http://creativecommons.org/licenses/by/4.0/), which permits unrestricted use, distribution, and reproduction in any medium, provided you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made.

About this article

Cite this article

ZHAO, X., ZHANG, C., CHAI, X. et al. Balance control of grid currents for UPQC under unbalanced loads based on matching-ratio compensation algorithm. J. Mod. Power Syst. Clean Energy 6, 1319–1331 (2018). https://doi.org/10.1007/s40565-018-0383-7

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s40565-018-0383-7