Abstract

Linearity analysis of nanoscale devices is a vital issue as nonlinearity behavior is exhibited by them when employed in circuits for microwave and RF applications. In this work, a junctionless surrounded gate-graded channel MOSFET (JLSGGC MOSFET) is investigated thoroughly to analyze its linearity performance with the help of ATLAS tool of technology computer-aided design. The proposed device is compared systematically with the conventional junstionless surrounded gate MOSFET(JLSG MOSFET) to investigate their linearity. To evaluate the linearity, the figure of merits such as higher-order transconductance (Gm1, Gm2), intercept points(VIP2, VIP3, IIP3), IMD3 and 1 dB—compression point(P1 dB) are considered. The linearity of our proposed device improves by 35.5% in view of the compression point in comparison to JLSG MOSFET before the threshold voltage region of operation. The simulation results reveal a substantial enhancement in the linearity performance of the JLSGGC MOSFET. The improved linearity behavior of JLSGGC MOSFET makes it suitable for wireless RF and system-on-chip applications.Analog/RF performance is studied in terms of intrinsic gain (Gm/Gds), cut-off frequency (fT),maximum frequency of oscillation (fmax).Improved analog/RF performances of JLSGGC MOSFET suggests its applications in high frequency operating range.

Article Highlights

-

Linearity is an important issue that need to be resolved before employing the nano MOSFETs for high frequency radio applications.It is assessed through certain key factors which determine the level of distortion present in the said device. The key factor quantifies what should be the maximum input with in which the device should operate without reducing its gain by 1 decibel unit

-

The impact of graded channel architechure on the linearity of the proposed device is explored by comparing the key performance factors between graded and ungraded structures of junctionless surrounded gate MOSFETs

-

Systematic Comparison of gain , unity current gain frequency(fT) ,unity power gain frequency (fmax) are performed to find the suitability for anlog/RF applications of the JLSGGC MOSFET.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

The downscaled nano MOSFETs find their suitability for wireless and microwave applications. Short channel effects (SCEs) are the major hindrances in the path of further downscaling. Advanced MOS devices are proposed in the literature that minimizes SCEs up to a certain extent but still can’t be neglected. SOI MOSFETs [1], multi-gate MOSFETs [2], nanowires [3], and nanotube MOSFETs [4] are investigated to reduce SCEs and these structures are proved to be potential candidates for VLSI applications. SiGe Double gate MOSFET TFET with low doped drain region enhances the scaling capabilities and exhibits reduced susceptibility in comparison to conventional Si DG MOSFET [5]. The neural network-based hybrid approach is proposed to model graphene nanoribbon field-effect transistors (GNRFETs) which relaxes the computational burden substantially [6]. The requirement of steep S/D junction and parasitic resistance set obstacles in further downscaling which are overcome with the introduction of Junctionless MOSFETs [7, 8]. JL MOSFET is a uniformly doped gated resistor with a doping concentration of 1 × 1019 cm−3 or more than that. The advantageous features of junctionless devices, such as easy fabrication, channel homogeneity, and improved electrical characteristics, make them a promising option for enhancing the immunity performances of nano-scaled CMOS-based devices [9]. Device reliability and performance optimizations are two major concerns for the designing of advanced nano-scaled MOSFETs. The reduction in DIBL is more prominent due to the presence of a hot carrier in DG MOSFET as the channel length enters into the nanometer regime [10]. The immunity of JL DG MOSFET against hot carrier degradation is better than DG MOSFET [11]. By leveraging the benefits of junctionless DG MOSFETs, nanoelectronics digital applications can benefit from improved device immunity and reliability [11]. The mole fraction of Ge is explored in Si1-xGx/Ge/Si heterojunction (HJ) DG JL TFET to bring an improvement in sub-threshold characteristics and reduction in ambipolar conduction [12]. The investigation of the drain and source extension design in gate-all-around junctionless MOSFETs offers valuable insights into their electrical behavior for high-performance RF and analog applications [13]. The use of higher doping concentration in JL MOSFET results in mobility degradation and reduction of transconductance [14]. Lowering of transconductance restricts the use of JL MOSFET in analog/RF applications due to a reduction in cut-off frequency in comparison to traditional MOSFETs [15, 16]. As a matter of solution to improve RF performance, asymmetrical channel engineering has been proposed in past literature [17, 18]. The nanoscale graded channel gate stack double-gate (GCGS DG) MOSFET structure offers a promising solution for suppressing short-channel effects and improving subthreshold performance in MOSFETs for nanoelectronics applications [17]. The multi-objective optimization approach yields optimal subthreshold parameters for GCGSDG MOSFETs [18]. By iteratively evaluating and adjusting the subthreshold parameters using the genetic algorithm, significant improvements in threshold voltage, DIBL, subthreshold swing, and OFF-current are achieved [18]. Leakage current is reduced by the confinement of the electric field using gate engineering in the surrounding gate structure [19].To the best of our knowledge, improvement in analog and RF characteristics of DG JL MOSFET is put forward by Chen et al., implement asymmetric channel doping or nonuniform channel doping profile [20]. The results reveal the supremacy of graded channel DG JL MOSFET over traditional double gate JL MOSFET. Combining the advantage of surrounded gate architecture from gate engineering and graded channel architecture from channel engineering, here we put forward the proposal junctionless surrounded gate graded channel MOSFET (JLSGGC MOSFET).

Transistors have inherent nonlinearity within themselves. Nonlinearity in power amplifiers, continuous time alias filters, and LNAs leads to system performance degradation. The radio frequency performance of a system under investigation depends upon its linearity which in turn minimizes the inter-modulation terms and higher-order harmonics [21]. A higher level of linearity can be achieved in RF systems by designing sophisticated circuits which in turn reduces the nonlinearity from MOS devices up to a certain extent. However, linearization at the circuit level requires a larger IC area, more power consumption, and becomes costly. Linearity improvement is more appropriate at the device- level rather than at the system level as complex hardware circuitry is needed in system-level linearization [22, 23]. Hence linearity needs to be analysed precisely and comprehensively using physics-based device simulators. Many reports are available in the literature, focussing on the analog/RF analysis of graded channel (asymmetric channel) MOSFETs [24,25,26]. Linearity has not got much attention for surrounded gate JL MOSFET with asymmetric or graded channel architecture which is a potential candidate for VLSI applications and there still lies a gap. In this paper, we have investigated the linearity performance of surrounded gate junctionless MOSFET with graded channel architecture. Linearity performance is studied on a comparison basis with respect to the figure of merits (FOMs)such as higher-order transconductance (Gm2, Gm3), second and third-order intercept point (VIP2 and VIP3), third-order intermodal dispersion (IMD3), 1dBcompression point.

.The organization of the paper is mentioned as: Sect. 1 represents the reports from the literature concerning the state of the art. Section 2 describes the structural parameters of the device and the physical model used during simulation along with the model validation. Sections 3 and 4 illustrate the simulated results for linearity analysis between JLSGGC MOSFET and the conventional SGJL MOSFET. Finally, conclusion is drawn in Sect. 5.

2 Device structure and simulation setup

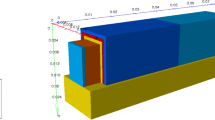

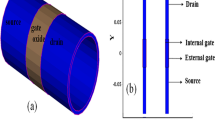

The conventional junctionless surrounded gate MOSFET is uniformly doped having an impurity concentration of 1019 cm−3. The doping concentration of JLSGGC MOSFET is the same as that of JLSG MOSFET. The channel of JLSGGC MOSFET is graded laterally along the direction of z. The device parameters and supply sources are selected for simulation according to ITRS [27]. Figures 1a and b depict the views of JLSGGC MOSFET in 3D and 2D. In the proposed device grading is done exactly in half the channel. The length of the channel(LG) is twice that of the graded channel length(Lgc). The radius (r) of the JLSGGC MOSFET is kept at 5 nm, hence the width (Tsi) is 10 nm. The length of Source/Drain extension (LS/D) and channel (LG) are kept at 20 nm and 30 nm respectively while performing the simulation.

In the proposed device the channel is graded exactly at half of its length. The channel length(LG) is twice that of the graded channel length(Lgc). The radius (r) and width (Tsi) of the nanowire JLGC MOSFET are kept at 5 nm and 10 nm respectively. Half of the region of the channel towards the source end of nanowire JLSGGC MOSFET is doped with 1 × 1019 cm−3 (Nd) and the rest of the channel towards the drain end is doped with 1.5 × 1019 cm−3 (Ngc). In the present work, simulation is carried out with ATLAS TCAD SILVACO three-dimensional device simulator [28]. Drift Diffusion and Boltzmann models are included during the simulation to consider the carrier transportation inside the semiconductor. Lombardi CVT model and FLDMOB models are used to consider carrier mobility. The Shockley Read Hall (SRH) physical model considers carrier lifetime before recombination during simulation. In nanoscaled devices, quantum effects become significant due to the reduced size and confinement of charge carriers, leading to unique quantum phenomena and properties. Moreover, when layer thickness approaches 7 nm or less, the de Broglie wavelength of the layer approaches that of a thermalized electron, and conventional energy–momentum relations for bulk semiconductors are no longer operational [29, 30]. Similarly, ballistic transport refers to the motion of charge carriers, such as electrons, through a material without experiencing scattering or collisions. In this transport, carriers travel freely, following classical physics principles, and their trajectories are not influenced by impurities, defects, or lattice vibrations. Ballistic transport is typically observed in ultra-small devices, where the device dimensions are comparable to the mean free path of the charge carriers [31]. The channel length and thickness of the present device are 30 nm and 10 nm respectively. The quantum and ballistic phenomenon come into play if the channel length and body thickness reduce below 20 nm and 7 nm respectively. The present model doesn’t include the quantum as well as ballistic transport mechanisms as (i) The size of the devices is more than de-Broglie wavelengths which leads to the beyond the realm of quantum effects [30]. (ii) The computed value of the mean free path (\(\lambda =\frac{1}{\pi {d}^{2}N})\) (where d is diameter and N is concentration) is not comparable to the dimensions of the proposed device, which causes the exclusion of the ballistic transport mechanism [31]. Complete depletion of the charge carrier during the off state of such a heavily doped device is ensured by using polysilicon as the gate metal having work function 5.0 eV. Differential equations are solved using the Gummel-Newton numerical method. The chosen models are validated by calibrating the simulated results against the experimental results of n-type junctionless nanowires [32]. The body thickness and channel length of the device are kept at 30 nm and 1 µm respectively which are the same as the experimental data. The simulation is done at VDS = 0.05 V. Figure 2 illustrates good agreement between the results obtained from simulation and experiment. Hence the chosen models are validated.

The design parameters of JLSGGC MOSFET are summarized in Table 1.

3 Transfer characteristics

The drain current for graded channel and ungraded channel MOSFETs are compared with respect to Vgs and illustrated in Fig. 3.

The charge carriers of both devices face different electric fields due to which there is a faster increase in the center potential of JLSGGC MOSFET than the traditional one [33]. A discontinuous electric field is marked in JLSGGC MOSFET having two peaks [33]. But junctionless surrounded gate MOSFET has one electric field peak. The additional electric field peak, created at the grading channel position, leads to the electric field diminution towards the drain. The reduced electric field accelerates the electrons while crossing the conducting channel. This improved transportation of electrons enhances the drain current in JLSGGC MOSFET.

Transconductance (Gm) is a major factor in considering linearity in the case of MOSFETs. Transconductance (Gm) represents the variation in drain current as per the change in Vgs. Figure 4 illustrates Gm as a function of Vgs for both of the devices.

The existence of an additional electric field peak due to channel grading redistributes the electric field at the drain. This is the cause of improved Gm in the proposed device.

4 Linearity analysis

In this section, a systematic comparison is made between the linearity performance of JLSGGC MOSFET and JLSG MOSFET with the performance indices like second and third-order incept points(VIP2, VIP3), intermodal dispersion (IMD3), input intercept point (IIP3), 1-dB compression point(P1-dB). Linearity has a direct and inverse relationship with first and higher-order transconductances [34]. A MOSFET is a nonlinear time-variant system that modulates the AC input i,e (Vgs) and thereby produces the current ID. ID can be represented as a Taylor series expansion and the coefficients of this expansion are given by [35]:

The 2nd and 3rd order transconductance terms cause nonlinearity in the device. The variable intercept points are interpreted as the extrapolated gate voltage amplitude at which the harmonics of the 2nd and 3rd order will be the same as the fundamental tone in drain current ID. The values of intercept points should be high to obtain higher linearity and lower distortion. The variable intercept points are formulated as: [36]

The peaks of Gm2 and Gm3 for both of the devices are obtained at lower voltages of Vgs as demonstrated by Fig. 5a and b. This result shows the utilization of the devices in the circuits operated in moderately inverted regions. Both (a) and (b) of Fig. 5 clarify that JLSGGC MOSFET possesses more linearity in terms of suppressing higher-order inter-modulation terms by achieving lower peaks of Gm2 and Gm3.

It is evident from Figs. 6 and 7 that JLSGGC MOSFET attains higher peaks of VIP2 and VIP3 as compared to JLSG MOSFET. The reason for this is the discontinuous electric field that redistributes itself towards the drain side and carriers transport more efficiently.

The distortion due to inter-modulation terms in the output of the RF stage is measured by third-order inter-modulation term i.e. IMD3. To achieve linearity in the proposed MOSFET, the IMD3 should be minimal. The expression for IMD3 is as follows [37]

Usually, Rs is 50 Ω for radio frequency applications.. As depicted in Fig. 7 JLSGGC MOSFET is said to have a value of IMD3 ranging from − 79 dBm to 0dBm whereas JLSG MOSFET posses IMD3 ranging from − 93 dBm to 0dBm from VGS = 0.0 V to VGS = 0.4. The more negative the value of IMD3, the more will be the distortion because distortion is regarded as a loss. Hence JLSGGC MOSFET shows less distortion in comparison to JLSG MOSFET suggesting improved linearity. But from VGS = 0.4 V to VGS = 0.7, JLSGGC MOSFET attains a higher value of IMD3 as compared to JLSG MOSFET showing degradation in linearity performance. Hence SJLGC MOSFET can be chosen to be a potential candidate for low-power analog applications during the lower value of VGS possessing lower distortion [37, 38]

It is Gm3 which is mostly responsible for generating intermodulation terms i.e. amplitude of the main signal is distorted along with the amplitudes of sideband signals. In advanced RF communication systems, 3rd order intermodulation intercept point (IIP3) is considered a major source for nonlinear systems and devices.

The IIP3 is expressed as: [38]

Figure 9. shows that IIP3 for the JLSGGC MOSFET is more than the traditional one, suggesting better suppression of intermodulation terms in NWJL MOSFET. The linearity of the device is assessed through higher variable and inter-modulation intercept points [39].

The 1-dB compression point (P1dB) of an RF power amplifier refers to that point where the gain of the amplifier reduces by 1 dB. This point indicates the amount of RF input power needed to ensure a loss of 1 dB. The highest allowable input power to the RF mixer is obtained from this point.

1 dB compression point is expressed as: [38]

P1 dB represents the level of output power at which there is a fall in gain by 1 dB from its saturated constant value. It is desirable to operate the amplifiers below the P1dB point. The higher value of 1-dB compression point results in lower distortion and reduced inter-channel interference so that RF and Microwave systems can operate linearly. Our proposed devices possess better linearity than the traditional counterpart as they achieve higher P1dB than JLSG MOSFET as noticeable in Fig. 10. In graded channel architecture there is an increase in carrier transportation towards the drain end due to reduced electric field [33]. Although both of the devices have surrounded gate structures the impact of gate controllability in JLSGGC MOSFET is more in focusing the electrons in the channel towards the drain end owing to their higher transportation efficiency. This results in a higher Id, hence the transconductance. Higher Gm leads to an improved 1 dB compression point. The results discussed above are summarized in Table 2 for a comparative study.

Apart from linearity analysis, analog/RF performance figure of merits (FOMs) such as intrinsic gain, cut-off frequency, maximum frequency of oscillation are investigated for the proposed device.

Intrinsic gain is the highest possible voltage gain of the transistor amplifier irrespective of the biasing point.It is one of the figure of merits (FOMs) to access the analog circuits. Intrinsic gain is the ratio of the transconductance (Gm) to output conductance (Gds). Figure 11 depicts the comparison of intrinsic gain in between JLSG and JLSGGC MOSFETs.

Our proposed device posses higher gain as compared to the conventional one as evident from Fig. 11. The reason for this is the higher transconductance (Gm) and lower output conductance (Gds) exhibited by JLSGGC MOSFET. The lowering of Gds in the proposed device is due to the discontinuity in electric field along the channel where it is graded. The higher doping region of the channel absorbs additional Vds and doesn’t allow the punch through to occure. This is known as screening effect due to which Gds reduces in JLSGGC Mosfet [40].

The cut-off frequency (fT) is that frequency of an amplifier where short circuit current gain is one.It has significance in evaluating the radio frequency performance of RF amplifier.The analytical formula for fT is given by: [34, 37, 38]

In Eq. (8), Cgg is the intrinsic inter electrode gate to gate capacitance. The comparison of fT is illustrated in Fig. 12. The volume of inversion charges reduces towards the source end due to discontinuous electric field in the graded channel structure. Vgs gradually looses its control towards the source end to invert the charges. As a result, JLSGGC MOSFET posses lower Cgg than JLSG MOSFET. Cut off frequency is more in JLSGGC MOSFET because of increased Gm and decreased Cgg in the device.

The upper limit of frequency for successful operation of RF amplifiers are quantified by fmax.It is the frequency at which power gain is unity. The expression for fmax is given by:[34, 37, 38]

In Eq. (9), Rg, Cgd,Gds are the gate resistance, gate to drain capacitance, drain to source conductance respectively. fmax varies exactly in the same way as fT w.r.t Vgs as shown in Fig. 13. The maximum frequency of oscillation is more in JLSGGC MOSFET than JLSG MOSFET. This is because the increase in parasitic drain to source capacitance is compensated by decrease in Gds in the proposed device.

Table 3 represents a comparison of performance indexes between the proposed device and one comparable device (laterally graded with double gate junctionless architechture)reported in literature.The surrounded gate structure brings improvement in JLSGGC MOSFET as shown in Table 3.This comparision reveals that our proposed device is a befitting candidate for VLSI and RF applications.

5 Conclusion

The impact of a non-uniformly doped channel (graded channel) on the linearity performance of nanowire junctionless graded channel MOSFET is investigated in this paper. The existence of an additional electric field peak at the location where the channel is graded leads to the enhancement of on-state current. Thus the transportation capability of charge carriers is enhanced 35.53% improvement in the 1- dB compression point for our proposed device, suggesting its more linearity in comparison to comparison to JLSG MOSFET in the subthreshold region.Higher value of intrinsic gain of JLSGGC MOSFET in the sub threshold region is best suitable for its low power switching applications.The proposed device can be a better choice to operate in wide range of RF spectrum because of its higher cut-off frequency and maximum frequency of oscillation. This paper demonstrates that a compromise is required according to the utilization of the novel MOSFET in various areas. The present paper paves the path to new additional inquiries for the proposed device from its application area.

Data availability

The authors confirm that the data supporting the findings of this study are available within the article or below mentioned references.

References

Balestra F, Christoloveanu S, Benachir M, Brini J, Elewa T (1987) Double gate silicon-on-insulator transistor with volume inversion : a new device with greatly enhanced performance. IEEE Electron Device Lett 8(9):410. https://doi.org/10.1109/EDL.1987.26677

Hisamoto D, Lee WC, Kedzierski J et al (2000) Fin FET – a self –aligned double gate MOSFET scalable to 20nm, IEEE Trans. Electron Devices 47(12):2320. https://doi.org/10.1109/16.887014

Cui Y, Zhong Z, Wang D, Wang W et al (2003) High performance silicon nanowire field effect transistors. Nano Lett 3(2):149. https://doi.org/10.1021/nl025875l

Tekleab D (2014) Device performance of silicon nanotube field effect transistor. IEEE Electron Device Lett. https://doi.org/10.1109/LED.2014.2310175

Bentrcia T, Djeffal F, Ferhati H, Dibi Z (2020) A comparative study on scaling capabilities of Si and SiGe nanoscale double gate tunneling FETs. SILICON 12(4):945–953. https://doi.org/10.1007/s12633-019-00190-w

Tamersit K, Djeffal F (2019) A computationally efficient hybrid approach based on artificial neural networks and the wavelet transform for quantum simulations of graphene nanoribbon FETs. J Comput Electron 18(3):813–825. https://doi.org/10.1007/s10825-019-01350-2

Wong HSP (2011) Beyond the conventional MOSFET. In:Proceeding of 31th European Solid State Device Research Conference, p.69. https://doi.org/10.1109/ESSDERC.2001.195206

Lee CW, Borne A, Ferain I et al (2010) High Temperature performance of silicon junctionless MOSFETs. IEEE Trans Electron Devices 57(3):620. https://doi.org/10.1109/TED.2009.2039093

Cho S, Park SH, Park B G, et al. (2011) Sillicon -compatible bulk-type compound junctionless field-effect transistor . In Proc.(ISDRS).

Ghoggali Z, Djeffal F (2010) Analytical analysis of nanoscale fully depleted Double-Gate MOSFETs including the hot-carrier degradation effects. Int J Electron 97(2):119–127. https://doi.org/10.1080/00207210902894746

Chebaki E, Djeffal F, Bentrcia T (2012) Two-dimensional numerical analysis of nanoscale junctionless and conventional double gate MOSFETs including the effect of interfacial traps. Physica Status Solidi 9(10–11):2041–2044. https://doi.org/10.1002/pssc.201200128

Ferhati H, Djeffal F, Bentrcia T (2018) The role of the Ge mole fraction in improving the performance of a nanoscale junctionless tunneling FET: concept and scaling capability. Beilstein J Nanotechnol 9(1):1856–1862. https://doi.org/10.1016/j.spmi.2015.09.041

Djeffal F, Ferhati H, Bentrcia T (2016) Improved analog and RF performances of gate-all-around junctionless MOSFET with drain and source extensions. Superlattices Microstruct 90:132–140. https://doi.org/10.1007/s10825-019-01350-2

Colinge JP, Kranti A, Yan R et al (2011) Junctionless nanowire transistor (JNT): properties and design guidelines. Solid 65–66:33. https://doi.org/10.1016/j.sse.2011.06.004

Cho S, Kim KR, Park BG, Kang IM (2011) RF performance and small signal parameter extraction of junctionless silicon nano wire MOSFETs. IEEE Trans Electron Devices 58(8):2511. https://doi.org/10.1109/TED.2011.2109724

Doria RL, Pavanello MA, Trevisoli RD et al (2011) Junctionless multiple – gate transistors for analog applications. IEEE Trans Electron Devices 58(8):2511–2519

Djeffal F, Meguellati M, Benhaya A (2009) A two-dimensional analytical analysis of subthreshold behavior to study the scaling capability of nanoscale graded channel gate stack DG MOSFETs. Physica E 41(10):1872–1877. https://doi.org/10.1016/j.physe.2009.08.002

Bendib T, Djeffal F, Arar D (2011) Subthreshold behavior optimization of nanoscale graded channel gate stack double gate (GCGSDG) MOSFET using multi-objective genetic algorithms. J Comput Electron 10:210–215. https://doi.org/10.1007/s10825-011-0349-8

Amoroso SM, Compagnoni CM, Mauri A et al (2011) Semi-analytical model for the transient operation of gate-all-around charge-trap memories IEEE. Trans Electron Devices 58(9):3116. https://doi.org/10.1109/TED.2011.2159010

Chen Y, Mohamad M, Jo M et al (2013) Junctionless MOSFETs with laterally graded-doping channel for analog/ RF applications. J Comput Electron 12(4):757. https://doi.org/10.1007/s10825-013-0478-3

Kang S, Choi B, Kim B (2002) Linearity analysis of CMOS for RF applications. IEEE RFIC Symp Dig. https://doi.org/10.1109/TMTT.2003.808709

Ma W, Kaya S (2004) Impact of device physics on DG and SOI MOSFET linearity. Solid-State Electron 48(10–11):1741. https://doi.org/10.1016/j.sse.2004.05.008

Nandi A, Saxena AK, Dasgupta S (2012) Impact of dual –K spacer on analog performance of underlap FinFET. Microelectron J 43(11):883

Rao SS, Joseph RDB, Chintala VD, Saramekala GK, Srikar D, Rao NB (2022) Analog/RF performance of triple material gate stack-graded channel double gate-junctionless strained-silicon MOSFET with fixed charges. Silicon. https://doi.org/10.1007/s12633-021-01462-0

Ashima, Dhandapani, V. and Raj, B., 2021. Performance analysis of charge plasma induced graded channel Si nanotube. Journal Of Engineering Research, 9, pp.146–154. https://doi.org/10.36909/jer.EMSME.13843

Roy S, Mukherjee S, Dutta A, Kumar Sarkar C, Bose C (2019) Circuit performance analysis of graded doping of channel of DGMOS with high-k gate stack for analogue and digital application. IET Circuits Devices Syst 13(3):337–343. https://doi.org/10.1049/iet-cds.2018.5199

Semiconductor Industry Association ,International Tehnology Roadmap for semiconductors, SIA San Jose,2011.

SILVACO Int.SantaClara,CA ,ATLAS 3D DEVICE Simulator,2012

Jaiswal N ,Kranti A .A model for underlap-dependent short-channel Effects in junctionless MOSFET.IEEE Trans.on Device, 2018,65(3) ,2018. . https://doi.org/10.1109/TED.2018.2796602

Huang JZ, Chew WC, Tang M, Jiang L (2011) Efficient simulation and analysis of quantum ballistic transport in nanodevices with AWE. IEEE Trans Electron Devices 59(2):468–476. https://doi.org/10.1109/TED.2011.2176130

Fang J, Chen S, Vandenberghe WG, Fischetti MV (2017) Theoretical study of ballistic transport in silicon nanowire and graphene nanoribbon field-effect transistors using empirical pseudopotentials. IEEE Trans Electron Devices 64(6):2758–2764. https://doi.org/10.1109/TED.2017.2695960

Colinge JP, Lee CW, Afzalian A et al (2010) Nanowire transistors without junctions. Nat Nanotechnol 5:225. https://doi.org/10.1038/nnano.2010.15

Misra S, Biswal SM, Baral B, Swain SK, Pati SK (2021) Study of analog/Rf and stability investigation of surrounded gate junctionless graded channel MOSFET (SJLGC MOSFET). Silicon. https://doi.org/10.21203/rs.3.rs-2757963/v1

Biswal SM, Baral B, De D et al (2016) Study of effect of gate length downscaling on the analog/RF performance and linearity investigation of InAs based nanowire tunnel FET. Superlattice Microstruct 91:319. https://doi.org/10.1016/j.spmi.2016.01.021

Kang S, Choi B, Kim B (2003) Linearity analysis of CMOS for RF application. IEEE Trans Microw Theory Tech 51(3):972. https://doi.org/10.1109/TMTT.2003.808709

Gautam R, Saxena M, Gupta RS et al (2012) Effect of localized charges on nanoscale cylindrical surrounding gate MOSFET: analog performance and linearity analysis. Microelectron Reliab 52(6):989. https://doi.org/10.1016/j.microrel.2011.12.014

Baral B, Biswal SM et al (2017) Radio frequency/analog and linearity performance of a junctionless double gate metal-oxide-semiconductor field effect transistor. SAGE Publ 93(11):985. https://doi.org/10.21203/rs.3.rs-621755/v1

Biswas K, Sarkar A, Sarkar CK (2015) Impact of barrier thickness on analog, RF and linearity performance of nanoscale DG heterostructure MOSFET. Superlattices Microstruct MOSFET 86:95. https://doi.org/10.1016/j.spmi.2015.06.047

Kaya S, Ma W (2004) Optimization of RF linearity in DG-MOSFETs. IEEE Electron Device Lett 25(5):308–310. https://doi.org/10.1109/LED.2004.826539

Chaudhry A, Kumar MJ et al (2004) Investigation of novel attributes of a fully depleted dual-material gate SOI MOSFET. IEEE Trans Electron Devices 51(9):1463. https://doi.org/10.1109/TED.2004.833961

Acknowledgements

The authors would like to thank Electronics &Communication Engineering, Silicon Institute of Technology, Bhubaneswar, for their support in using TCAD simulator to carry out this simulation.

Funding

The authors declare that no funds, grants, or other support were received during the preparation of this manuscript.

Author information

Authors and Affiliations

Contributions

Sarita Misra, Sudhansu Mohan Biswal-[Conceptualization, methodology] Sudhansu Mohan Biswal, Sarita Misra- [simulation] Biswajit Baral, Sudhansu Kumar Pati—[investigation, reviewing and editing, overall correction].

Corresponding author

Ethics declarations

Conflict of interest

The authors declared there is no conflict of interest in this work.

Consent for publication

The authors gave consent for publication as per the journal standard.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Misra, S., Biswal, S.M., Baral, B. et al. Investigation of graded channel effect on analog/linearity parameter analysis of junctionless surrounded gate graded channel MOSFET. SN Appl. Sci. 5, 384 (2023). https://doi.org/10.1007/s42452-023-05473-x

Received:

Accepted:

Published:

DOI: https://doi.org/10.1007/s42452-023-05473-x