Abstract

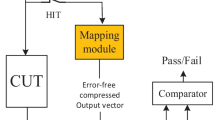

Although several synthesis methods for asynchronous circuits exist, only limited test methodologies have been developed. This paper presents a built-in self-test (BIST) architecture for Multi-Threshold NULL Convention Logic (MTNCL) asynchronous circuits that utilizes an automated, industry-standard tool-based flow. The software procedure for, and hardware components to implement, BIST functionality are explained. To improve testing performance, the MTNCL pipeline is separated into multiple parallel BIST circuits, with standard pipeline components doubling as BIST circuitry to reduce area overhead. Results of this BIST architecture and software performance is explored for three different test cases looking at area impact and effects of varying the number of input patterns and initial seeds. Further refinements to fault exclusions based upon operating principles of MTNCL are developed to better depict actual fault coverage; and additional hardware modifications are proposed to improve controllability and observability to further increase fault coverage.

Similar content being viewed by others

Data Availability

Data sharing not applicable to this article as no datasets were generated or analyzed during the current study.

References

Fant KM, Brandt SA (1996) NULL Convention Logic: A Complete and Consistent Logic for Asynchronous Digital Circuit Synthesis. Proc Int Conf Appl Specific Syst Architect Process 261–273

Zhou L, Parameswaran R, Parsan F, Smith SC, Di J (2015) Multi-Threshold NULL Convention Logic (MTNCL): An Ultra-Low Power Asynchronous Circuit Design Methodology. J Low Power Electron Appl 5(2):81–100

Reese RB, Smith SC, Thornton MA (2012) Uncle - An RTL Approach to Asynchronous Design. Proc IEEE Int Symp Asynchronous Circuits Syst 65–72

Parsan F, Smith SC, Al-Assadi WK (2016) Design for Testability of Sleep Convention Logic. IEEE Transactions on VLSI Systems 24(2):743–753

Nemati N, Beckett P, Reed MC, Fant K (2018) Clock-less DFT-less Test Strategy for Null Convention Logic. IEEE Trans Emerg Top Comput 6(4):460–473

Nemati N, Reed MC, Fant K, Beckett P (2016) Asynchronous Interleaved Scan Architecture for On-line Built-in Self-test of Null Convention Logic. Proc IEEE Int Symp Circuits Syst 746–749

Sparkman B, Smith SC, Di J (2020) Built-In Self-Test for Multi-Threshold NULL Convention Logic Asynchronous Circuits. Proc IEEE VLSI Test Symp 1–6

Smith SC, Di J (2009) Designing Asynchronous Circuits using NULL Convention Logic (NCL). Synthesis Lectures on Digital Circuits and Systems, Morgan & Claypool Publishers, Vol. 4/1

Nagle HT, Roy SC, Hawkins CF, McNamer MG, Fritzemeier RR (1989) Design for Testability and Built-In Self Test: A Review. IEEE Trans Industr Electron 36(2):129–140

Fišer P. Collection of Digital Design Benchmarks. Czech Technical University in Prague, [Online]. Available: https://ddd.fit.cvut.cz/www/prj/Benchmarks/. Accessed June 2022

Wang LT, McCluskey EJ (1987) Built-in self-test for sequential machines. Proc Int Test Conf 334–341

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

Competing Interests

The authors have no relevant financial or non-financial interests to disclose.

List of Differences

The work presented in this paper is a continuation of our previous work, titled “Built-In Self-Test for Multi-Threshold NULL Convention Logic Asynchronous Circuits,” which was published in the 2020 IEEE VLSI Test Symposium [7]. Our previous work implemented the entire MTNCL DUT as a single BIST stage, while this paper partitions the DUT, such that each MTNCL pipeline stage is its own BIST stage, in order to parallelize BIST operation. The method proposed herein not only decreases test time, but also allows for fault calculation of MTNCL circuits with data feedback, which was not possible in our previous work. Additional new contributions include development of fault exclusion rules, based upon MTNCL circuit operating principles, to better depict actual fault coverage, and hardware for increasing controllability and observability, in order to increase fault coverage. We estimate that this paper consists of approximately 50% new material compared to our VTS paper, which is well above the minimum requirement of 30% new material.

Additional information

Responsible Editor: V. D. Agrawal

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Sparkman, B., Smith, S.C. & Di, J. Built-In Self-Test for Multi-Threshold NULL Convention Logic Asynchronous Circuits using Pipeline Stage Parallelism. J Electron Test 38, 321–334 (2022). https://doi.org/10.1007/s10836-022-06007-w

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10836-022-06007-w