Abstract

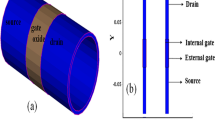

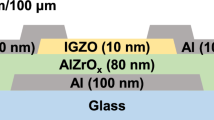

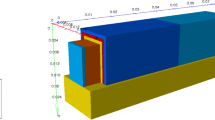

This work deals with the novel characterization of n + SiGe δ-doped layer with the combination of gate stacking method in Vertical TFET device by using TCAD simulation tool. The vertical structure will enhance the device’s scalability because of vertical electron tunneling for vertical electrical field. Therefore, higher ON state current offers due to parallel movement of charge carriers to the gate electric field. The introduction to the optimized n + Si0.2Ge0.8 δ-doped layer will further reduce the off-state leakage current and enhance device performance because it minimizes the tunneling bandwidth between the source and channel junction. Triple metal gate is introduced to mitigate the unwanted ambipolar conduction and optimized the work function at tunneling gate, control gate and auxiliary gate with the value of 4.15 eV, 4.3 eV and 4.15 eV. Four of the different combinations have been discussed and compared with and without presence of the gate stack and n + δ-doped layer. The reported data reveals that among all different structures, the existence of gate staking method and SiGe δ-doped layer will show the 40% improvement with existing simulations. A high current ratio of the order (~1013), with substantially benchmarking results of steeper subthreshold slope (9.75 mV/decade), is achieved. The simulation results conclude the n + δ-doped TMG vertical TFET as a sustainable candidate for ultralow-power applications.

Similar content being viewed by others

References

Koswatta SO, Lundstrom MS, Nikonov DE (2009) Performance comparison between pin tunneling transistors and conventional MOSFETs. IEEE Trans Electron Devices 56(3):456–465. https://doi.org/10.1109/TED.2008.2011934

Kim S, Choi WY (2017) Improved compact model for double-gate tunnel field-effect transistors by the rigorous consideration of gate fringing field. Japanese J Appl Phys 56.8:084301

Choi WY, Park B-G, Lee JD, Liu T-JK (2007) Tunneling field-effect transistors (TFETs) with subthreshold swing (SS) less than 60 mV/dec. IEEE Electron Device Letters 28(8):743–745. https://doi.org/10.1109/LED.2007.901273

Yasin Khatami, Kaustav Banerjee, “Steep Subthreshold Slope n- and p-Type Tunnel-FET Devices for Low-Power and Energy- Efficient Digital Circuits,” IEEE Trans Electron Devices, VOL. 56, NO. 11, pp.2752–2760, DOI:https://doi.org/10.1109/TED.2009.2030831, 2009

Krishnamohan T, Kim D, Raghunathan S, and Saraswat K (2008) Double-Gate Strained-Ge Heterostructure Tunneling FET (TFET) With record high drive currents and≪ 60mV/dec subthreshold slope. In 2008 IEEE International Electron Devices Meeting, pp. 1–3. IEEE. DOI: https://doi.org/10.1109/IEDM.2008.4796839

Ko E, Lee H, Park J-D, Shin C (2016) Vertical tunnel FET: design optimization with triple metal-gate layers. IEEE Trans Electron Devices 63(12):5030–5035

Singh S, Raj B (2018) Vertical tunnel-fet analysis for excessive low power digital applications. In 2018 First International Conference on Secure Cyber Computing and Communication (ICSCCC), pp. 192–197. IEEE

Toh E-H, Wang GH, Samudra G, Yeo Y-C (2007) Device physics and design of double-gate tunneling field-effect transistor by silicon film thickness optimization. Appl Phys Lett 90(26):263507

Avci UE, Morris DH, Young IA (2015) Tunnel field-effect transistors: prospects and challenges. IEEE J Electron Devices Soc 3(3):88–95

Bhushan B (2012) Kaushik Nayak, and V. Ramgopal Rao. "DC compact model for SOI tunnel field-effect transistors.". IEEE Trans Electron Devices 59(10):2635–2642

Pal A, Dutta AK (2016) Analytical drain current modeling of double-gate tunnel field-effect transistors. IEEE Trans Electron Devices 63(8):3213–3221

Verhulst AS, Vandenberghe WG, Maex K, De Gendt S, Heyns MM, Groeseneken G (2008) Complementary silicon-based heterostructure tunnel-FETs with high tunnel rates. IEEE Electron Device Lett 29(12):1398–1401

Lee MJ, Choi WY (2012) Effects of device geometry on hetero-gate-dielectric tunneling field-effect transistors. IEEE Electron Device Lett 33(10):1459–1461

Raad B, Nigam K, Sharma D, Kondekar P (2016) Dielectric and work function engineered TFET for ambipolar suppression and RF performance enhancement. Electron Lett 52(9):770–772

Sant S, Schenk A (May 2015) Band-offset engineering for GeSn-SiGeSn hetero tunnel FETs and the role of strain. IEEE J Electron Devices Soc 3(3):164–175. https://doi.org/10.1109/JEDS.2015.2390971

Sun M-C, Kim SW, Kim G, Kim HW, Lee J-H, Shin H, Park B-G (2010) Scalable embedded Ge-junction vertical-channel tunneling field-effect transistor for low-voltage operation. In 2010 IEEE Nanotechnology Materials and Devices Conference, pp. 286–290. IEEE. doi: https://doi.org/10.1109/NMDC.2010.5652410

Toh E-H et al (2008) Device physics and design of germanium tunneling field-effect transistor with source and drain engineering for low power and high performance applications. J Appl Phys 103.10:104504

Rooyackers R, Vandooren A, Verhulst AS, Walke AM, Simoen E, Devriendt K, Lo-Corotondo S et al (2014) Ge-source vertical tunnel FETs using a novel replacement-source integration scheme. IEEE Trans Electron Devices 61(12):4032–4039

Boucart K, Ionescu AM (2007) Double-gate tunnel FET with high-$\kappa $ gate dielectric. IEEE Trans Electron Devices 54(7):1725–1733. https://doi.org/10.1109/TED.2007.899389

Singh S, Raj B (2019) Design and analysis of a heterojunction vertical t-shaped tunnel field effect transistor. J Electron Mater 48(10):6253–6260

Venkatesh M, Balamurugan NB (2020) Influence of threshold voltage performance analysis on dual halo gate stacked triple material dual gate TFET for ultra low power applications. Silicon:1–13

Venkatesh M, Balamurugan NB (2019) New subthreshold performance analysis of germanium based dual halo gate stacked triple material surrounding gate tunnel field effect transistor. Superlattice Microst 130:485–498

Badgujjar S, et al (2019) Design and Analysis of Dual Source Vertical Tunnel Field Effect Transistor for High Performance. Trans Electric Electronic Mater: 1–9. https://doi.org/10.1007/s42341-019-00154-2

Singh S, Raj B (2021) Analytical and compact modeling analysis of a SiGe hetero-material vertical L-shaped TFET. Silicon: 1–11

Singh S, Raj B (2020) Modeling and simulation analysis of SiGe heterojunction double gate vertical t-shaped tunnel FET. Superlattice Microst 142:106496

Vanlalawpuia K, Bhowmick B (2019) Investigation of a Ge-source vertical TFET with delta-doped layer. IEEE Trans Electron Devices 66(10):4439–4445

Wadhwa G, Singh J (2020) Implementation of linearly modulated work function A σ B 1− σ gate electrode and Si 0.55 Ge 0.45 N+ pocket doping for performance improvement in gate stack vertical-TFET. Appl Phys A 126(11):1–11

TCAD Atlas User's Manual, SILVACO r interna- tional (2018)

Nigam K, Kondekar P, Sharma D (2016) High frequency performance of dual metal gate vertical tunnel field effect transistor based on work function engineering. Micro Nano Lett 11(6):319–322

Singh S, Raj B (2020) Analysis of ONOFIC technique using SiGe heterojunction double gate vertical TFET for low power applications. Silicon 12:1–10

Singh S, Raj B (2020) Two-dimensional analytical modeling of the surface potential and drain current of a double-gate vertical t-shaped tunnel field-effect transistor. J Comput Electron 19(3):1154–1163

Kane EO (Jun. 1961) Theory of tunneling. J Appl Phys 32(1):83–91

Keldysh LV (1958) Behavior of non-metallic crystals in strong electric fields. Soviet J Exp Theoretic Phys 6:763

Mushtaq U, Solay LR, Amin SI, Anand S (2019) Design and Analog performance analysis of triple material gate based doping-less tunnel field effect transistor. J Nanoelectronics Optoelectron 14(8):1177–1182

Mushtaq U, Kumar N, Anand S, Amin I (2020) Design and performance analysis of core-shell dual metal-dual gate cylindrical GAA silicon nanotube-TFET. Silicon 12(10):2355–2363

Boucart K, Ionescu AM (2007) Threshold voltage in tunnel FETs: physical definition, extraction, scaling and impact on IC design." In ESSDERC 2007-37th European Solid State Device Research Conference, pp. 299–302. IEEE

Singh S, Raj B (2020) Analytical modelling and simulation of Si-Ge hetero-junction dual material gate vertical T-shaped tunnel FET. Silicon 12:1–12

Acknowledgements

The authors are greatful to Dr. Subodh Wariya, IET, Lucknow for their support during the research.

Availability of Data and Materials

Not Applicable.

Funding

The author(s) received no financial support for the research, authorship, and/or publication of this article.

Author information

Authors and Affiliations

Contributions

Shilpi Gupta: Validation, Writing and Editing, conceptualization,Simulation, TCAD Software, Writing- Original draft preparation, Investigation.

Subodh Wairya: Revision and Supervision.

Shailendra Singh: Logical-Methodology, Data curation, Reviewing.

Corresponding author

Ethics declarations

Ethics Approval and Consent to Participate

Not Applicable.

Consent for Publication

Not Applicable.

Competing Interests

Not Applicable.

Disclosure of Potential Conflicts of Interest

No conflicts to report.

Research Involving Human Participants and/or Animals

Not applicable.

Informed Consent

Not applicable.

Additional information

Publisher’s Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Gupta, S., Wairya, S. & Singh, S. Design and Analysis of Triple Metal Vertical TFET Gate Stacked with N-Type SiGe Delta-Doped Layer. Silicon 14, 4217–4225 (2022). https://doi.org/10.1007/s12633-021-01211-3

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s12633-021-01211-3