Abstract

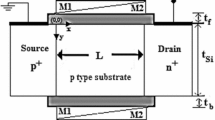

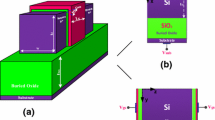

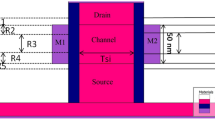

We present a two-dimensional (2-D) analytical modeling of the surface potential of a double-gate vertical t-shaped tunnel field-effect transistor (TFET), considering the inherit dual modulation effect in such devices. This effect explains the control of the surface potential by both bias voltages, which are used to calculate the tunneling depletion width at the source and drain junctions. A model of the tunneling current in the device is derived based on the surface-potential model. The parabolic approximation is used to solve the 2-D Poisson equation with appropriate boundary conditions. The dependence of the surface potential profile on different parameters is analyzed by varying the gate–source potential, drain–source potential, gate oxide dielectric constant, gate metal work function, and different materials used. Finally, expressions for the surface potential of the channel along with the tunneling current are obtained, accurately capturing their variation with the gate and drain biases. The proposed method is verified by the agreement between its analytical results and technology computer-aided design (TCAD) simulation results.

Similar content being viewed by others

References

Koswatta, S.O., Lundstrom, M.S., Nikonov, D.E.: Performance comparison between pin tunneling transistors and conventional MOSFETs. IEEE Trans. Electron Devices 56(3), 456–465 (2009). https://doi.org/10.1109/TED.2008.2011934

Kim, S., Choi, W.Y.: Improved compact model for double-gate tunnel field-effect transistors by the rigorous consideration of gate fringing field. Jpn. J. Appl. Phys. 56(8), 084301 (2017)

Choi, W.Y., Park, B.-G., Lee, J.D., Liu, T.-J.K.: Tunneling field-effect transistors (TFETs) with subthreshold swing (SS) less than 60 mV/dec. IEEE Electron Device Lett. 28(8), 743–745 (2007). https://doi.org/10.1109/LED.2007.901273

Khatami, Y., Banerjee, K.: Steep subthreshold slope n- and p-type tunnel-FET devices for low-power and energy-efficient digital circuits. IEEE Trans. Electron Dev. 56(11), 2752–2760 (2009). https://doi.org/10.1109/TED.2009.2030831

Krishnamohan, T., Kim, D., Raghunathan, S., Saraswat, K: Double-gate strained-Ge heterostructure tunneling FET (TFET) with record high drive currents and 60 mV/dec subthreshold slope. In: 2008 IEEE International Electron Devices Meeting, pp. 1–3. IEEE (2008). https://doi.org/10.1109/iedm.2008.4796839

Sun, M.-C., Kim, S.W., Kim, G., Kim, H.W., Lee, J.-H., Shin, H., Park, B.-G.: Scalable embedded Ge-junction vertical-channel tunneling field-effect transistor for low-voltage operation. In: 2010 IEEE Nanotechnology Materials and Devices Conference, pp. 286–290. IEEE (2010). https://doi.org/10.1109/nmdc.2010.5652410

Toh, E.-H., et al.: Device physics and design of germanium tunneling field-effect transistor with source and drain engineering for low power and high performance applications. J. Appl. Phys. 103(10), 104504 (2008)

Vandenberghe, W.G., et al.: Analytical model for a tunnel field-effect transistor. In: MELECON 2008—The 14th IEEE Mediterranean Electrotechnical Conference. IEEE (2008). https://doi.org/10.1109/melcon.2008.4618555

Boucart, K., Ionescu, A.M.: Double-gate tunnel FET with high-κ gate dielectric. IEEE Trans. Electron Devices 54(7), 1725–1733 (2007). https://doi.org/10.1109/TED.2007.899389

Nigam, K., Kondekar, P., Sharma, D.: High frequency performance of dual metal gate vertical tunnel field effect transistor based on work function engineering. Micro Nano Lett. 11(6), 319–322 (2016). https://doi.org/10.1049/mnl.2015.0526

Sant, S., Schenk, A.: Band-offset engineering for GeSn–SiGeSn hetero tunnel FETs and the role of strain. IEEE J. Electron Devices Soc. 3(3), 164–175 (2015). https://doi.org/10.1109/JEDS.2015.2390971

Singh, S., Vishvakarma, S.K., Raj, B.: Analytical modeling of split-gate junction-less transistor for a biosensor application. Sens. Bio-Sens. 18, 31–36 (2018). https://doi.org/10.1016/j.sbsr.2018.02.001

Badgujjar, S., et al.: Design and analysis of dual source vertical tunnel field effect transistor for high performance. Trans. Electr. Electron. Mater. 6, 5–6 (2019). https://doi.org/10.1007/s42341-019-00154-2

Wang, P.-Y., Tsui, B.-Y.: Band engineering to improve average subthreshold swing by suppressing low electric field band-to-band tunneling with epitaxial tunnel layer tunnel FET structure. IEEE Trans. Nanotechnol. 15(1), 74–79 (2016). https://doi.org/10.1109/TNANO.2015.2501829

Dubey, P.K., Kaushik, B.K.: T-shaped III–V heterojunction tunneling field-effect transistor. IEEE Trans. Electron Devices 6(8), 3120–3125 (2017). https://doi.org/10.1109/TED.2017.2715853

Chen, S., Liu, H., Wang, S., Li, W., Wang, X., Zhao, L.: Analog/RF performance of T-shape gate dual-source tunnel field-effect transistor. Nanoscale Res. Lett. 13(1), 321 (2018). https://doi.org/10.1186/s11671-018-2723-y

Kumar, S., Raj, B.: Simulations and modeling of TFET for low power design. In: Chapter no. 21 in the Book Titled “Handbook of Research on Computational Simulation and Modeling in Engineering”, pp. 650–679. IGI Global, USA (2015). https://doi.org/10.4018/978-1-4666-8823-0.ch021

Kumar, S., Raj, B.: Compact channel potential analytical modeling of DG-TFET based on evanescent-mode approach. J. Comput. Electron. 14(3), 820–827 (2015). https://doi.org/10.1007/s10825-015-0718-9

Samuel, A.T.S., Balamurugan, N.B., Bhuvaneswari, S., Sharmila, D., Padmapriya, K.: Analytical modelling and simulation of single-gate SOI TFET for low-power applications. Int. J. Electron. 101(6), 779–788 (2014). https://doi.org/10.1080/00207217.2013.796544

Nayfeh, O.M., Hoyt, J.L., Antoniadis, D.A.: Strained-Si1−xGex/Si band-to-band tunneling transistors: impact of tunnel-junction germanium composition and doping concentration on switching behavior. IEEE Tran. Electron Devices 56(10), 2264–2269 (2009). https://doi.org/10.1109/TED.2009.2028055

Lee, M.J., Choi, W.Y.: Analytical model of single-gate silicon-on-insulator (SOI) tunneling field-effect transistors (TFETs). Solid-State Electron. 63(1), 110–114 (2011). https://doi.org/10.1016/j.sse.2011.05.008

Wu, C., et al.: An analytical surface potential model accounting for the dual-modulation effects in tunnel FETs. IEEE Trans. Electron Devices 61(8), 2690–2696 (2014). https://doi.org/10.1109/TED.2014.2329372

Sentaurus User’s Manual, Synopsys, Inc., Mountain View (2017)

Prabhat, V., Dutta, A.K.: Analytical surface potential and drain current models of dual-metal-gate double-gate tunnel-FETs. IEEE Trans. Electron Devices 63(5), 2190–2196 (2016). https://doi.org/10.1109/TED.2016.2541181

Semiconductor Industry Association (SIA), International Technology Roadmap for Semiconductors (ITRS) (2015)

Bagga, N., Dasgupta, S.: Surface potential and drain current analytical model of gate all around triple metal TFET. IEEE Trans. Electron Devices 64(2), 606–613 (2017). https://doi.org/10.1109/TED.2016.2642165

Gholizadeh, M., Hosseini, S.E.: A 2-D analytical model for double-gate tunnel FETs. IEEE Trans. Electron Devices 61(5), 1494–1500 (2014)

Pandey, P., Vishnoi, R., Kumar, M.J.: A full-range dual material gate tunnel field effect transistor drain current model considering both source and drain depletion region band-to-band tunneling. J. Comput. Electron. 14(1), 280–287 (2015). https://doi.org/10.1007/s10825-014-0649-x

Zhang, L., He, J., Chan, M.: A compact model for double-gate tunneling field-effect-transistors and its implications on circuit behaviors. In: 2012 International Electron Devices Meeting. IEEE (2012). https://doi.org/10.1109/iedm.2012.6478994

Kane, E.O.: Theory of tunneling. J. Appl. Phys. 32(1), 83–91 (1961)

Acknowledgements

The authors thank the VLSI design group of NIT Jalandhar for their interest in this work and useful comments that led to the final form of this paper. The support of DST-SERB Project ECR/2017/000922 is gratefully acknowledged. The authors also thank NIT Jalandhar for the laboratory facilities and research environment to carry out this work.

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher’s Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Singh, S., Raj, B. Two-dimensional analytical modeling of the surface potential and drain current of a double-gate vertical t-shaped tunnel field-effect transistor. J Comput Electron 19, 1154–1163 (2020). https://doi.org/10.1007/s10825-020-01496-4

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10825-020-01496-4