Abstract

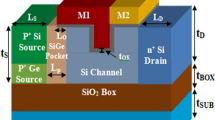

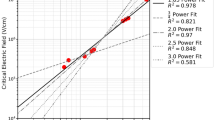

In this paper, a heterojunction vertical t-shaped tunnel field effect transistor (V-tTFET) is proposed, and the scaling issue associated with it is investigated using Sentaurus Technology computer-aided design simulation. This device is basically a gated P-I-N diode. It is made up of silicon material with dual gate control over the channel based on a band-to-band tunneling mechanism. Furthermore, a silicon-germanium (SiGe) layer is introduced to the channel which results in an aggressive improvement in the input characteristics of the device. The testified results of the device with respect to threshold voltage (VT), subthreshold slope and the current ratio (Ion/Ioff) emerges efficiently with the values of 0.253 V, 31.05 mV/decade and 1012 for a 60-nm channel length with a 10-nm SiGe layer. A lower bandgap material in the source region and higher bandgap material in the drain region also improves the input characteristics of the device. It is also demonstrated that scaling the gate oxide thickness (tox) enhances the device characteristics. Moreover, ON-state current increases exponentially by taking the high value of the dielectric constant (k) for the oxide material. Furthermore, the (p++) source doping concentration of the V-tTFET lies between 1018 to 1020 cm−3 which makes the tunneling easier at the source-channel junction to achieve high Ion/Ioff. The vertical tunnel FET has a distribution of the source channel drain in the vertical direction, which enhances the scalability of the simulated device.

Similar content being viewed by others

References

S. Sharma, B. Raj, and M. Khosla, J. VLSI Des. Tools Technol. (JoVDTT) 6, 19 (2016).

A. Jain, S. Sharma, and B. Raj, Int. J. Eng. Sci. Technol. 19, 1864 (2016).

S. Singh, S.K. Vishvakarma, and B. Raj, Sens. Biosens. Elsevier 18, 31 (2018).

W.Y. Choi, B.G. Park, J.D. Lee, and T.J.K. Liu, IEEE Electron Dev. Lett. 28, 743 (2007).

J. Zhi, Z. Yiqi, L. Cong, W. Ping, and L. Yuqi, J. Semicond. 37, 094003 (2016).

S. Brocard, M.G. Pala, and D. Esseni, in IEDM (2013).

Pei-Yu Wang and B.-Y. Tsui, IEEE Trans. Nanotechnol. 15, 74 (2016).

P.K. Dubey and B.K. Kaushik, IEEE Trans. Electron Dev. 64, 3120 (2017).

F. Chen, H. Ilatikhameneh, Y. Tan, G. Klimeck, and R. Rahman, IEEE Trans. Electron Dev. 65, 3065 (2018).

G. Wadhwa and B. Raj, IEEE Sens. J. 18, 6048 (2018).

S. Kumar and B. Raj, J. Comput. Electron. 14, 820 (2015).

S. Kumar and B. Raj, J. Nanoelectron. Optoelectron. 11, 323 (2016).

M.C. Sun, S.W. Kim, G. Kim, H.W. Kim, J.H. Lee, H. Shin, and B.G. Park, in Nanotechnology Materials and Devices Conference (NMDC), p. 2264 (2010).

O.M. Nayfeh, J.L. Hoyt, and D.A. Antoniadis, IEEE Trans. Electron Dev. 56, 2264 (2009).

Y. Khatami and K. Banerjee, IEEE Trans. Electron Dev. 56, 2752 (2009).

H. Lee, J.-D. Park, and C. Shin, IEEE Trans. Electron Dev. 63, 2016 (1827).

Z. Ahangari, Micro Nano Lett. 13, 1165 (2018).

S. Brocard,, M.G. Pala, and D. Esseni, in Electron Devices Meeting (IEDM), p. 5 (2013).

K.K. Bhuwalka, J. Schulze, and I. Eisele, IEEE Trans. Electron Dev. 52, 909 (2005).

Y. Kamata, Y. Kamimuta, T. Ino, and A. Nishiyama, Jpn. J. Appl. Phys. 44, 2323 (2005).

K.K. Bhuwalka, S. Sedlmaier, A.K. Ludsteck, C. Tolksdorf, J. Schulze, and I. Eisele, IEEE Trans. Electron Dev. 51, 279 (2004).

W. Wang, IEEE Trans. Electron Dev. 61, 193 (2014).

Sentaurus User’s Manual, Synopsys 09 (2017).

Semiconductor Industry Association (SIA), in International Technology Roadmap for Semiconductors (ITRS) (2015).

D.W. Kwon, H.W. Kim, J.H. Kim, E. Park, J. Lee, W. Kim, S. Kim, J.H. Lee, and B.G. Park, IEEE Trans. Electron Dev. 64, 1799 (2017).

S. Sant and A. Schenk, IEEE J. Electron Dev. Soc. 3, 164 (2015).

S. Kumar and B. Raj, in Handbook of Research on Computational Simulation and Modeling in Engineering, IGI Global, p. 640 (2016).

J. Wu and Y. Taur, IEEE Trans. Electron Dev. 63, 3342 (2016).

Acknowledgments

We thank the VLSI design group of NIT Jalandhar for their interest in this work and useful comments to draft the final form of the paper. The support of DST-SERB Project (ECR/2017/000922) is gratefully acknowledged. We would like to thank NIT Jalandhar for lab facilities and research environment to carry out this work.

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Singh, S., Raj, B. Design and Analysis of a Heterojunction Vertical t-Shaped Tunnel Field Effect Transistor. J. Electron. Mater. 48, 6253–6260 (2019). https://doi.org/10.1007/s11664-019-07412-2

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11664-019-07412-2