Abstract

Neuron models exist in different levels of complexity and biological modeling depth. The Hindmarsh–Rose model offers a rich repertoire of neuronal dynamics while being moderately mathematically complex. Existing circuit realizations of this neuron model, however, require a large amount of operational amplifiers due to the model’s quadratic and cubic nonlinearity. In contrast to hardware realizations of simpler neuron models, this leads to a higher power consumption. In this work, the Hindmarsh–Rose model is approximated by an ideal electrical circuit that relies mostly on passive circuit elements and thus reduces the power consumption. For this purpose, we analyze the power flows of an equivalent electrical circuit of the Hindmarsh–Rose model and replace several nonlinear circuit elements by constant ones. Moreover, we approximate the cubic nonlinearity by three memristors in combination with a negative impedance converter. This negative impedance converter represents the only active circuit element required for the complete circuit, leading to an increased energy efficiency compared to the existing circuit realizations. Simulations verify the circuit’s ability to generate spiking and bursting dynamics comparable to the original Hindmarsh–Rose model.

Graphic abstract

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

In recent years, the notion of energy efficiency has permeated everyday life as well as science. For cognitive tasks, for instance, such an energy-efficient aspect can be realized via hardware implementations of neuronal networks. Then, a key ingredient is the neuronal model that inspires the hardware realization. Mathematical neuroscience has proposed a large number of different model classes that vary in terms of their level of complexity and implementation effort. To summarize only the most prominent ones, the Hodgkin–Huxley [1, 2] and the Morris–Lecar models [3,4,5,6] are strongly linked to biology in a close correspondence of dynamical variables and model parameters to physiological quantities. Furthermore, a simple, but well-established model is the integrate-and-fire model, which is still biologically inspired, but mathematically simplified. Several variations have been proposed, even recently [7,8,9,10]. Inbetween these two levels of mathematical approximation are the more abstract models such as the Izhikevich [11,12,13] and the Hindmarsh–Rose model [14,15,16]. In this work, we consider the Hindmarsh–Rose model because of its mathematical complexity that is significantly lower than the Hodgkin–Huxley model, but still exhibits a large amount of different neuronal dynamics, including bursting or spiking. Moreover, in contrast to, e.g., the Izhikevich model, which comes with a discontinuous reset, the Hindmarsh–Rose model is stated in terms of continuous differential equations, favoring a circuit implementation.

Existing circuit realizations of the Hindmarsh–Rose model are usually either based on field programmable gate arrays (FPGAs) [17] or integrator circuits [18, 19]. Here, one of the main challenges lies in realizing the cubic and quadratic nonlinearity of the Hindmarsh–Rose model, which has, for instance, been realized by multipliers [18, 20]. Multiplierless approaches have been recently proposed, e.g., in [21,22,23]. In contrast to this, an equivalent electrical circuit of the Hindmarsh–Rose model has been reported in [24] that only requires a negative impedance converter (NIC) as an active component. While this circuit is promising in terms of low-power consumption, it exhibits several highly nonlinear circuit elements that are difficult to realize without leading to high implementation costs. Our aim in this work is to simplify the equivalent circuit of [24] while still maintaining the generation of spiking and bursting behaviors, the major functionalities of the Hindmarsh–Rose model. For this purpose, we first analyze the power flows of the nonlinear circuit elements of the equivalent circuit to replace them by simpler, implementable passive circuit elements; cf. [25]. Second, we deploy memristor models based on devices with a filament-based bipolar switching [26] to approximate the cubic nonlinearity. Since the considered memristor models account for passive circuit elements, this results in a lower power consumption and, thus, an increased energy efficiency compared to operational-amplifier-based hardware realizations. Memristors are, in general, a very promising circuit element, especially in the context of neuromorphic engineering. This is especially because they can be used for synapse realizations [27, 28]. However, memristors are also used for neuron models. For instance, the differential equation for the slow current of the Hindmarsh–Rose model has been modified to account for memristors [16, 29, 30], while in [31,32,33], Hindmarsh–Rose models with an additional fourth memristor-based differential equation have been considered. In contrast to these approaches, in this work, we approximate the original Hindmarsh–Rose model with a memristor-based circuit.

The remainder of this work is structured as follows: In Sect. 2, we briefly summarize the original Hindmarsh–Rose model and the equivalent circuit presented in Ref. [24]. The latter serves as the basis for the circuit simplification discussed in Sect. 3. We verify the circuit’s ability to generate spiking and bursting behaviors by LTspice simulations in Sect. 4. We finish with some conclusions in Sect. 5.

2 Original Hindmarsh–Rose model

2.1 Hindmarsh–Rose model

The original Hindmarsh–Rose model is given by the following set of differential equations [14]:

where the dynamical variables \(z_1\), \(z_2\), and \(z_3\) denote the membrane potential, a fast current, and a slow current, respectively. \(a, b, c, d, \epsilon ,\) and s are positive constants, \(\varphi \) is the resting potential, and k represents the externally applied current. The parameter b together with k can be used to switch between bursting and spiking behavior; see [15, 16].

2.2 Equivalent electrical circuit

In [24], an equivalent electrical circuit for the Hindmarsh–Rose model has been proposed. We briefly recapitulate this circuit in this sequel, since it serves as the starting point for the desired model simplification. The equivalent circuit can be described by

with the circuit elements given by

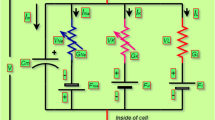

Here, \(U_0=1\,\textrm{V}, I_0 = 1\,\textrm{mA}, R_0 = 1\,\mathrm {k\Omega }\), and \(L_0 = 1\,\mu \textrm{H}\) are normalization constants, \(f(u_1)\) is a smooth \(\textrm{signum}\)-function, which can be realized as a \(\textrm{tanh}\)-function, and \(\varepsilon = 10^{-3}\) ensures that the denominators of the inductance and resistance functions do not become zero. As proposed in [24], the smooth \(\textrm{signum}\)-function can be implemented using a voltage-controlled switch in combination with an NIC inverting the current, as illustrated in Fig. 1. Note that in contrast to [24], we have not split \(G_1(u_1)\) into its quadratic and linear term, because we approximate the combined terms as discussed in Sect. 3. The complete circuit then consists of a capacitor, inductor, resistor, current source, and voltage source, as well as a nonlinear inductor, a nonlinear resistor, a controlled voltage source, an NIC, and a switch. For more information on the equivalent circuit and its derivation, the interested reader is referred to [24].

3 Circuit simplification

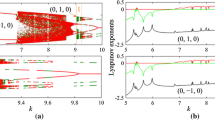

Power flow of \(R_2(u_1)\) (top), change of stored energy of \(L_{2}(u_1)\) (top center), power of \(e_2(u_1)\) (bottom center), and total energy consumption (bottom) for a spiking (a) and a bursting behavior (b). Note that some of the plotted signals exceed the vertical axis limits. We have cut off those signals for the sake of clarity

3.1 Power-flow analysis

The equivalent circuit of Fig. 1 consists of several nonlinear circuit elements, which are difficult to implement in practice. This is especially true for \(L_2(u_1)\) and \(R_2(u_1)\). In particular, from a circuit-theoretic point of view, both \(L_2(u_1)\) and \(R_2(u_1)\) are not well defined, since they are controlled by a voltage not present at their own respective port. As a result, this leads to high implementation costs in a hardware realization. For this reason, we aim for a simplification of the resistive and inductive part of the second differential equation [Eq. (1b)] while still maintaining a comparable spiking and bursting behavior. We additionally consider a simplification of \(e_2(u_1)\), because it is governed by a similar nonlinearity. Again, this simplification should preserve the major functionality of the Hindmarsh–Rose model, that is, the generation of comparable spiking and bursting dynamics. To this end, we investigate the respective power flows as well as the energy consumption of the complete circuit for a spiking and bursting behavior, as shown in Fig. 2a and b. The power flows and the energy consumption can be calculated via

The results have been obtained by solving Eq. (2) with a standard ODE solver in Matlab. The utilized parameters are given in Table 1.

Let us first consider the total energy consumption of the circuit depicted in the bottom of Fig. 2. This shows that one spike during a spiking activity leads to an energy consumption of \(0.13\,\textrm{nJ}\). During one burst, \(0.12\,\textrm{nJ}\) energy is consumed, while in the quiescence phase between bursts, \(2.48\,\textrm{nJ}\) energy is consumed. Hence, while a burst and a spike during regular spiking consumes similar energy, most energy is consumed in the non-active state of the neuron circuit during a bursting behavior.

Concerning the power flows, several high power spikes and high spikes for the change of stored energy can be seen for \(R_2(u_1)\), \(e_2(u_1)\), and \(L_2(u_1)\). These spikes occur when \(u_1\) gets close to zero, since in this case, \(R_2(u_1)\), \(L_2(u_1)\), and \(e_2(u_1)\) become maximal. These power spikes are extremely narrow, because for the parameter set utilized in this work, \(u_1\) is only a transition point and not an equilibrium; see, e.g., [24]. Hence, the influence of these spikes on the overall power flow and thus on the functionality of the circuit is negligible. This in turn indicates that the nonlinearities of \(R_2(u_1)\), \(L_2(u_1)\), and \(e_2(u_1)\) themselves are negligible, cf. [25], since they are directly linked to the occurring power spikes. Hence, we choose \(L_2\), \(R_2\), and \(e_2\) constant by leaving out their dependency on \(u_1\). To sum up, the linear circuit elements now read

3.2 Memristive switch

The voltage-controlled switch together with the NIC used in the circuit of Fig. 1 implements the smooth \(\textrm{signum}\)-function \(f(u_1)\). Typically, the switch switches very fast between two positions. For a technical implementation, this could be problematic, as it can lead to peak currents and hence damage the inductor. For this purpose, we replace the switch by memristors that enable a slower switching process. Their design is based on the following main idea: Overall, the switch should allow for changing the polarity of the current \(i_2\) by alternating between two current paths. In particular, the path containing the NIC inverts the current \(i_2\), while the path with the short circuit passes on the non-inverted current. This switching between the two paths requires the currently active path to become highly conductive relative to the inactive path. As such, this behavior can be realized by two complementary switching memristors. In this work, we use memristor models inspired by filament-based memristors with a bipolar switching; see, e.g., [26]. Such memristors can be described by

where \(u_{\textrm{s}\pm } = u_\textrm{s}\) for \(W_\textrm{sa}\) and \(u_{\textrm{s}\pm } = -u_\textrm{s}\) for \(W_\textrm{sb}\). \(z_\textrm{s}\) is the state variable, \(W_{\textrm{s} 1}\) is the high conductance state, and \(W_{\textrm{s} 0}\) is the low conductance state. \(\sigma (\cdot )\) is the Heaviside function with

\(U_{\textrm{p,s}}\) and \(U_{\textrm{n,s}}\) are the positive and negative threshold voltages, respectively, and \(S_{\textrm{p,s}}\) and \(S_{\textrm{n,s}}\) are the slopes for an increasing and decreasing state variable, respectively.

We use two of these memristors to implement the desired switching behavior, as depicted in Fig. 3. In contrast to the switch proposed in [24], the memristive switch is not controlled by the voltage \(u_1\) but rather by its own voltage \(u_\textrm{s}\), as this leads to well-defined circuit elements. Moreover, the memristive switch adds an additional resistive term to the second differential equation [Eq. (2b)]. This can be seen when evaluating the mesh and node rules of Fig. 3. As a result, the new circuit is an approximation of the originally equivalent electrical circuit of the Hindmarsh–Rose model.

To keep this approximation as close as possible to the equivalent circuit, the choice of the memristor parameters is important. First, it should hold that \(\frac{1}{W_\textrm{s0}}<< R_2\). This way, the voltage drop at the memristive switch is small compared to the voltage present at the series interconnection of \(L_2\), \(R_2\), and \(e_2\), and thus alters the original circuit’s dynamics only marginally. Second, \(W_{\textrm{s} 1}\) should be significantly larger than \(W_{\textrm{s} 0}\), such that the memristive switch switches between the two current paths given by the NIC and the short circuit. Third, the threshold voltages \(U_{\textrm{p,s}}\) and \(U_{\textrm{n,s}}\) should be close to \(0\,\textrm{V}\), so that the switching occurs every time the voltage \(u_\textrm{s}\) changes its polarity. Finally, the slopes should enable a complete switching from the low to the high conductance state and vice versa for the time period by which the voltage \(u_\textrm{s}\) retains its polarity.

3.3 Memristive approximation of \(G_1(u_1)\)

The conductance \(G_1(u_1)\) stems from the cubic nonlinearity of the original Hindmarsh–Rose model in Eq. (1a). Together with the quadratic nonlinearity in Eq. 1b, an implementation of this nonlinearity for electrical circuits has been extensively dealt with in recent literature; see, e.g., [22, 23]. However, while some approaches have managed to mitigate the use of multipliers and have hence reduced the implementation cost, a larger amount of operational amplifiers and transistors is still necessary. For this reason, in this work, we take an alternative approach by approximating \(G_1(u_1)\) by memristors, such that the only active component required for the complete circuit is the NIC.

Inspired by [22], where the cubic nonlinearity has been fitted by three parametrized \(\textrm{tanh}\)-functions and an additional constant, we split \(G_1(u_1)\) into three parts that can be fitted by \(\left[ 1+\textrm{tanh}\right] \)-terms. In general, \(\textrm{tanh}\)-functions as well as \(\left[ 1+\textrm{tanh}\right] \)-terms can be realized in different ways, where one solution approach is the use of transistors [22, 34]. Moreover, a \(\left[ 1+\textrm{tanh}\right] \)-term is similar to an activation function for neuron models and neuronal networks, and can be realized, for instance, by memristors in combination with operational amplifiers [35]. However, since we aim for a purely memristive solution, we first consider the \(\left[ 1+\textrm{tanh}\right] \)-terms to be nonlinear conductances and replace them with memristor models later.

In contrast to pure \(\textrm{tanh}\)-terms, this results in non-negative conductance definitions that can be implemented by nonlinear resistors. The approximation for \(G_1(u_1)\) then yields

where \(G_\textrm{n1}\), \(G_\textrm{n2}\), and \(G_\textrm{n3}\) are the maximum conductance values, \(U_\textrm{th,1}\), \(U_\textrm{th,2}\), and \(U_\textrm{th,3}\) are the threshold voltages, and \(U_\textrm{n,1}\), \(U_\textrm{n,2}\), and \(U_\textrm{n,3}\) determine the slopes of the \(\tanh \)-functions. Note that every term \(g_\mathrm {n\mu }, \mu =1,2,3\), represents a single conductance, such that, in total, three nonlinear conductances are required to implement \(G_1(u_1)\). This leads to one conductance switching between \(0\,\textrm{S}\) and \(-G_\textrm{n2}\), indicating an active component. However, since we already exploit an NIC, which can also enable negative conductances, we can implement the desired conductance without requiring an additional active component by placing a non-negative conductance at the port of the NIC.

Fitting \(G_1(u_1)\) by three nonlinear conductances based on \(\left[ 1+\textrm{tanh}\right] \)-terms, with \(u_\textrm{min}=-1.5\,\textrm{V}\), \(u_\textrm{max}=2\,\textrm{V}\), \(G_\textrm{min}=-1.4\,\textrm{mS}\), and \(G_\textrm{max}=0.6\,\textrm{mS}\). (a) Comparison between \(G_1(u_1)\) and the complete fitting result and (b) comparison of \(G_1(u_1)\) and the individual nonlinear conductances \(g_\textrm{n1}(u_1), g_\textrm{n2}(u_1)\), and \(g_\textrm{n3}(u_1)\)

The results of this fitting procedure are illustrated in Fig. 4 and the corresponding parameters are shown in Table 2.

Figure 4b shows the three parts of \(G_1(u_1)\) being fitted by \(g_\textrm{n1}(u_1)\), \(g_\textrm{n2}(u_1)\), and \(g_\textrm{n3}(u_1)\), highlighted by the shaded areas. These parts cover the operation range of the Hindmarsh–Rose model for the parameters given in Table 1. As can be seen from Fig. 4a, the combined nonlinear conductances fit \(G_1(u_1)\) well within the operation range. A small deviation can be seen at \(0\,\textrm{V}\), which is caused by both \(g_\textrm{n1}(u_1)\) and \(g_\textrm{n2}(u_1)\) entering regions where they become nearly constant; see Fig. 4b.

The overall behavior of the nonlinear conductances \(g_\textrm{n1}(u_1), g_\textrm{n2}(u_1)\), and \(g_\textrm{n3}(u_1)\) is to switch between \(0\,\textrm{S}\) and their maximum conductance values. This switching behavior can be approximated by filament-based memristors with a bipolar switching, although deviations between the memristive solution and the nonlinear conductances are to be expected due to the threshold-based switching of the memristors. Similar to the memristive switch, the utilized memristor models yield

Here, \(u_{1\pm } = u_1\) for \(W_\textrm{n2}\) and \(W_\textrm{n3}\) and \(u_{1\pm } = -u_1\) for \(W_\textrm{n1}\). \(z_\mathrm {n\mu }\) is the state variable, \(W_{\textrm{n} \mu 1}\) is the high conductance state, and \(W_{\textrm{n}\mu 0}\) is the low conductance state. \(U_{\textrm{p,n},\mu }\) is the positive threshold voltage, \(U_{\mathrm {n,\textrm{n}\mu }}\) is the negative threshold voltage, and \(S_{\textrm{p,n}\mu }\) and \(S_{\textrm{n,n}\mu }\) are the slopes for an increasing and decreasing state variable, respectively.

\(G_1(u_1)\) depends on the bifurcation parameter b and is an important factor for the dynamic behavior of the original Hindmarsh–Rose model. The choice of the memristive parameters approximating this conductance thus strongly influences the exhibited dynamic behavior of the simplified circuit. In general, the low conductance states \(W_{\textrm{n} \mu 0}\) are freely selectable as long as \(W_{\textrm{n} \mu 0} \ll 1\,\textrm{mS}\) is satisfied. The high conductance states should be chosen similar to \(G_\textrm{n1}\), \(G_\textrm{n2}\), and \(G_\textrm{n3}\) from Eq. (7). All negative threshold voltages \(U_{\textrm{n,n}\mu }\) should be close to \(0\,\textrm{V}\). This is the closest approximation of \(g_\textrm{n1}(u_1)\), \(g_\textrm{n2}(u_1)\), and \(g_\textrm{n3}(u_1)\) from Fig. 4, which start switching even before the voltage \(u_1\) becomes negative. Concerning the positive threshold voltages, \(U_{\textrm{p,n}\mu 1}\) should also be close to \(0\,\textrm{V}\), as this is again the closest approximation of \(G_\textrm{n1}(u_1)\) from Fig. 4. \(U_{\textrm{p,n}\mu 2}\) and \(U_{\textrm{p,n}\mu 3}\) should be chosen similar to \(U_\textrm{th,2}\) and \(U_\textrm{th,3}\) from Eq. (7), respectively. Finally, the slopes \(S_{\textrm{p}\mu }\) and \(S_{\textrm{n}\mu }\) should enable a complete switching from the low to the high conductance state and vice versa for the time period by which the voltage \(u_1\) does not change its polarity.

Replacing the nonlinear conductance \(G_1(u_1)\) by the three memristors \(W_{\textrm{n}1}, W_{\textrm{n}2}\), and \(W_{\textrm{n}3}\) as depicted in Fig. 5, the simplified Hindmarsh–Rose circuit is now governed by

with \(\nu \in [a,b]\) and \(\mu \in [1,2,3]\).

4 Simulation results

In this section, we discuss numerical results based on LTspice simulations of the circuit shown in Fig. 5 to verify the simplified circuit’s ability to generate a bursting and spiking behavior. For this purpose, we implement the NIC by a controlled voltage and current source, as illustrated in Fig. 6. For a practical circuit implementation, the NIC can, for instance, be realized by operational amplifiers [36, 37] or current conveyors [38]; cf. [24]. Memristors are modeled by implementing each equation by a controlled voltage source.

We also simulate the model from Sect. 3.1 (cf. Fig. 3) with an ODE solver in Matlab to investigate the intermediate modeling steps. To compare the results to the equivalent circuit of the original Hindmarsh–Rose model, we further simulate Eq. (2). The parameters used for the memristors of the simplified circuit are given in Table 3.

Simulation results are shown in Fig. 7, which depicts the time series of \(u_1\) next to the corresponding trajectory in the three-dimensional phase space.

Before exploring the bursting regime, we first consider the spiking behavior. In Fig. 7a, the original model generates eight spikes and exhibits a spike-frequency adaption. In contrast to this, the models from Sects. 3.1 and 3.2 generate four and six spikes, respectively, but show a long-lasting first spike instead of a spike-frequency adaption. The model from Sect. 3.3, however, again shows a spike-frequency adaption while generating seven spikes. It should also be noted that the input current has been drastically increased for all modified models from \(j_1 = 2.5\,\textrm{mA}\) to \(j_1 = 9\,\textrm{mA}\). This shows that the neglected nonlinearity of the original circuit elements and the associated power spikes are compensated by a larger input current. Additionally, it can be seen that the spike shape changes for the models of Sects. 3.2 and 3.3. In particular, the spikes now exhibit a distinct hyperpolarization phase, which can be interpreted as a behavior close to biology.

Observing the phase-space trajectories in Fig. 7b, two groups can be seen. The first group contains the original model and the model from Sect. 3.1, which show a similar limit cycle, but differ in terms of their transient approach to the limit cycle. The second group contains the model from Sects. 3.2 and 3.3 and show a similar, yet differently shaped limit cycle. Overall, there are two different limit cycles for the four models, with one model per limit cycle showing a spike-frequency adaption in the transient phase.

The membrane potentials (a, c) and the state trajectories (b, d) for a spiking (left) and bursting behavior (right). Depicted are the results of the original Hindmarsh–Rose model (top row), the model from Sect. 3.1 (second row from the top), the model from Sect. 3.2 (second row from the bottom), and the model from Sect. 3.3 (bottom row). The utilized parameters for the spiking are \(k_\textrm{S} = 9\), \(k_\textrm{S} = 9\), and \(k_\textrm{S} = 7.5\) for the results of Sect. 3.1, Sect. 3.2, and Sect. 3.3, respectively. Concerning the bursting behavior, \(k_\textrm{B}\) is chosen to \(k_\textrm{B} = 9\), \(k_\textrm{B} = 7.5\), and \(k_\textrm{B} = 7\) for the results of Sect. 3.1, Sect. 3.2, and Sect. 3.3, respectively

The bursting behavior is depicted in Fig. 7c. While each models generates bursts consisting of three spikes, the original model exhibits two bursts, the model from Sect. 3.1 shows five bursts, and the models from Sects. 3.2 and 3.3 show three bursts. It is likely that the linearized circuit elements cause the increase of the burst frequency, as this increase can already be observed from the model of Sect. 3.1. This is also supported by the fact that the input current is again raised once the linearized circuit elements are introduced. Similar to the the spiking behavior, it can be observed that the models from Sects. 3.2 and 3.3 exhibit a clearly visible depolarization phase. Additionally, another intraburst spike starts at the end of a burst, but is strongly damped when the quiescence phase begins. As this first appears for the model of Sect. 3.2, this is probably caused by the introduction of the memristive switch.

Considering the spike trajectories of Fig. 7d, one can see that the limit cycles of the original model and the model from Sect. 3.1 are distantly similar. On the other hand, the limit cycles of the models from Sects. 3.2 and 3.3 are extremely similar. For this reason, the grouping of the models mentioned for the spiking behavior applies for the bursting behavior, as well.

5 Conclusion

In this work, we have analyzed the power flows of an equivalent circuit of the Hindmarsh–Rose model. Based on this analysis, we have simplified the equivalent circuit by replacing a nonlinear inductance, resistance, and voltage source by constant circuit elements. In addition, we have replaced the switch proposed for the equivalent circuit by two memristors. These memristors enable a smooth, continuous switching between two competing current paths, preventing high current peaks occurring during the switching process. Moreover, we have approximated the cubic nonlinearity of the original Hindmarsh–Rose model by three memristors, acting as passive circuit elements. In total, our simplified Hindmarsh–Rose circuit only requires one active component given by a negative impedance converter. In contrast to other approaches reported in the literature, this significantly reduces the amount of required transistors and operational amplifiers.

We have verified our circuit’s ability to generate spiking and bursting dynamics by LTspice simulations. While the amount of spikes and bursts have changed, the qualitative behavior is maintained by the simplified circuit.

Considering a practical circuit implementation, there are several challenges that need to be addressed in future research. For example, a sensitivity analysis of the circuit parameters with respect to the desired neuronal dynamics, as well as implementation with more advanced software tools such as PSPICE can aid the design process. Even more importantly, as discussed in, for instance, [39], memristors suffer from large manufacturing variability and might even undergo irreversible changes. Hence, more reliable, available memristors are required. How reliable the parameters of these memristors should be can be investigated in advance, for example, by bifurcation analyses with respect to the memristor parameters used for the approximated cubic nonlinearity.

Data availability

The data generated to support the findings of this study are available from the corresponding author upon reasonable request.

Change history

30 October 2023

A Correction to this paper has been published: https://doi.org/10.1140/epjb/s10051-023-00609-9

References

A.L. Hodgkin, A.F. Huxley, A quantitative description of membrane current and its application to conduction and excitation in nerve. J. Physiol. 4(117), 500–506 (1952). https://doi.org/10.1007/BF02459568

M. Amiri, S. Nazari, K. Faez, Digital realization of the proposed linear model of the Hodgkin-Huxley neuron. Int. J. Circuit Theory Appl. 47(3), 483–497 (2019). https://doi.org/10.1002/cta.2596

C. Morris, H. Lecar, Voltage oscillations in the barnacle giant muscle fiber. Biophys. J . 35(No. 1), 193–205 (1981). https://doi.org/10.1016/s0006-3495(81)84782-0

V. Rajamani, M. Sah, Z. Mannan, H. Kim, L. Chua, Third-order Memristive Morris-Lecar model of barnacle muscle fiber. Int. J. Bifurc. Chaos (2017). https://doi.org/10.1142/S0218127417300154

R. Cai, Y. Liu, J. Duan, A. Tesfay, State transitions in the Morris-Lecar model under stable Lévy noise. Eur. Phys. J. B 93, 38 (2020). https://doi.org/10.1140/epjb/e2020-100422-2

H. Fatoyinbo, S.S. Muni, A. Abidemi, Influence of sodium inward current on the dynamical behaviour of modified Morris-Lecar model. Eur. Phys. J. B 95, 4 (2022). https://doi.org/10.1140/epjb/s10051-021-00269-7

Z. Rácz, M. Cole, J.W. Gardner, M.F. Chowdhury, W.P. Bula, J.G.E. Gardeniers, S. Karout, A. Capurro, T.C. Pearce, Design and implementation of a modular biomimetic infochemical communication system. Int. J. Circuit Theory Appl. 41(6), 653–667 (2013). https://doi.org/10.1002/cta.1829

N. Tsigkri-DeSmedt, J. Hizanidis, E. Schöll, P. Hövel, A. Provata, Chimeras in leaky integrate-and-fire neural networks: effects of reflecting connectivities. Eur. Phys. J. B 90(7), 139 (2017). https://doi.org/10.1140/epjb/e2017-80162-0

M. Sung, Y. Kim, Training spiking neural networks with an adaptive leaky integrate-and-fire neuron. IEEE Int. Conf. Consum. Electron. Asia (ICCE-Asia) (2020). https://doi.org/10.1109/ICCE-Asia49877.2020.9277455

J.B. Shaik, A. Vs, S. Singhal, N. Goel, Reliability-aware design of temporal neuromorphic encoder for image recognition. Int. J. Circuit Theory Appl. 50(4), 1130–1142 (2022). https://doi.org/10.1002/cta.3209

E.M. Izhikevich, N.S. Desai, E.C. Walcott, F.C. Hoppensteadt, Bursts as a unit of neural information: selective communication via resonance. Trends Neurosci. 26(3), 161–167 (2003). https://doi.org/10.1016/S0166-2236(03)00034-1

E.M. Izhikevich, Simple model of spiking neurons. Trans. Neur. Netw. 14(6), 1569–1572 (2003). https://doi.org/10.1109/TNN.2003.820440

B. Abdoli, S. Safari, A reconfigurable real-time neuromorphic hardware for spiking winner-take-all network. Int. J. Circuit Theory Appl. 48(12), 2141–2152 (2020). https://doi.org/10.1002/cta.2877

J.L. Hindmarsh, R.M. Rose, A.F. Huxley, A model of neuronal bursting using three coupled first order differential equations. Proc. R. Soc. Lond. B 221(1222), 87–102 (1984). https://doi.org/10.1098/rspb.1984.0024

R. Barrio, S. Ibáñez, L. Pérez, Hindmarsh-Rose model: close and far to the singular limit. Phys. Lett. A 381(6), 597–603 (2017). https://doi.org/10.1016/j.physleta.2016.12.027

B. Bao, A. Hu, H. Bao, X. Quan, M. Chen, W. Huagan, Three-dimensional memristive Hindmarsh-Rose neuron model with hidden coexisting asymmetric behaviors. Complexity 2018, 1–11 (2018). https://doi.org/10.1155/2018/3872573

N. Gomar, B. Moradi, M. Ahmadi, Digital hardware implementation of a biological central pattern generator. IEEE Int. Midwest Symp. Circuits Syst. (MWSCAS) (2018). https://doi.org/10.1109/MWSCAS.2018.8624033

S. Vaidyanathan, C. Volos, I. Kyprianidis, I. Stouboulos, E. Tlelo-Cuautle, Memristor: a new concept in synchronization of coupled neuromorphic circuits. J. Eng. Sci. Technol. Rev. 8, 157–173 (2015). https://doi.org/10.25103/jestr.082.21

Y. Lihua, R. Guodong, C. Wang, Synchronization of neuronal circuits with ring connection on pspice. J. Control Sci. Eng. 2016, 1–10 (2016). https://doi.org/10.1155/2016/3414909

M. Wouapi Kemayou, F. Hilaire, P. Louodop, F. Florent, N. Zeric, H. Temene, Various firing activities and finite-time synchronization of an improved Hindmarsh-Rose neuron model under electric field effect. Cogn. Neurodyn. 14, 375–397 (2020). https://doi.org/10.1007/s11571-020-09570-0

P. Arena, L. Fortuna, M. Frasca, Extended SC-CNN implementation of the Hindmarsh-Rose neuron. Proc. Sixth IEEE Int. Workshop Cell. Neural Netw. Appl. (2000). https://doi.org/10.1109/CNNA.2000.877352

J. Cai, H. Bao, X. Quan, Z. Hua, B. Bao, Smooth nonlinear fitting scheme for analog multiplierless implementation of Hindmarsh-Rose neuron model. Nonlinear Dyn. 104, 4379–4389 (2021). https://doi.org/10.1007/s11071-021-06453-9

J. Cai, H. Bao, M. Chen, X. Quan, B. Bao, Analog/digital multiplierless implementations for nullcline-characteristics-based piecewise linear Hindmarsh-Rose neuron model. IEEE Trans. Circuits Syst. I(69), 2916–2927 (2022). https://doi.org/10.1109/TCSI.2022.3164068

K. Ochs, S. Jenderny, An equivalent electrical circuit for the Hindmarsh-Rose model. Int. J. Circuit Theory Appl. 49(11), 3526–3539 (2021). https://doi.org/10.1002/cta.3113

S. Jenderny, K. Ochs, M. Gibson, P. Hövel, A simplified Hindmarsh-Rose model based on power-flow analysis. In: Accepted at 2023 21st IEEE International New Circuits and Systems Conference (NEWCAS) (2023)

E. Solan, E. Pérez, D. Michaelis, C. Wenger, K. Ochs, Wave digital model of a TiN/Ti/HfO2/TiN memristor. Int. J. Numer. Model. Electron. Netw. Dev. Fields 32(5), 2588 (2019). https://doi.org/10.1002/jnm.2588

S. Jo, T. Chang, I. Ebong, B. Bhadviya, P. Mazumder, W. Lu, Nanoscale memristor device as synapse in neuromorphic systems. Nano Lett. 10, 1297–301 (2010). https://doi.org/10.1021/nl904092h

Z. Wang, S. Joshi, S. Savel’ev, H. Jiang, R. Midya, P. Lin, M. Hu, N. Ge, J.W. Strachan, Z. Li, Q. Wu, M. Barnell, G.-L. Li, H. Xin, S. Williams, Q. Xia, J.J. Yang, Memristors with diffusive dynamics as synaptic emulators for neuromorphic computing. Nat. Mater. 16, 101–108 (2016). https://doi.org/10.1038/nmat4756

L. Lu, C. Bao, M. Ge, Y. Xu, L. Yang, X. Zhan, Y. Jia, Phase noise-induced coherence resonance in three dimension memristive Hindmarsh-Rose neuron model. Eur. Phys. J. Spec. Top. 228, 2101–2110 (2019). https://doi.org/10.1140/epjst/e2019-900011-1

Y. Yu, M. Shi, H. Kang, M. Chen, B. Bao, Hidden dynamics in a fractional-order memristive Hindmarsh-Rose model. Nonlinear Dyn. 100, 891–906 (2020). https://doi.org/10.1007/s11071-020-05495-9

M. Lv, C. Wang, R. Guodong, X. Song, Model of electrical activity in a neuron under magnetic flow effect. Nonlinear Dyn. 85, 1479–1490 (2016). https://doi.org/10.1007/s11071-016-2773-6

Z. Wang, X. Shi, Electric activities of time-delay memristive neuron disturbed by Gaussian white noise. Cogn. Neurodyn. 14, 115–124 (2020). https://doi.org/10.1007/s11571-019-09549-6

L. Xu, G. Qi, J. Ma, Modeling of memristor-based Hindmarsh-Rose neuron and its dynamical analyses using energy method. Appl. Math. Model. 101, 503–516 (2022). https://doi.org/10.1016/j.apm.2021.09.003

X. Hu, C. Liu, L. Liu, J. Ni, S. Li, An electronic implementation for Morris-Lecar neuron model. Nonlinear Dyn. 84, 2317–2332 (2016). https://doi.org/10.1007/s11071-016-2647-y

C. Yakopcic, M.T. Taha, Analysis and design of memristor crossbar based neuromorphic intrusion detection hardware. Int. Jt. Conf. Neural Netw. (IJCNN) (2018). https://doi.org/10.1109/IJCNN.2018.8489252

A. Holt, J. Carey, A method for obtaining analog circuits of impedance convertors. IEEE Trans. Circuit Theory 15(4), 420–425 (1968). https://doi.org/10.1109/TCT.1968.1082847

M. Itoh, Synthesis of electronic circuits for simulating nonlinear dynamics. Int. J. Bifurc. Chaos 11, 605–653 (2001). https://doi.org/10.1142/S0218127401002341

A.M. Soliman, Generation and classification of CCII and ICCII based negative impedance converter circuits using NAM expansion. Int. J. Circuit Theory Appl. 39(8), 835–847 (2011). https://doi.org/10.1002/cta.671

L. Minati, L.V. Gambuzza, W.J. Thio, J.C. Sprott, M. Frasca, A chaotic circuit based on a physical memristor. Chaos Solitons Fractals 138, 109990 (2020). https://doi.org/10.1016/j.chaos.2020.109990

Acknowledgements

This work was funded by the Deutsche Forschungsgemeinschaft (DFG—German Research Foundation) under Project-ID 434434223-SFB 1461.

Funding

Open Access funding enabled and organized by Projekt DEAL.

Author information

Authors and Affiliations

Contributions

Conceptualization: SJ and KO; methodology: SJ; formal analysis: SJ, KO, and PH; writing—original draft preparation: SJ; writing—review and editing: KOs and PH; supervision: KO. All authors have read and approved the final manuscript.

Corresponding author

Ethics declarations

Conflict of interest

The authors have no relevant financial or non-financial interests to disclose. PH currently serves as Associate Editor of EPJB and has not been involved in the review process of this manuscript.

Additional information

The original online version of this article was revised: In table 3, the units of the Parameters Sp,n1 , Sn,n1 , Sp,n2 , Sn,n2 , Sp,n3 , and Sn,n3 should read GHz/V, instead of GHz.

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article’s Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Jenderny, S., Ochs, K. & Hövel, P. A memristor-based circuit approximation of the Hindmarsh–Rose model. Eur. Phys. J. B 96, 110 (2023). https://doi.org/10.1140/epjb/s10051-023-00578-z

Received:

Accepted:

Published:

DOI: https://doi.org/10.1140/epjb/s10051-023-00578-z