Abstract

In this review of experimental studies, the retention time and endurance of memristor RRAM memory elements based on reversible resistive switching in oxide dielectrics are studied. The influence of external parameters—switching pulses and ambient temperature—as well as internal factors—evolution of the concentration of oxygen vacancies in the filament region, the material, structure; the thickness of the active dielectric layer, material of metal electrodes on the long-term stability of high resistance state (HRS) and the low resistance state (LRS) of the memristor is discussed.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

INTRODUCTION

Due to the promising prospects for the construction of nonvolatile memory ICs of terabit capacity and applications for neuromorphic computing [1], the number of studies in the field of memory devices based on resistive switching in dielectrics has grown exponentially. Memory cells based on the storage of electric charge have approached the physical limits of scaling due to the lack of ideal dielectrics, limiting current leakage through structural defects, and tunneling effects. In contrast, in memory cells based on resistive switching mechanisms (ReRAM), an ideal dielectric is not needed, but the structure of its local defect regions have to be limited to the nanoscale. The cationic-anionic charge transport in this region under the influence of an external electric field leads to a local and reversible change in the structural defects of the dielectric, which is externally expressed in stepwise changes in the conductivity of the cell and resistive switching between its states with high resistance (HRS or RESET state) and low resistance (LRS or SET state). These states are established after exposure to a switching pulse of a certain polarity, duration, and amplitude. In the absence of external electric fields, an ideal memristor (a resistor with memory) is able to maintain the HRS and LRS for as long as desired with the fixed value of the electrical resistance of the cell. Thus, a bit of information in the memristor memory cell is stored in the form of structural changes in the local region of the dielectric enclosed between the two conducting electrodes. Memristors with only two levels of electrical resistance (one-bit), integrated into the cross-bar architecture [2–6], and in 3D configurations [7, 8], represent the foundation for future ultralarge integrated circuits of fast nonvolatile memory ReRAM with a long retention time. At the same time, multilevel (multibit) memristors with a set of intermediate discrete levels of electrical resistance of the cells (from 4 to 20) [9–17] offer the possibility of creating systems with a parallel computing mechanism and synaptic plasticity function, which is necessary for constructing recurrent neural networks and next generation artificial intelligence architectures [18–21].

Unipolar [16, 12] and bipolar [23–25] switching between the HRS and LRS is possible. In unipolar devices, switching between resistive states is carried out by the voltage pulses of the same polarity but of different amplitudes. In bipolar memristors, in order to change the cell states, it is necessary to reverse the polarity of the applied pulse [26]. In the mode of reading the HRS and LRS, small measuring voltage pulses are used that do not lead to switching between memristor states, but their parameters require careful analysis in terms of a possible cumulative long-term effect.

Different designs and structures of resistive cells can have different switching mechanisms. For example, in a number of memristors, the resistance value of the HRS and LRS depends on the contact area [27–29]. This may be due to both the drift-trap mechanism of charge carriers [27, 29] and the formation of multiple filaments [28]. The advantage of devices of the first type is lower power consumption, but at the same time they have a worse HRS/LRS ratio and a lower switching speed. In addition, they have significantly poorer prospects for scaling in high-density integrated circuits. Devices of the second type can be used as multibit devices.

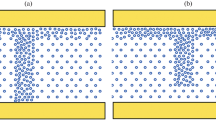

For systems with a high degree of integration, cell structures that are analyzed further, where the entire area of the metal-dielectric interface is not involved in the process of resistive switching and the sharp change in the electrical resistance is due to the formation of one or several electrically conductive filaments of a sub-10-nm thickness of the filaments, which are more promising (Fig. 1).

The formation of filaments in dielectric layers was observed experimentally in [30–32]. Filament-type cells are characterized by a high switching rate and a high HRS/LRS resistance ratio, and are currently most widely studied [33, 34]. Filamentary memristors, in turn, are subdivided into those in which switching is based on the movement of oxygen anions (charged oxygen vacancies) [4, 35–37] and those in which the conducting filament is formed by metal cations (Ag, Ni, Cu) [11, 20, 38, 39].

Memristors, based in principle on the transport of anions, must contain an excessive amount of vacancies (usually oxygen vacancies in oxide dielectrics). An excess concentration of vacancies can be obtained by (i) choosing a nonstoichiometric metal oxide as an active medium, (ii) using an oxidizing metal as an electrode in contact with a dielectric, or (iii) using multilayer composite dielectrics as a vacancy generator. In the last two cases, nonstoichiometric regions are created at the interfaces of the layers: reservoirs of oxygen vacancies.

There are also structures of memristors, where the switching process includes the transport of both oxygen ions and metal cations [2, 27, 40–43] simultaneously. For example, the movement of Ta cations was observed in the Ta/HfO2/Pt anionic memristor [11]. Even atoms of chemically inert electrodes, such as Pd in Pd/AlOx/Pd [35], or Pt in Pt/TiO2/Pt [44] in some cases can participate in the mechanisms of resistive switching.

For the formation of an initial filament in a newly fabricated cell, a pulse of a higher voltage (forming) is usually required [45, 46], compared with pulses of further switching. Due to inhomogeneities in the composition and structure in the dielectric film of the cell, as well as nanoroughness (needle-shaped protrusions) of metal electrodes, the forming voltage pulse creates a local inhomogeneity of the field strength, and, accordingly, is controlled by the breakdown of the dielectric, which forms a conducting channel (channels) in the form of filaments with a high content of oxygen vacancies or metal cations. Generally speaking, the individual forming of each cell for a giga- or terabit memory chip is not economically feasible; therefore, ways of creating formless filamentary memristors that do not require individual forming procedures are currently being intensively sought [17, 40, 47, 48].

A number of requirements are imposed on modern single-bit resistive memory cells for building ultralarge integrated circuits (ULICs) based on them: device design scalability, SET/RESET rewriting voltage less than 1 V, power consumption less than 10 pJ per switch, switching time less than 10 ns, information retention time not less than 10 years at 85°C, number of rewriting cycles (endurance) 1012, etc. A number of parameters, such as scalability [40, 49, 50], speed [9, 50, 51], and energy efficiency [52, 53], have already been achieved, albeit, in different cell designs and with different active dielectric materials.

At the same time, the current priority issues are endurance of the considered devices and retention time of information (retention time). These problems are the subject of analysis in this study.

DEGRADATION OF MEMRISTORS

Despite the fact that endurance of more than 1012 switchings was observed, for example, in [6, 47, 50], and the required retention time was stated in [54–57], these results were achieved in the study of a single device.

Switching of filament-type memristors involves disruption/creation filaments. For vacancy memristors, a filament is a region with an excess concentration of vacancies. Having an effective positive charge, oxygen vacancies attract electrons, forming neutral complexes. Such a complex (F-center) can be represented as a quasi-atom with energy levels located in the forbidden zone. Breaking away from the vacancy, the electron goes into the conduction band according to the reaction \({{{\text{F}}}^{x}} \to V_{x}^{ + } + {{e}^{ - }}\). In cationic memristors, a filament is a conductive filament formed by metal cations. The advantage of the first group consists in longer retention times due to the rather high migration energy of the oxygen ions in the bulk of most oxides (>1 eV) [4, 58, 59]. In the case of the motion of cations, their activation energy for bulk diffusion is much lower (<0.3 eV) [60], which favors low switching voltages but also low retention times [61].

Papers [31, 62, 63] are devoted to the observation of filaments and the study of the dynamics of their switching. In [64, 65], a stochastic approach is proposed that simulates microscopic processes inside transition metal oxides. The model is based on percolation theory and a resistor network. The dynamics of the migration of oxygen vacancies without taking into account the Joule heating of the filament during the flow of an electric current [66–70] and taking into account the Joule heating [21, 71–76] were studied theoretically based on the kinetic equations.

The retention time of information for memristors is determined by the stability of the LRS and HRS in time. In order to determine it, after the SET/RESET transition to the structure, a voltage pulse is applied (Vread ≈ 0.1 V, tread ≈ 1 ms) periodically (Δt ≈ 1 s) and the dependence of the current on time is recorded for each resistive state. To eliminate the effect of charge accumulation, the polarity of the switching pulse should be periodically changed. This was done, for example, in [37]. The predicted retention time of the memristor states should be 10 years at a temperature of 85°C. Real measurements are carried out over several hours/days, after which the data are extrapolated over time [48, 77, 79]. Thanks to the Arrhenius dependence probabilities of the formation/recombination of point defects, as well as their diffusion/drift processes, the retention time of information is often determined at elevated temperatures [37, 80–81]. After that, the retention time is recalculated to the required temperature value. This approach is also susceptible to errors. Thus, in the work [77], the dependence of resistance on the information retention time for the Pt/Al2O3/HfO2/Al2O3/TiN memristor is investigated at room and elevated (85°C) temperatures. At room temperature, the resistances of the LRS and HRS increased with the observation time, while at 85°С, they decreased. In [37], using the TiN/HfOx/Pt memristor as an example, it was shown that the estimate of the retention time based on data extrapolation may be incorrect due to the detected abrupt degradation of the HRS state by the complete failure at a certain point in time.

The endurance of a memristor cell is determined by its stability as a result of multiple switching cycles. Each cycle consists of a set of voltage pulses: Vset(~1 V, ~10 ns)–Vread(~0.1 V, ~10 ns)–Vreset(~–1 V, ~10 ns)–Vread(~0.1 V, ~10 ns). As a result, the dependence of the current (resistance) on the number of such cycles is obtained [33].

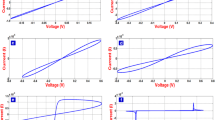

Analyzing the experimental data of many publications on structures in which switching is caused by the formation/rupture of a conducting filament, it can be seen that after a series of cyclic switchings in the memristor cell, the HRS and LRS are not reproduced with ideal accuracy. In a practically acceptable case, the resistances of the high-resistance and low-resistance states of single-bit memristors should remain within the allowable windows for HRS and LRS, set by the maximum and minimum values (Fig. 2a). Such behavior would mean no degradation of states. However, in some cases, it turns out that either the high resistance or low resistance is out of the specified range.

Memristor degradation is expressed as a change in resistance over time or number of switchings. Ultimately, degradation leads to device failure by the memristor “sticking” in a state with a certain resistance value [82]. When tested for endurance, the most common degradation of the state of the HRS (Fig. 2b), leading to a decrease in resistance in this state and, as a result, to the impossibility of switching the LRS into the HRS, takes place [9, 15, 21, 42, 83]. Sometimes, RHRS increases with increasing switching cycles [52, 84] (Fig. 2c), and in some cases there is an increase in the resistance of RLRS [25, 85] (Fig. 2d).

For retention time, the most typical cases are an increase in resistance in the LRS and a decrease in the HRS [28, 48, 80, 81, 86–88] (Figs. 2b, 2d). In [80, 81], the retention time of the Ir/Ta2O5 –δ/TaOx/TaN memristor was investigated. It was found that for a memristor with a filament of a larger cross section, a decrease in resistance is observed in the HRS and an increase in resistance in the LRS for filaments with a smaller cross section. This result suggests that the degradation of the LRS and HRS states in the study of retention time is primarily determined by diffusion processes. For filaments of a small diameter, due to radial diffusion, the filament dissolves, leading to a decrease in the LRS. For filaments of a large diameter, the HRS degrades due to longitudinal diffusion in the rupture region.

During the switching cycles of states, the authors of the works [36, 82, 89–90] found a situation when, as a result of degradation, the memristor takes on some intermediate state between the RHRS and RLRS (Fig. 3). The degradation of a Ti/HfOx/TiN memristor was investigated in [36]. The endurance test fails when \(2.5\,\, \times \,\,{{10}^{4}}\) switching cycles after the application of a negative pulse. The memristor is stuck in an intermediate position between the HRS and LRS. Before the failure, the resistance of the LRS gradually decreased, while the HRS remained practically stable. The reason for the degradation, according to the authors, is due to the fact that SET/RESET repetitions lead to the appearance of additional defects, which causes (i) an increase in the reservoir of defects near the upper electrode and (ii) a decrease in the energy of their migration due to the higher density of vacancies, which leads to an increase in the filament. It was found that the maximum value of the limiting voltage (Vstop) during the RESET cycle is the key parameter that controls the endurance of the switching (a decrease in Vstop leads to an increase in endurance). Sticking in an intermediate state was also observed for a Ti/HfSiOx/TiN memristor [89]. It showed a slight decrease in the HRS and LRS with the number of cycles less than 1.5 × 105; then, the LRS began to grow, and the HRS fell sharply until they coincided. It has been found that the fault is always caused by negative voltage, i.e., when the filament breaks. The authors believe that the failure is due to the injection of defects from the lower electrode. As a result, the filament thickens, causing a decrease in the HRS.

Smooth resistance change HRS and LRS from first switching cycles/observation times observed in [5, 10, 25, 42, 43, 48, 49, 80, 81, 85, 86] (Fig. 2). Analysis of the Cu/HfO2/Pt devices [42] showed a monotonic decline in the HRS with the first switching cycles and sticking in the LRS (Fig. 2b). A decrease in VSET was noted with an increase in the number of switching cycles, while VRESET grew. The main difference between the initial and switched filaments was the copper concentration, which was significantly higher in the second case. By adjusting the switching voltages, it was possible to achieve >109 switching cycles. Arrays of Cu/TaOx/Pt memristors consisting of 50 cells were investigated in [42]. The time for which the HRS and LRS were maintained after 1, 100, and 1000 switching cycles was studied. It was observed that with an increase in the number of switching cycles, the time period during which the LRS state is maintained increases, while the time period for which the HRS is maintained decreases. This reduces the dispersion of resistances from device-to-device. According to the works [15, 42], the newly formed filament takes on its stationary shape, corresponding to the parameters of the switching pulse, after a certain number of switching cycles. If the pulse parameters are chosen incorrectly, then the evolution of the filament to the equilibrium state will be accompanied by degradation of the LRS and/or HRS.

In many cases, the resistance begins to change only after a certain critical value of the observation time/switching pulse [24, 37, 42, 52, 90] (Fig. 4).

For a TaN/ZnO/ZrO2/Pt memristor [24], the LRS does not change within 103 switching cycles, while the HRS begins to decline after 900 cycles (Fig. 4a). The authors attribute the possible reasons for the deterioration of the HRS to the unstable RESET operations arising from the excessive growth of conductive filaments and the creation of other filaments during the switching cycles. A decrease in the HRS with increasing switching cycles, caused by unrecovered defects in the oxide matrix, accumulating from cycle-to-cycle, was also observed in the TiN/HfOx/AlOx/Pt memristor [10].

In [90] degradation of the highly conductive state was observed (Fig. 4b). At the same time, an increase in voltage VSET was detected after 107 and 109 switching cycles. According to the authors, this increase indicates a decrease in the mobility of oxygen vacancies. Since the failure of the memristor occurs at a fixed voltage, by increasing the voltage at the gate of the memristor, it can be returned to the operating state again. In [91], using a TiN/Hf/HfO2/TiN memristor as an example, a method for controlling the motion of defects was proposed. Four regions were found depending on the resistance of the LRS and HRS on the number of switching cycles: (i) where the resistance states are stable, (ii) resistance increases in LRS state, (iii) the memristor is stuck in the HRS, and (iv) in a region restored by the application of a higher positive voltage. It was found that, after a failure, the rupture region is surrounded by defects with lower/higher energy levels, which disappear after the memristor is restored, which confirms their role in degradation. When the concentration of these defects reaches a critical level, they (i) repel other defects from the transition to the discontinuity region, causing the SET to fail; (ii) they can form a shunt current path at Vset by reducing the stress in the region of the filament’s rupture and contributing to the degradation of the memristor; (iii) the defects impede conductivity when Vread due to energy level shift and/or the longer electron tunneling path.

The possibility of creation a memristor memory cell after its failure is also discussed in [52]. Thus, the endurance of the memristor TiN/Hf/HfO2/TiN is ~107 switchings, but after each failure it was possible to restore the device by applying an increased SET voltage (by a factor of at least 5). Thus, the introduction of a check operation can significantly increase the lifespan of these devices. For an Pt/TiO2/TiN memristor [9], a test during retention at 85°C showed that resistances with higher values increase slightly with time, while the states with lower resistances remained practically unchanged for more than 256 hours. The endurance test passed 2 × 106 switching cycles, after which the memristor became stuck in the LRS state. The RESET operation using the DC sweep mode returned the device to an operating state, after which it withstood another ~106 switching cycles.

Further, various factors are discussed that affect the endurance and retention time of information in memristor memory cells.

1 Influence of Temperature

The operation of memristors is based on the drift of ions within the dielectric layer and reactions of the formation/recombination of point defects. The degradation of memristors is caused by diffusion processes through the conducting electrodes and in the region of the dielectric surrounding the filament. All the listed processes have an Arrhenius dependence and, therefore, strongly depend on temperature. Therefore, it should be expected that the increase in temperature leads to a decrease in the endurance and retention time of memristors [42, 43]. The decrease in retention time with increasing temperature has been confirmed by numerous studies. Thus, tests at elevated temperatures (100, 125, 140°C) [92] showed that the retention time (τ) dropped with increasing temperature, and lnτ turned out to be a linear function of the reciprocal temperature, which indicates the diffusion nature of degradation. The growth of temperature leads to earlier degradation also for the Cu/HfO2/Pt memristor [42]. In this case, the HRS was practically independent of temperature, which indicates tunneling as the dominant form of conduction in a weakly conducting state. The metallic properties of the LRS of this memristor are indicated by the linearity of the current-voltage characteristic with positive temperature dependence. In [78], a formless W/AlOx/Al2O3/Pt/Ti memristor was obtained with a high switching speed (28 ns). The study of this memristor at high and low temperatures relative to room temperature showed a decrease in the HRS/LRS resistance ratio (~103 at 100, ∼103 at 298, and ∼80 at 400 K) and retention time (∼106 s at 100 K, ∼104 s at 400 K) at elevated temperatures.

In contrast, in [21] the addition of a layer HfOx layer in an Au/CeOx/Al memristor provoked an increase in temperature in the region of the filament and increased the endurance of this structure. In [46] it was possible to reduce the forming voltage from 2.5 to 1.7 V due to the process at increased (125°C) temperatures. At the same time, the spread of the HRS and LRS resistances was reduced and the information retention time increased by a factor of more than 40. The authors believe that the reason for the obtained improvements is the recombination of excess oxygen vacancies.

The test for the retention time for a Pt/Al2O3/HfO2/Al2O3/TiN memristor [77] was carried out at room and elevated (85°C) temperatures. At room temperature, after 102 s, there is a parallel increase in the LRS/HRS resistance; and at 85°C, a parallel decline. The authors explain the obtained result by the competition of two effects: (i) oxygen from the atmosphere can slowly diffuse into the samples at room temperature, which leads to a gradual decrease in the concentration of oxygen vacancies, i.e., an increase in the HRS and LRS; (ii) an increase in temperature provokes the creation of oxygen vacancies. At low temperatures the first mechanism prevails; and at high temperatures, the second mechanism is prevalent.

These results indicate that, in order to increase the retention time, it is necessary to choose materials with high energies of migration of oxygen vacancies. However, this will inevitably lead to an increase in the switching voltage. From the point of view of the endurance of devices, the lower temperatures are not a guarantee of an increase in the number of switchings, since lower temperatures make it difficult to recover the broken filament. Thus, for a W/AlOx/Al2O3/Pt/Ti memristor [78], the best endurance was achieved at room temperature (108 at 100, 1010 at 298, and 107 at 400 K).

2 Influence of Switching the Pulse Parameters

The selection of the switching pulse parameters is the simplest way to improve the performance of the device. Therefore, the study of the influence of the duration and amplitude of the applied SET/RESET pulses is an important stage in the study of the properties of memristors.

Using the example of a TiN/HfO2/Hf/TiN memristor, the authors [79] showed that with the optimal selection of the SET/RESET pulse parameters, the memristor’s endurance can exceed 1010. Most authors [90–92, 94] note that an increase in the switching amplitude leads to a decrease in the endurance of the device.

Thus, it was found in [90] that an increase in the voltage in a TiN/HfO2/Hf/TiN memristor leads to its earlier failure, which is explained by the decrease in the mobility of oxygen vacancies (the energy barrier increases), due to the local relaxation of amorphous HfO2 to the minimum energy state (short-range atomic rearrangement) caused by elevated temperatures. Also in this work, an increase in endurance was observed with an increase in the LRS resistance (below the operating current). A memristor whose operating principle is based on the diffusion of silver ions [92] has shown endurance >108 switching cycles. According to the authors, the result obtained is associated with minimizing the switching voltage, since the endurance readings are reduced on devices with a large limiting current. The rise in the RESET voltage and its duration also reduced the endurance of the TiN/Ta2O5/Ta memristor [94]. It was found that at high voltages and pulse durations the memristor sticks in the HRS position; and at low voltages, in the LRS. The results are explained by the gradual oxidation of the TiN electrode, which ultimately leads to the impossibility of filament reduction due to the difficult removal of O from TiN in the first case. However, toggling with lower RESET voltages may be insufficient for the oxidation of TiN, but sufficient for the diffusion of oxygen ions along the internode or grain boundaries. The endurance of the TiN/Hf(Al) O/Hf/TiN memristor was tested at two SET voltages of 1.5 and 2.5 V [83]. In the first case, after ~107 there was a sharp rise in the LRS and a smoother rise in the HRS until they coincided. For 2.5 V after ~107 there is a decline in the HRS to the LRS level.

It was found in [89] that the endurance of the Ti/HfSiOx/TiN memristor as a function of the applied voltage for the given duration has the maximum (Vm). An increase in duration leads to a decrease in Vm, leaving the maximum number of switchings approximately constant. The dependence of the area of the hysteresis loop of current-voltage characteristic at various recording voltages (0.2, 0.4, 0.6, 0.8, 1, and 1.2 V) in a 10-nm memristor was studied in [95]. It was found that the loop area first gradually increases with an increase in the write voltage, and after the critical value (~1 V) it drops sharply. It was found that the resistance in the HRS is practically independent of the recording frequency and voltage, while the LRS resistance increases sharply with increasing voltage at low switching frequencies and weakly at high frequencies. In [48], it was found for an unformed Al/ZnO/Al memristor that the hysteresis window decreases with an increase in the sweep frequency. According to the authors, the detected interstitial oxygen ions play a decisive role in the process of resistive switching, contributing to the destruction of oxygen vacancies during the RESET process.

A number of works suggest varying the amplitude and/or duration of the switching pulse to increase the service life of the device. The conductivity values of a Ta/TaOx/Pt memristor [96] in the 1T1R cell array was achieved by a combination of transistor gate control and a developed feedback algorithm. It was obtained that one cell of the TaOx memristor can be precisely and repeatedly programmed (more than 106) to precisely represent 6-bit values. The authors of [97] managed to improve the endurance of the Ti/HfO2/Pt memristor due to the smooth transition from the ON state to the OFF state and vice versa. This was achieved by using a positive offset current sweep during the SET and a rising voltage sweep during the RESET. By adding a series resistor to a Pt/Ta/TaOx/Pt/Ta to the memristor [98], with the correct resistance during the SET and RESET cycles, it is possible to suppress the unevenness of the internal voltage drop across it, which leads to a significant increase in its service life. Application of a fixed write pulse can lead to degradation due to changes in the thickness/length of the break in the filament . To avoid this, the theoretical model [99] proposes a recording scheme that identifies the optimal amplitude and duration for the recording pulse. It has been found that the proposed scheme for various malfunctions of the memristor can effectively improve its endurance.

3 Influence of the Concentration of Oxygen Vacancies

The concentration of oxygen vacancies is the governing parameter for memristors, whose operation is based on the movement of oxygen anions. The more vacancies that are contained in the oxide the smaller the voltage that is required for the formation of a filament. However, the accumulation of a large number of vacancies may be more likely to lead to the formation of pores, multiple filaments, and/or resizing of the initially formed filament during rewriting operations.

According to the work [100], the mechanisms of degradation of memristors can be attributed to the additional oxygen vacancies generated/recombined during switching, which leads to a change in the initial structure of the filament. When additional oxygen vacancies are generated during switching in or near the filament region, the filament increases, while the HRS and LRS decrease. The increase in resistance is a result of the additional recombination between oxygen ions and oxygen vacancies with an increase in the distance between the gaps during the RESET. Sometimes the memristor sticks in the intermediate state, mainly due to the defects that emerge from the upper and lower electrodes, which can lead to breakage of the filament.

The dependence of the endurance of the Pt/TaO2–x/Ta2O5–x/Pt memristor on the concentration of vacancies in the TaO2–x layer was studied in [50]. It was found that an increase in the concentration of oxygen vacancies lowers the switching resistance and the number of switching cycles. For memristor of 30 × 30 μm2, endurance was achieved for 1012 switching cycles.

However, according to [101], where structures based on TiO2 with different concentrations of oxygen vacancies (10, 20, and 30%) were investigated, it was found that the best manifestation of the memristor properties corresponds to a concentration of oxygen vacancies of 20%. The work [102] is also devoted to a study of TiOx-based memristors. Four TiOx sublayers were made in it with different contents of oxygen vacancies, and various combinations of the succession of layers were investigated. It was found that the ON/OFF ratios and retention times in both the on and off states are the best for a structure with a sequence of layers corresponding to a nonmonotonic distribution of the oxygen vacancy concentration. At the same time, the creation of a TaOx film in a Pt/TaOx/Pt memristor [103] with an oxygen concentration gradient ranging from Ta2O5–x at the anode to TaO2–x at the cathode made it possible to increase the endurance of the studied memristor to values exceeding 109 switching cycles. For Pt/HfOx/TiN [104], it was shown that in the case of an excessive number of vacancies (HfO1.5 compared to HfO2), a reduced forming potential is required, but at the same time, an increase in the spread of resistances is observed in both the HRS and LRS. In this study, a model is proposed that includes the rupture of the filament caused by the field and temperature. The rupture occurs near the anode in the case of a stoichiometric oxide, and at both interfaces in the case of an oxygen deficiency. According to the model, the thermal ion/vacancy motion decreases in the oxygen-deficient memristor due to the higher heat transfer.

Thus, the concentration of oxygen vacancies is the most important parameter in the creation of anionic memristors. However, an unambiguous relationship between the concentration of vacancies and the endurance of the device has not been traced, and further research is required in order to understand it.

4 Active Dielectric Layer Structure and Thickness

The choice of the dielectric and its parameters radically changes the switching characteristics, as well as its endurance and retention time.

One of the most important parameters is the thickness of the dielectric layer. A decrease in the thickness, on the one hand, leads to a decrease in the amplitude of the switching pulse, but on the other hand, it decreases the ratio of resistances in the high-resistance and low-resistance states. The growth of the TaOx film thickness from 10 to 60 nm [54] for the Pt/TiOx/TaOx/Pt memristor shows a nonmonotonic dependence of the HRS and LRS resistance on film thickness with the minimum corresponding to 20 nm. At the same time, according to [83], an increase in the thickness of the HfO layer in the TiN/Hf(Al)O/Hf/TiN structure increases the endurance of the device.

Multilayer dielectrics are the subject of research by many authors [18, 39, 105]. The addition of an additional layer promotes the formation of a vacancy reservoir, and its thickness and composition affect the size of the specified reservoir and the migration and formation energies of vacancies. The use of multilayer dielectrics also affects the energy of the formation/migration of defects, which decreases in the area of the oxygen deficiency [29, 106].

In addition, the dependence of the heat capacity, density, and thermal conductivity on the film thickness leads to a change in the heating of the filament with a variation in the thickness, and, therefore, strongly affects the diffusion, drift, and creation/recombination of vacancies [21]. In the works [12, 13, 27, 107–117], an increase in the stability of devices with a two-layer dielectric, such as AlOx/HfO2, Ta2O5–x/TaO2–x, ZrOx/HfOx, ZrO2/AlON, and AlOx/Al2O3, was reported.

The Ag/SiO2/Ta2O5/Pt memristor was studied in [39], the switching properties of which are based on the disruption/creation of the Ag filament. Due to the SiO2 layer, in which the mobility of Ag ions is low, the growth direction thins the Ag filament in the Ta2O5 layer, which leads to the dissolution of the Ag filament in the Ta2O5 layer in the following operations. In single-layer Ag/Ta2O5/Pt and Ag/SiO2/Pt structures, there is a strong scatter in the HRS. The Ag/SiO2/Ta2O5/Pt memristor showed lower switching voltages and less variation in the HRS and LRS resistances from cycle-to-cycle. The endurance of the memristor cell has also increased. The SiO2/Ta2O5 boundary is a reservoir of vacancies due to which this memristor cannot be considered purely cationic, which may explain the increased endurance of the composite memristor.

It was found in [118] that Ti/TiO2/Pt breaks down during the RESET, which results in an LRS with extremely low resistance, which confirms the overgrowth of the conductive filaments. However, the addition of a vacancy-rich-2 nm ZrO2–x layer on the Ti/TiO2 boundary increased the retention time (>104 s) without any apparent degradation of the HRS and LRS resistances. According to [119], graphene can be used as an intermediate layer between the electrodes and the dielectric to reduce the scatter of parameters between cycles, by suppressing the diffusion of atoms between the electrode and the insulator, thereby increasing its endurance. The introduction of graphene can reduce energy consumption due to its high out-of-plane contact resistance (compared to metal electrodes) and suppress surface effects: chemisorption and/or photodesorption. The introduction of the TiO2 layer to the Pt/HfO2/TiO2/ITO memristor [120] made it possible to reduce the switching voltage due to the formation of a virtual cathode in the HfO2 layer. Similar results were obtained in [54] for the Pt/TiOx/TaOx/Pt memristor. The Ti/TiOx/Pt and Ti/HfO2/Pt devices were manufactured to clarify the role of the TiOx layer in the Ti/HfO2/TiOx/Pt memristor [13]. The Ti/HfO2/Pt memristor demonstrates explicit switching, whereas the Ti/TiOx/Pt memristor does not. This means that the resistive switching effect mainly occurs in the HfO2 layer, while the TiOx layer can serve as a reservoir of vacancies. The influence of an intermediate TiO2 layer on the switching characteristics of the ZrO2-based memristor was studied in [121]. Compared to the Cu/ZrO2/Pt and Cu/ZrO2/TiO2/Pt devices, the forming voltage, switching voltage, and reset current of the Cu/TiO2/ZrO2/Pt and Cu/TiO2/ZrO2/TiO2/Pt devices are clearly improved. The formless Ag/MnO/Ta2O5/Pt memristor [12] has three states: LRS, IRS, and HRS. The third state is explained as a break of the filament in MnO, and the HRS in both MnO (vacancy reservoir) and Ta2O5. The resistance window is 104. The MnO/Ta2O5 system has greater endurance and a lower switching voltage than structures with a single layer. The influence of the Al2O3 layer [122] in the Ti/Al2O3/HfO2/Al2O3/Pt memristor was studied by comparing its properties with a memristor without or with only one Al2O3 layer. It was found that the initial version has the largest resistance window and endurance of more than 105 cycles without visible degradation. According to the authors of [27], switching in a formless Pt/NbOx/TiOy/NbOx/TiN memristor was carried out due to the capture/release of electrons, where the oxygen vacancies in the central TiOy and/or Ti impurity centers in the NbOx layer near the upper Pt electrode play the role of traps. In this device, the switching current was much lower than that of the oxygen ion migration memristors. Adding the NiOx layer [123] in ITO/TaOx/NiOx/Al lowers the switching voltage greatly (ITO is a solid solution of indium(III) and tin(IV) oxides, typically 90% of the former and 10% of the latter). The proposed design avoids the breakage of filaments during the RESET process, which provides a more uniform and stable resistive switching behavior than other ReRAM devices. A study of the effect of an additional dielectric layer on the thermal properties was carried out in [21]. With the ratio of the thickness of the HfOx layers to the CeOx layers of 0.1 for the Au/CeOx/HfOx/Al memristor, the maximum heating is observed in the filament region, which is explained by the dependence of the thermal conductivity of the hafnium oxide layer on the thickness. With this ratio, the maximum endurance (>2 × 105) and the minimum operating switching voltage are observed.

Various dielectric materials were compared in [124, 125]. It was revealed in [124] that a memristor with Ta2O5/Ta has significantly better endurance (>109) compared to the HfO2/Hf memristor. A comparison of the HfO2, TiO2, Ta2O5, and Al2O3 metal oxides as an insulating layer of the memristor is carried out in [125, 126]. The energies of the formation of oxygen vacancies and their migration barriers were calculated. It is shown that contact with an active metal lowers the energy of vacancy formation. The high energy of formation reduces the likelihood of new vacancies forming during switching cycles, which ensures a constant number of vacancies and, as a consequence, increases endurance. TiO2 oxide contains a number of substoichiometric TiO2–x phases, which will prevent the preservation of the number of vacancies and, therefore, it is not advisable to use it to increase the endurance of devices. Al2O3 has a relatively high energy of formation of the O vacancy and high migration energy, making the migration of vacancies in the ReRAM cycle difficult. According to the authors, the endurance of Ta2O5 is due to the fact that Ta2O5 remains amorphous at higher temperatures than HfO2 and the adaptability of its lattice to the formation of oxygen vacancies.

Thus, by combining various oxides and varying the thickness of the films of an active medium, it is possible to control the switching parameters of the memristor, as well as its service life and information retention time.

5 The Influence of the Parameters of Conducting Cell Electrodes

The memristor electrode material not only affects the switching parameters but can also lead to rapid degradation of the device. The electrode material can be reactive with respect to oxygen and inert. The first type of electrodes is typically used to create a vacancy reservoir at the electrode/dielectric interface through a heterogeneous chemical reaction with the dielectric material. In this case, the energy of the formation/migration of defects decreases upon contact with the active electrode [125].

[103] compared to the different electrode materials for the TaOx-based memristor. It was found that memory cells with Ir, Pt, and Au electrodes having a high work function of electrons show stable resistance switching behavior, in contrast to Ag or W electrodes. In this study, it was found that stable switching occurs for metals of electrodes, whose electrochemical potential is greater than that of Ta. This indicates that the absence of the oxidation reaction of the electrodes is preferred for resistance switching. The authors [5] found that using Ru as the bottom electrode (BE) in the Pt/Ta2O5/BE memristor leads to a decrease in the switching voltage and a significant (by almost 3 orders of magnitude) maximum current level compared to the BE electrodes from Ta and Pt. Replacing the TiN electrode with Ru [94], which has a lower affinity for the oxygen anions in the TiN/Ta2O5/Ta memristor resulted in an increase in stability to more than 108 switching cycles. The authors explain the results obtained by the continuous slow oxidation of TiN at the heterointerface, which changes the vacancy balance in the reservoir and, ultimately, leads to the impossibility of filament reduction due to the difficult removal of O atoms from TiN. The characteristics of the Pt/HfO2/TiO2/HfO2/Pt and Pt/HfO2/TiO2/HfO2/TiN memristors, due to the material of the electrodes, were compared in the work [23]. In the case of a Pt electrode, the HRS/LRS ratio is ~105; and for the TiN electrode, it is ~102. In addition, the TiN memristor exhibits a strong HRS scatter and requires large switching voltages to extract vacancies from the reservoir.

For Pt/Ta2O5–x/TaO2–x/Al2O3/Pt [127], it was found that the roughness at the Pt/Ta2O5–x interface affects the switching mechanism in the memristor cell. The roughness contributes to the strong localization of the electric field, contributing to the formation of single filaments. At the same time, increasing the smoothness of the contacts contributes to the formation of multibit states. Previously, in [84] it was also found that due to the chemical-mechanical polishing (CMP) in the manufacture of the TiN/HfOx/TiN memristor cell resulted in increasing the endurance to more than \({{10}^{{10}}}\) switching cycles.

CONCLUSIONS

The review discusses the influence of temperature and switching pulse parameters, as well as the concentration of oxygen vacancies in the reservoir, materials of the conducting electrodes, and the active dielectric layer in the memristor, on the ability of devices to maintain the given value of the HRS and LRS resistance over time, and the stability of the HRS and LRS states during multiple rewriting cycles.

According to the results presented in the review, it can be concluded that the influence of these parameters on the endurance and the retention time of the states of memristors is complex and multifactorial. However, the following qualitatively described tendencies can be distinguished:

—A rise in temperature leads to a decrease in the endurance of the memristor cell due to the growth of activation processes of diffusion/migration and the generation/recombination of point defects. An increase in temperature can also lead to the formation of crystals of a new phase, which also reduces the endurance of the devices.

—An increase in the switching voltage and an increase in the switching pulse duration beyond the minimum required values also reduce the cell endurance, which can be explained by the excessive temperature rise in the filament region, and by the evolution of the filament during switching to a nonstationary state (breakage or excessive thickening).

—An increase in the concentration of oxygen vacancies in the reservoir and the active region of the dielectric contributes to a decrease in the forming potential and sometimes leads to the formation of a formless memristor, but at the same time the spread of resistances increases the HRS and LRS with the sequential switching of the cell, and its endurance is also reduced.

—The use of cells’ electrodes inert with respect to oxygen increases the service life and retention time of the information in the memristor cells. The films of the electrodes should have a minimum number of defects and insulate the active medium of the dielectric from the external environment. In some cases, it was found that sometimes a memristor degrades due to the defects introduced by the electrodes.

—The use of multilayer dielectric structures as the active medium of the memristor makes it possible to adjust the size and position of the vacancy reservoir, as well as the energy of the formation/migration of defects.

—Of the analyzed dielectrics in memristors, tantalum oxide Ta2O5 has the lowest energy of the migration and formation of oxygen vacancies, and remains amorphous at higher temperatures. This explains its advantage in the endurance of the cells and allows the use of low switching potentials.

REFERENCES

Ang, D.S., Zhou, Y., Yew, K.S., and Berco, D., On the area scalability of valence-change memristors for neuromorphic computing, Appl. Phys. Lett., 2019, vol. 115, p. 173501.

Carta, D., Salaoru, I., Khiat, A., Regoutz, A., Mitterbauer, C., Harrison, N.M., and Prodromakis, T., Investigation of the switching mechanism in TiO2-based RRAM: A two-dimensional EDX approach, ACS Appl. Mater. Interfaces, 2016, vol. 8, no. 30, pp. 19605–19611.

Matveyev, Y., Kirtaev, R., Fetisova, A., Zakharchenko, S., Negrov, D., and Zenkevich, A., Crossbar nanoscale HfO2-based electronic synapses, Nanoscale Res. Lett., 2016, vol. 11, p. 147.

Sun, W., Gao, B., Chi, M., Xia, Q., Yang, J.J., Qian, H., and Wu, H., Understanding memristive switching via in situ characterization and device modeling, Nat. Commun., 2019, vol. 10, p. 3453.

Yoon, J.H., Zhang, J., Lin, P., Upadhyay, Y.P., Liu, Y., Xia, Q., and Yang, J.J., A low-current and analog memristor with Ru as mobile species, Adv. Mater., 2020, vol. 32, no. 9, p. e1904599.

Cheng, H.Y., Chien, W.C., Kuo, I.T., Yeh, C.W., Gignac, L., Kim, W., Lai, E.K., Lin, Y.F., Bruce, R.L., Lavoie, C., Cheng, C.W., Ray, A., Lee, F.M., Carta, F., Yang, C.H., Lee, M.H., Ho, H.Y., Brightsky, M., and Lung H.L., Ultra-high endurance and low IOFF selector based on AsSeGe chalcogenides for wide memory window 3D stackable crosspoint memory, in Proceedings of the 2018 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, 2018, pp. 37.3.1–37.3.4.

Chakrabarti, B., Lastras-Montano, M.A., Adam, G., Prezioso, M., Hoskins, B., Payvand, M., Madhavan, A., Ghofrani, A., Theogarajan, L., Cheng, K.-T., and Strukov, D.B., A multiply-add engine with monolithically integrated 3D memristor crossbar/CMOS hybrid circuit, Sci. Rep., 2017, vol. 7, p. 42429.

Li, C., Han, L., Jiang, H., Jang, M.-H., Lin, P., Wu, Q., Barnell, M., Yang, J.J., Xin, H.L., and Xia, Q., Three-dimensional crossbar arrays of self-rectifying Si/SiO2/Si memristors, Nat. Commun., 2017, vol. 8, p. 15666.

Yoshida, C., Tsunoda, K., Noshiro, H., and Sugiyama, Y., High speed resistive switching in Pt/TiO2/TiN film for nonvolatile memory application, Appl. Phys. Lett., 2007, vol. 91, p. 223510.

Yu, S., Wu, Y., Jeyasingh, R., Kuzum, D., and Wong, H.-S.P., An electronic synapse device based on metal oxide resistive switching memory for neuromorphic computation, IEEE Trans. Electron Dev., 2011, vol. 58, no. 8, pp. 2729–2737.

Wedig, A., Luebben, M., Cho, D.-Y., Moors, M., Skaja, K., Rana, V., Hasegawa, T., Adepalli, K.K., Yildiz, B., Waser, R., and Valov, I., Nanoscale cation motion in TaOx, HfOx and TiOx memristive systems, Nat. Nanotechnol., 2016, vol. 11, pp. 67–74.

Lee, N.J., Kang, T.S., Hu, Q., Lee, T.S., Yoon, T.-S., Lee, H.H., Yoo, E.J., Choi, Y.J., and Kang, C.J., Tri-state resistive switching characteristics of MnO/Ta2O5 resistive random access memory device by a controllable reset process, J. Phys. D: Appl. Phys., 2018, vol. 51, p. 225102.

Liu, J., Yang, H., Ji, Y., Ma, Z., Chen, K., Zhang, X., Zhang, H., Sun, Y., Huang, X., and Oda, S., An electronic synaptic device based on HfO2TiOx bilayer structure memristor with self-compliance and deep-RESET characteristics, Nanotechnology, 2018, vol. 29, p. 415205.

Wu, W., Wu, H., Gao, B., Deng, N., and Qian, H., Suppress variations of analog resistive memory for neuromorphic computing by localizing Vo formation, J. Appl. Phys., 2018, vol. 124, p. 152108.

Wu, L., Liu, H., Li, J., Wang, S., and Wang, X., A multi-level memristor based on Al-doped HfO2 thin film, Nanoscale Res. Lett., 2019, vol. 14, p. 177.

Yin, L., Cheng, R., Wang, Z., Wang, F., Sendeku, M.G., Wen, Y., Zhan, X., and He, J., Two-dimensional unipolar memristors with logic and memory functions, Nano Lett., 2020, vol. 20, no. 6, pp. 4144–4152.

Simanjuntak, F.M., Ohno, T., Chandrasekaran, S., Tseng, T.-Y., and Samukawa, S., Neutral oxygen irradiation enhanced forming-less ZnO-based transparent analog memristor devices for neuromorphic computing applications, Nanotecnology, 2020, vol. 31, p. 26LT01.

Jo, S.H., Chang, T., Ebong, I., Bhadviya, B.B., Mazumder, P., and Lu, W., Nanoscale memristor device as synapse in neuromorphic systems, Nano Lett., 2010, vol. 10, no. 4, pp. 1297–1301.

Prezioso, M., Merrikh-Bayat, F., Hoskins, B.D., Adam, G.C., Likharev, K.K., and Strukov, D.B., Training and operation of an integrated neuromorphic network based on metal-oxide memristors, Nature (London, U.K.), 2015, vol. 521, pp. 61–64.

Guo, J., Wang, L., Liu, Y., Zhao, Z., Zhu, E., Lin, Z., Wang, P., Jia, C., Yang, S., Lee, S.-J., Huang, W., Huang, Y., and Duan, X., Highly reliable low-voltage memristive switching and artificial synapse enabled by Van der Waals integration, Matter, 2020, vol. 2, pp. 965–976.

Hsieh, C.-C., Roy, A., Chang, Y.-F., Shahrjerdi, D., and Banerjee, S.K., A sub-1-volt analog metal oxide memristive-based synaptic device with large conductance change for energy-efficient spike-based computing systems, Appl. Phys. Lett., 2016, vol. 109, p. 223501.

Fan, Z., Xu, H., Wang, Z., Xu, J., Ma, J., and Liu, Y., Reversible alternation between bipolar and unipolar resistive switching in Ag/MoS2/Au structure for multilevel flexible memory, J. Mater. Chem. C, 2018, vol. 6, no. 27, pp. 7195–7200.

Zhang, W., Kong, J.-Z., Cao, Z.-Y., Li, A.-D., Wang, L.-G., Zhu, L., Li, X., Cao, Y.-Q., and Wu, D., Bipolar resistive switching characteristics of HfO2/ TiO2/HfO2 trilayer-structure RRAM devices on Pt and TiN-coated substrates fabricated by atomic layer deposition, Nanoscale Res Lett., 2017, vol. 12, no. 1, p. 393.

Ismaila, M., Rahmania, M.K., Khana, S.A., Choia, J., Hussaina, F., Batoolb, Z., Ranac, A.M., Leea, J., Choa, H., and Kim, S., Effects of Gibbs free energy difference and oxygen vacancies distribution in a bilayer ZnO/ZrO2 structure for applications to bipolar resistive switching, Appl. Surf. Sci., 2019, vol. 498, p. 143833.

Tu, M., Lu, H., Luo, S., Peng, H., Li, S., Ke, Y., Yuan, S., Huang, W., Jie, W., and Hao, J., Reversible transformation between bipolar memory switching and bidirectional threshold switching in 2D layered k-birnessite nanosheets, ACS Appl. Mater. Interfaces, 2020, vol. 12, no. 21, pp. 24133–24140.

Memristors and Memristive Systems, Ronald, T., Ed., New York: Springer, 2014.

Kim, K.M., Zhang, J., Graves, C., Yang, J.J., Choi, B.J., Hwang, C.S., Li, Z., and Williams, R.S., Low-power, self-rectifying, and forming-free memristor with an asymmetric programing voltage for a high-density crossbar application, Nano Lett., 2016, vol. 16, no. 11, pp. 6724–6732.

Prakash, A., Jana, D., Samanta, S., and Maikap, S., Self-compliance-improved resistive switching sing Ir/TaOx/W cross-point memory, Nanoscale Res. Lett., 2013, vol. 8, p. 527.

Xiao, N., Villena, M.A., Yuan, B., Chen, S., Wang, B., Shi, Y., Hui, F., Jing, X., and Lanza, M., Resistive random access memory cells with a bilayer TiO2/SiOx insulating stack for simultaneous filamentary and distributed resistive switching, Adv. Funct. Mater., 2017, p. 1700384.

Kwon, D.-H., Kim, M., Jang, J.H., Jeon, J.M., Lee, M.H., Kim, G.H., Li, X.-S., Park, G.-S., Lee, B., Han, S., Kim, M., and Hwang, C.S., Atomic structure of conducting nanofilaments in TiO2 resistive switching memory, Nat. Nanotech., 2010, vol. 5, pp. 148–153.

Liu, Q., Sun, J., Lv, H., Long, S., Yin, K., Wan, N., Li, Y., Sun, L., and Liu, M., Real-time observation on dynamic growth/dissolution of conductive filaments in oxide-electrolyte-based ReRAM, Adv. Mater., 2012, vol. 24, pp. 1844–1849.

Chen, J.-Y., Hsin, C.-L., Huang, C.-W., Chiu, C.-H., Huang, Y.-T., Lin, S.-J., Wu, W.-W., and Chen, L.-J., Dynamic evolution of conducting nanofilament in resistive switching memories, Nano Lett., 2013, vol. 13, no. 8, pp. 3671–3677.

Lanza, M., Wong, H.-S.P., Pop, E., Ielmini, D., Strukov, D., Regan, B.C., Larcher, L., Villena, M.A., Yang, J.J., Goux, L., Belmonte, A., Yang, Y., Puglisi, F.M., Kang, J., Magyari-Kope, B., et al., Recommended methods to study resistive switching devices, Adv. Electron. Mater., 2018, p. 1800143.

Banerjee, W., Liu, Q., and Hwang, H., Engineering of defects in resistive random access memory devices, J. Appl. Phys., 2020, vol. 127, p. 051101.

Wang, Z., Jiang, H., Jang, M.H., Lin, P., Ribbeb, A., Xia, Q., and Yang, J.J., Electrochemical metallization switching with a platinum group metal in different oxides, Nanoscale, 2016, vol. 8, no. 29, pp. 14023–14030.

Wang, Z.-Q., Ambrogio, S., Balatti, S., Sills, S., Calderoni, A., Ramaswamy, N., and Ielmini, D., Cycling-induced degradation of metal-oxide resistive switching memory (RRAM), in Proceedings of the IEEE International Electron Devices Meeting (IEDM), 2015, pp. 7.6.1–7.6.4.

Gao, B. et al., Modeling of retention failure behavior in bipolar oxide-based resistive switching memory, IEEE Electron Dev. Lett., 2011, vol. 32, no. 3, pp. 276–278.

Wu, X., Cha, D., Bosman, M., Raghavan, N., Migas, D.B., Borisenko, V.E., Zhang, X.-X., Kun, Li., and Pey, K.-L., Intrinsic nanofilamentation in resistive switching, J. Appl. Phys., 2013, vol. 113, p. 114503.

Guo, X., Wang, Q., Lv, X., Yang, H., Sun, K., Yang, D., Zhang, H., Hasegawa, T., and He, D., SiO2/Ta2O5 heterojunction ECM memristor: Physical nature of their low voltage operation with high stability and uniformity, Nanoscale, 2020, vol. 12, no. 7, pp. 4320–4327.

Yoon, J.H., Zhang, J., Ren, X., Wang, Z., Wu, H., Li, Z., Barnell, M., Wu, Q., Lauhon, L.J., Xia, Q., and Yang, J.J., Truly electroforming-free and low-energy memristors with preconditioned conductive tunneling paths, Adv. Funct. Mater., 2017, p. 1702010.

Yoon, J.H., Zhang, J., Lin, P., Upadhyay, Y.P., Liu, Y., Xia, Q., and Yang, J.J., A low-current and analog memristor with Ru as mobile species, Adv. Mater., 2020, vol. 32, no. 9, p. 1904599.

Lv, H., Xu, X., Liu, H., Liu, R., Liu, Q., Banerjee, W., Sun, H., Long, S., Li, L., and Liu, M., Evolution of conductive filament and its impact on reliability issues in oxide-electrolyte based resistive random access memory, Sci. Rep., 2015, vol. 5, p. 7764.

Jiang, H., Han, L., Wang, Z., Jang, M.H., Wu, Q., Barnell, M., Yang, J.J., Xin, H.L., and Xia, Q., Sub-10 nm Ta channel responsible for superior performance of a HfO2 memristor, Sci. Rep., 2016, vol. 6, p. 28525.

Jang, M.H., Agarwal, R., Nukala, P., Choi, D., Johnson, A.T.C., Chen, I.-W., and Agarwal, R., Observing oxygen vacancy driven electroforming in PtTiO2-Pt device via strong metal support interaction, Nano Lett., 2016, vol. 16, no. 4, pp. 2139–2144.

Jung, Y.C., Seong, S., Lee, T., Kim, S.Y., Park, I.-S., and Ahn, J., Improved resistive switching characteristics of a Pt/HfO2/Pt resistor by controlling of anode interface with forming and switching polarity, Appl. Surf. Sci., 2018, vol. 435, pp. 117–121.

Xu, X., Tai, L., Gong, T., Yin, J., Huang, P., Yu, J., Dong, D.N., Luo, Q., Liu, J., Yu, Z., Zhu, X., Wu, X.L., Liu, Q., Lv, H., and Liu, M., 40× retention improvement by eliminating resistance relaxation with high temperature forming in 28 nm RRAM chip, in Proceedings of the IEEE International Electron Devices Meeting (IEDM), 2018, p. 20.1.1–20.1.4.

Hennen, T., Bedau, D., Rupp, J.A.J., Funck, C., Menzel, S., Grobis, M., Waser, R., and Wouters, D.J., Forming-free Mott-oxide threshold selector nanodevice showing s-type NDR with high endurance (>1012 cycles), excellent Vth stability (5%), fast (<10 ns) switching, and promising scaling properties, in Proceedings of the IEEE International Electron Devices Meeting (IEDM), 2018, pp. 37.5.1–37.5.4.

Kumar, A., Das, M., Garg, V., Sengar, B.S., Htay, M.T., Kumar, S., Kranti, A., and Mukherjee, S., Forming-free high-endurance Al/ZnO/Al memristor fabricated by dual ion beam sputtering, Appl. Phys. Lett., 2017, vol. 110, p. 253509.

Yang, J.J., Zhang, M.-X., Strachan, J.P., Miao, F., Pickett, M.D., Kelley, R.D., Medeiros-Ribeiro, G., and Williams, R.S., High switching endurance in TaOx memristive devices, Appl. Phys. Lett., 2010, vol. 97, p. 232102.

Lee, M.-J., Lee, C.B., Lee, D., Lee, S.R., Chang, M., Hur, J.H., Kim, Y.-B., Kim, C.-J., Seo, D.H., Seo, S., Chung, U.-I., Yoo, I.-K., and Kim, K., A fast, high-endurance and scalable non-volatile memory device made from asymmetric Ta2O5–x/TaO2–x bilayer structures, Nat. Mater., 2011, vol. 10, pp. 625–630.

Choi, B.J., Torrezan, A.C., Strachan, J.P., Kotula, P.G., Lohn, A.J., Marinella, M.J., Li, Z., Williams, R.S., and Yan, J.J., High-speed and low-energy nitride memristors, Adv. Funct. Mater., 2016, vol. 26, pp. 5290–5296.

Govoreanu, B., Kar, G.S., Chen, Y.-Y., Paraschiv, V., Kubicek, S., Fantini, A., Radu, I.P., Goux, L., Clima, S., Degraeve, R., Jossart, N., Richard, O., Vandeweyer, T., Seo, K., Hendrickx, P., Pourtois, G., Bender, H., Altimime, L., Wouters, D.J., Kittl, J.A., and Jurczak, M., 10 × 10 nm2 Hf/HfOx crossbar resistive RAM with excellent performance, reliability and low-energy operation, in Proceedings of the International Electron Devices Meeting, Washington, DC, 2011, pp. 31.6.1–31.6.4.

Ahn, C., Jiang, Z., Lee, C.S., Chen, H.Y., Liang, J., Liyanage, L.S., and Wong, H.S.P., 1D selection device using carbon nanotube FETs for high-density cross-point memory arrays, IEEE Trans. Electron Dev., 2015, vol. 62, p. 2197.

Srivastava, S., Thomas, J.P., and Leung, K.T., Programmable, electroforming-free TiOx/TaOx heterojunction-based non-volatile memory devices, Nanoscale, 2019, vol. 11, no. 39, pp. 18159–18168.

Chen, Y.Y., Komura, M., Degraeve, R., Govoreanu, B., Goux, L., Fantini, A., Raghavan, N., Clima, S., Zhang, L., Belmonte, A., Redolfi, A., Kar, G.S., Groeseneken, G., Wouters, D.J., and Jurczak, M., Improvement of data retention in HfO2/Hf 1T1R RRAM cell under low operating current, in Proceedings of the International Electron Devices Meeting, Washington, DC, 2013, pp. 10.1.1–10.1.4.

Traoré, B., Blaise, P., Vianello, E., Grampeix, H., Bonnevialle, A., Jalaguier, E., Molas, G., Jeannot, S., Perniola, L., Desalvo, B., and Nishi, Y., Microscopic understanding of the low resistance state retention in HfO2 and HfAlO based RRAM, in Proceedings of the International Electron Devices Meeting, San Francisco, 2014, pp. 21.5.1–21.5.4.

Calderoni, A., Sills, S., Cardon, C., Faraoni, E., and Ramaswamy, N., Engineering ReRAM for high-density applications, Microelectron. Eng., 2015, vol. 147, pp. 145–150.

Nakamura, R., Toda, T., Tsukui, S., Tane, M., Ishimaru, M., Suzuki, T., and Nakajima, H., Diffusion of oxygen in amorphous Al2O3, Ta2O5, and Nb2O5, J. Appl. Phys., 2014, vol. 116, p. 033504.

O’Hara, A., Bersuker, G., and Demkov, A.A., Assessing hafnium on hafnia as an oxygen getter, J. Appl. Phys., 2014, vol. 115, p. 183703.

Boolchand, P. and Bresser, W., Mobile silver ions and glass formation in solid electrolytes, Nature (London, U.K.), 2001, vol. 410, pp. 1070–1073.

Kozicki, M.N., Mira, P., and Mitkova, M., Nanoscale memory elements based on solid-state electrolytes, IEEE Trans. Nanotech., 2005, vol. 4, pp. 331–338.

Kwon, D.H., Kim, K.M., Jang, J.H., Jeon, J.M., Lee, M.H., Kim, G.H., Li, X.-S., Park, G.-Su, Lee, B., Han, S., Kim, M., and Hwang, C.S., Atomic structure of conducting nanofilaments in TiO2 resistive switching memory, Nat. Nanotechnol., 2010, vol. 5, pp. 148–153.

Yang, Y., Gao, P., Gaba, S., Chang, T., Pan, X., and Lu, W., Observation of conducting filament growth in nanoscale resistive memories, Nat. Commun., 2012, vol. 3, pp. 732–735.

Huang, P., Gao, B., Chen, B., Zhang, F., Liu, L., Du, G., Kang, J., and Liu, X., Stochastic simulation of forming, SET and RESET process for transition metal oxide-based resistive switching memory, in Proceedings of the International Conference on Simulation of Semiconductor Processes and Devices SISPAD, 2012, pp. 312–315.

Huang, P., Liu, X.Y., Li, W.H., Deng, Y.X., Chen, B., Lu, Y., Gao, B., Zeng, L., Wei, K.L., Du, G., Zhang, X., and Kang, J.F., A physical based analytic model of RRAM operation for circuit simulation, in Proceedings of the International Electron Devices Meeting, San Francisco, CA, 2012, pp. 26.6.1–26.6.4.

Strukov, D.B., Borghetti, J.L., and Williams, R.S., Coupled ionic and electronic transport model of thin-film semiconductor memristive behavior, Small, 2009, vol. 5, pp. 1058–1063.

Noman, M., Jiang, W., Salvador, P.A., Skowronski, M., and Bain, J.A., Computational investigations into the operating window for memristive devices based on homogeneous ionic motion, Appl. Phys. A, 2011, vol. 102, pp. 877–883.

Kalaev, D. and Riess, I., Examining the crossing of I–V curves in devices based on mixed-ionic-electronic-conductors, Solid State Ionics, 2014, vol. 262, pp. 883–888.

Kalaev, D., Yalon, E., and Riess, I., On the direction of the conductive filament growth in valence change memory devices during electroforming, Solid State Ionics, 2015, vol. 276, pp. 9–17.

Tang, S., Tesler, F., Marlasca, F.G., Levy, P., Dobrosavljevic, V., and Rozenberg, M., Shock waves and commutation speed of memristors, Phys. Rev. X, 2016, vol. 6, pp. 11028-1–16.

Larentis, S., Nardi, F., Balatti, S., Gilmer, D.C., and Ielmini, D., Resistive switching by voltage-driven ion migration in bipolar RRAM. Part II: Modeling, IEEE Trans. Electron Dev., 2012, vol. 59, pp. 2468–2475.

Nardi, F., Balatti, S., Larentis, S., Gilmer, D.C., and Ielmini, D., Complementary switching in oxide-based bipolar resistive-switching random memory, IEEE Trans. Electron Dev., 2013, vol. 60, pp. 70–77.

Kim, S., Choi, S., and Lu, W., Comprehensive physical model of dynamic resistive switching in an oxide memristor, ACS Nano, 2014, vol. 8, pp. 2369–2376.

Marchewka, A., Waser, R., and Menzel, S., Physical simulation of dynamic resistive switching in metal oxides using a schottky contact barrier model, in Proceedings of the International Conference on Simulation of Semiconductor Processes and Devices (SISPAD), Washington, DC, USA, Sept. 9–11, 2015, pp. 297–300.

Marchewka, A., Roesgen, B., Skaja, K., Du, H., Jia, C.L., Mayer, J., Rana, V., Waser, R., and Menzel, S., Nanoionic resistive switching memories: On the physical nature of the dynamic reset process, Adv. Electron. Mater., 2016, vol. 2, p. 1500233-1–13.

Marchewka, A., Waser, R., and Menzel, S., Physical modeling of the electroforming process in resistive-switching devices, in Proceedings of the International Conference on Simulation of Semiconductor Processes and Devices (SISPAD), Kamakura, Japan, September 7–9, 2017, pp. 133–136.

Wang, L.-G., Qian, X., Cao, Y.-Q., Cao, Z.-Y., Fang, G.-Y., Li, A.-D., and Wu, D., Excellent resistive switching properties of atomic layer-deposited Al2O3/HfO2/Al2O3 trilayer structures for non-volatile memory applications, Nanoscale Res. Lett., 2015, vol. 10, p. 135.

Huang, X., Li, Y., Li, H., Xue, K., Wang, X., and Miao, X., Forming-free, fast, uniform, and high endurance resistive switching from cryogenic to high temperatures in W/AlOx/Al2O3/Pt bilayer memristor, IEEE Electron Dev. Lett., 2020, vol. 41, pp. 549–552.

Kim, W., Hardtdegena, A., Rodenbüchera, C., Menzela, S., Woutersb, D.J., Hoffmann-Eiferta, S., Bucaa, D., Wasera, R., and Rana, V., Forming-free metal-oxide ReRAM by oxygen ion implantation process, in Proceedings of the IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, 2016, pp. 4.4.1–4.4.4.

Wei, Z., Takagi, T., Kanzawa, Y., Katoh, Y., Ninomiya, T., Kawai, K., Muraoka, S., Mitani, S., Katayama, K., Fujii, S., Miyanaga, R., Kawashima, Y., Mikawa, T., Shimakawa, K., and Aono, K., Demonstration of high-density RERAM ensuring 10-year retention at 85°C based on a newly developed reliability model, in Proceedings of the International Electron Devices Meeting, 2011, p. 31.4.1–31.4.4.

Wei, Z., Takagi, T., Kanzawa, Y., Katoh, Y., Ninomiya, T., Kawai, K., Muraoka, S., Mitani, S., Katayama, K., Fujii, S., Miyanaga, R., Kawashima, Y., Mikawa, T., Shimakawa, K., and Aono, K., Retention model for high-density ReRAM, in Proceedings of the 4th IEEE International Memory Workshop, 2012, pp. 1–4.

Chen, B., Lu, Y., Gao, B., Fu, Y.H., Zhang, F.F., Huang, P., Chen, Y.S., Liu, L.F., Liu, X.Y., Kang, J.F., Wang, Y.Y., Fang, Z., Yu, H.Y., Li, X., Wang, X.P., Singh, N., Lo, G.Q., and Kwon, D.L., Physical mechanisms of endurance degradation in TMO-RRAM, in Proceedings of the International Electron Devices Meeting, Washington, DC, 2011, pp. 12.3.1–12.3.4.

Fantini, A., Goux, L., Redolfi, A., Degraeve, R., Kar, G., Chen, Y.Y., and Jurczak, M., Lateral and vertical scaling impact on statistical performances and reliability of 10 nm TiN/Hf(Al)O/Hf/TiN RRAM devices, in Proceedings of the Symposium on VLSI Technology (VLSI-Technology), Honolulu, HI, 2014, pp. 1–2.

Lee, H.Y., Chen, Y.S., Chen, P.S., Gu, P.Y., Hsu, Y.Y., Wang, S.M., Liu, W.H., Tsai, C.H., Sheu, S.S., Chiang, P.C., Lin, W.P., Lin, C.H., Chen, W.S., Chen, F.T., Lien, C.H., and Tsai, M.-J., Evidence and solution of over-reset problem for HfOx based resistive memory with sub-ns switching speed and high endurance, in Proceedings of the International Electron Devices Meeting, San Francisco, CA, 2010, pp. 19.7.1–19.7.4.

Liu, C.-F., Tang, X.-G., Wang, L.-Q., Tang, H., Jiang, Y.-P., Liu, Q.-X., Li, W.-H., and Tang, Z.-H., Resistive switching characteristics of HfO2 thin films on mica substrates prepared by sol-gel process, Nanomaterials (Basel), 2019, no. 8, p. 1124.

Ninomiya, T., Takagi, T., Wei, Z., Muraoka, S., Yasuhara, R., Katayama, K., Ikeda, Y., Kawai, K., Kato, Y., Kawashima, Y., Ito, S., Mikawa, T., Shimakawa, K., and Aono, K., Conductive filament scaling of TaOx bipolar ReRAM for long retention with low current operation, in Proceedings of the Symposium on VLSI Technology (VLSIT), Honolulu, HI, USA, 2012, pp. 73–74.

Chen, N.H., Zheng, Z.W., Cheng, C.H., and Yeh, F.S., Sub-micro watt resistive memories using nano-crystallized aluminum oxynitride dielectric, Appl. Phys. A, 2014, vol. 116, pp. 575–579.

Srivastava, S., Defect-rich size-selected nanoclusters and nanocrystalline films of titanium (IV) oxide and tantalum (IV) oxide for efficient photocatalyst and electroforming-free memristor applications, Theses, Waterloo, Ontario, Canada, 2016. http://hdl.handle.net/10012/10487.

Balatti, S., Ambrogio, S., Wang, Z.-Q., Sills, S., Calderoni, A., Ramaswamy, N., and Ielmini, D., Pulsed cycling operation and endurance failure of metal-oxide resistive (RRAM), in Proceedings of the IEEE International Electron Devices Meeting, San Francisco, CA, 2014, pp. 14.3.1–14.3.4.

Chen, Y.Y., Degraeve, R., Clima, S., Govoreanu, B., Goux, L., and Fantini, A., Understanding of the endurance failure in scaled HfO2-based 1T1R RRAM through vacancy mobility degradation, in Proceedings of the IEEE International Electron Devices Meeting, San Francisco, CA, 2012, pp. 20.3.1–20.3.4.

Chai, Z., Ma, J., Zhang, W., Govoreanu, B., Simoen, E., Zhang, J.F., Ji, Z., Gao, R., Groeseneken, G., and Jurczak, M., RTN-based defect tracking technique: Experimentally probing the spatial and energy profile of the critical filament region and its correlation with HfO2 RRAM switching operation and failure mechanism, in Proceedings of the IEEE Symposium on VLSI Technology, 2016, pp. 1–2.

Kim, K.-H., Jo, S.H., Gaba, S., and Lu, W., Nanoscale resistive memory with intrinsic diode characteristics and long endurance, Appl. Phys. Lett., 2010, vol. 96, p. 053106.

Chen, Y.Y., Govoreanu, B., Goux, L., Degraeve, R., Fantini, A., Kar, G., Wouters, D., Groeseneken, G., Kittl, J.A., and Jurczak, M., Balancing SET/RESET pulse for endurance in 1T1R bipolar RRAM, IEEE Trans. Electron Dev., 2012, vol. 59, p. 3243.

Chen, C.Y., Goux, L., Fantini, A., Clima, S., Degraeve, R., Redolfi, A., Chen, Y.Y., Groeseneken, G., and Jurczak, M., Endurance degradation mechanisms in TiN/Ta2O5/Ta resistive random-access memory cells, Appl. Phys. Lett., 2015, vol. 106, p. 053501.

Dongale, T.D., Khot, K.V., Mohite, S.V., Desai, N.K., Shinde, S.S., Moholkar, A.V., Rajpure, K.Y., Bhosale, P.N., Patil, P.S., Gaikwad, P.K., and Kamat, R.K., Investigating reliability aspects of memristor based RRAM with reference to write voltage and frequency, arXiv: 1602.01947, 2016. https://arxiv.org/abs/1602.01947.

Merced-Grafals, E.J., Davila, N., Ge, N., Williams, R.S., and Strachan, J.P., Repeatable, accurate, and high speed multi-level programming of memristor 1T1R arrays for power efficient analog computing applications, Nanotecnology, 2016, vol. 27, p. 365202.

Wang, G., Long, S., Yu, Z., Zhang, M., Li, Y., Xu, D., Lv, H., Liu, Q., Yan, X., Wang, M., Xu, X., Liu, H., Yang, B., and Liu, M., Impact of program/erase operation on the performances of oxide-based resistive switching memory, Nanoscale Res. Lett., 2015, vol. 10, p. 39.

Kim, K.M., Yang, J.J., Strachan, J.P., Grafals, E.M., Ge, N., Melendez, N.D., Li, Z., and Williams, R.S., Voltage divider effect for the improvement of variability and endurance of TaOx memristor, Sci. Rep., 2016, vol. 6, p. 20085.

Ravi, V. and Prabaharan, S.R.S., Fault tolerant adaptive write schemes for improving endurance and reliability of memristor memories, Int. J. Electron. Commun., 2018, vol. 94, pp. 392–406.

Wang, C., Wu, H., Gao, B., Zhang, T., Yang, Y., and Qian, H., Conduction mechanisms, dynamics and stability in ReRAMs, Microelectron. Eng., 2018, vols. 187–188, pp. 121–133.

Kamarozaman, N.S., Shamsul, M.U., Herman, S.H., and Abdullah, W.F.H., Effect of oxygen flow rate on the memristive behavior of reactively sputtered TiO2 thin films, Adv. Mater. Res., 2014, vol. 1024, p. 64.

Kim, M., Yoo, K., Jeon, S.-P., Park, S.K., and Kim, Y.-H., The effect of multi-layer stacking sequence of TiOx active layers on the resistive-switching characteristics of memristor devices, Micromachines (Basel), 2020, vol. 11, no. 2, p. 154.

Wei, Z., Kanzawa, Y., Arita, K., Katoh, Y., Kawai, K., Muraoka, S., Mitani, S., Fujii, S., Katayama, K., Iijima, M., Mikawa, T., Ninomiya, T., Miyanaga, R., Kawashima, Y., Tsuji, K., et al., Highly reliable TaOx ReRAM and direct evidence of redox reaction mechanism, in Proceedings of the International Electron Devices Meeting, 2008.

Sharath, S.U., Vogel, S., Molina-Luna, L., Hildebrandt, E., Wenger, C., Kurian, J., Duerrschnabel, M., Niermann, T., Niu, G., Calka, P., Lehmann, M., Kleebe, H.-J., Schroeder, T., and Alf, L., Control of switching modes and conductance quantization in oxygen engineered HfOx based memristive devices, Adv. Funct. Mater., 2017, vol. 27, p. 1700432.

Yin, X., Wang, Y., Chang, T.-H., Zhang, P., Li, J., Xue, P., Long, Y., Shohet, J.L., Voyles, P.M., Ma, Z., and Wang, X., Memristive behavior enabled by amorphous-crystalline 2D oxide heterostructure, Adv. Mater., 2020, p. 2000801.

Clima, S., Chen, Y.Y., Degraeve, R., Mees, M., Sankaran, K., Govoreanu, B., Jurczak, M., de Gendt, S., and Pourtois, G., First-principles simulation of oxygen diffusion in HfOx: Role in the resistive switching mechanism, Appl. Phys. Lett., 2012, vol. 100, p. 133102.

Stathopoulos, S., Michalas, L., Khiat, A., Serb, A., and Prodromakis, T., An electrical characterisation methodology for benchmarking memristive device technologies, Sci. Rep., 2019, vol. 9, p. 19412.

Valov, I., Linn, E., Tappertzhofen, S., Schmelzer, S., Hurk, J., Lentz, F., and Waser, R., Nanobatteries in redox-based resistive switches require extension of memristor theory, Nat. Commun., 2013, vol. 4, p. 1771.

Zhao, X., Zhang, X., Shang, D., Wu, Z., Xiao, X., Chen, R., Tang, C., Liu, J., Li, W., Lv, H., Jiang, C., Liu, Q., and Liu, M., Uniform, fast, and reliable LixSiOy-based resistive switching memory, IEEE Electron. Dev. Lett., 2019, vol. 40, pp. 554–557.

Tsai, T.-L., Chang, H.-Y., Lou, J.J.-C., and Tseng, T.-Y., A high performance transparent resistive switching memory made from ZrO2/AlON bilayer structure, Appl. Phys. Lett., 2016, vol. 108, p. 153505.

Chang, C.-F., Chen, J.-Y., Huang, G.-M., Lin, T.-Y., Tai, K.-L., Huang, C.-Y., Yeh, P.-H., and Wu, W.-W., Revealing conducting filament evolution in low power and high reliability Fe3O4/Ta2O5 bilayer RRAM, Nano Energy, 2018, vol. 53, pp. 871–879.

Woo, J., Moon, K., Song, J., Lee, S., Kwak, M., Park, J., and Hwang, H., Improved synaptic behavior under identical pulses using AlOx/HfO2 bilayer RRAM array for neuromorphic systems, IEEE Electron Dev. Lett., 2016, vol. 37, pp. 994–997.

Park, K. and Lee, J.S., Reliable resistive switching memory based on oxygen-vacancy controlled bilayer structures, RSC Adv., 2016, vol. 6, pp. 21736–21741.

Akbari, M., Kim, M.K., Kim, D., and Lee, J.S., Reproducible and reliable resistive switching behaviors of AlOx/HfOx bilayer structures with Al electrode by atomic layer deposition, RSC Adv., 2017, vol. 7, pp. 16704–16708.

Sadaf, S.M., Liu, X., Son, M., Park, S., Choudhury, S.H., Cha, E., Siddik, M., Shin, J., and Hwang, H., Highly uniform and reliable resistance switching properties in bilayer WOx/NbOx RRAM devices, Phys. Status Solidi, 2012, vol. 209, pp. 1179–1183.

Huang, C.Y., Huang, C.Y., Tsai, T.L., Lin, C.A., and Tseng, T.-Y., Switching mechanism of double forming process phenomenon in ZrOx/HfOy bilayer resistive switching memory structure with large endurance, Appl. Phys. Lett., 2014, vol. 104, p. 062901.

Yang, Y., Choi, S., and Lu, W., Oxide heterostructure resistive switching, Nano Lett., 2013, vol. 13, p. 2908.

Ismail, M., Hashmi, A., Rana, A.M., and Kim, S., Eradicating negative-set behavior of TiO2-based devices by inserting an oxygen vacancy rich zirconium oxide layer for data storage applications, Nanotecnology, 2020, vol. 31, no. 32, p. 325201.

Hui, F., Grustan-Gutierrez, E., Long, S., Liu, Q., Ott, A., Ferrari, A., and Lanza, M., Graphene and related materials for resistive random access memories, Adv. Electron. Mater., 2017, vol. 3, p. 1600195.

Ye, C., Deng, T., Zhang, J., Shen, L., He, P., Wei, W., and Wang, H., Enhanced resistive switching performance for bilayer HfO2/TiO2 resistive random access memory, Semicond. Sci. Technol., 2016, vol. 31, p. 105005.

Li, Y., Li, X., Fu, L., Chen, R., Wang, H., and Gao, X., Effect of interface layer engineering on resistive switching characteristics of ZrO2-based resistive switching devices, IEEE Trans. Electron Dev., 2018, vol. 65, no. 12, pp. 5390–5394.

Liu, J., Yang, H., Ma, Z., Chen, K., Zhang, X., Huang, X., and Oda, S., Characteristics of multilevel storage and switching dynamics in resistive switching cell of Al2O3/HfO2/Al2O3 sandwich structure, J. Phys. D: Appl. Phys., 2018, vol. 51, p. 025102.

Zhu, Y.B., Zheng, K., Wu, X., and Ang, L.K., Enhanced stability of filament-type resistive switching by interface engineering, Sci. Rep., 2017, vol. 7, p. 43664.

Goux, L., Fantini, A., Redolfi, A., Chen, C.Y., Shi, F.F., Degraeve, R., Chen, Y.Y., Witters, T., Groeseneken, G., and Jurczak, M., Role of the Ta scavenger electrode in the excellent switching control and reliability of a scalable low-current operated TiN/Ta2O5/Ta RRAM device, in Proceedings of the 2014 Symposium on VLSI Technology (VLSI-Technology), Honolulu, HI, 2014, pp. 1–2.

Guo, Y. and Robertson, J., Materials selection for oxide-based resistive random access memories, Appl. Phys. Lett., 2014, vol. 105, p. 223516.

Jiang, H. and Stewart, D.A., Enhanced oxygen vacancy diffusion in Ta2O5 resistive memory devices due to infinitely adaptive crystal structure, J. Appl. Phys., 2016, vol. 119, p. 134502.

Lee, M.-J., Park, G.-S., Seo, D.H., Kwon, S.M., Lee, H.-J., Kim, J.-S., Jung, M., You, C.-Y., Lee, H., Kim, H.-G., Pang, S.-B., Seo, S., Hwang, H., and Park, S.K., Reliable multivalued conductance states in TaOx memristors through oxygen plasma-assisted electrode deposition with in situ-biased conductance state transmission electron microscopy analysis, ACS Appl. Mater. Interfaces, 2018, vol. 10, no. 35, pp. 29757–29765.

Funding

This work was carried out as part of program no. 066-2019-0004 of the Ministry of Science and Education of the Russian Federation and supported by the Russian Foundation for Basic Research, project no. 18-37-20076.

Author information

Authors and Affiliations

Corresponding authors

Ethics declarations

The authors declare that they have no conflict of interest.

Rights and permissions

Open Access. This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made. The images or other third party material in this article are included in the article’s Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Fadeev, A.V., Rudenko, K.V. To the Issue of the Memristor’s HRS and LRS States Degradation and Data Retention Time. Russ Microelectron 50, 311–325 (2021). https://doi.org/10.1134/S1063739721050024

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1134/S1063739721050024