Abstract

A new technological approach is needed for the development of emerging electronic components and systems within the Internet of Things (IoT) era. New advancements and innovations are required in architectural design and hybrid systems heterogeneous integration to address the challenge of widespread IoT deployment, its power demands and sustainability. Hybrid chips are one of the emerging technologies that can help overcome the current limitations in terms of energy consumption, performance and sustainability that could shape the future of electronic systems for targeted applications. Hybrid chips combine different materials and manufacturing technologies on the same substrate or package using advanced flexible heterogeneous integration techniques, with the focus of merging the advantages of each unit or technology toward enhanced performance and new levels of emerging functionalities. The categorization of hybrid chips spans across rigid hybrid chips that follow a multi-chiplet approach, semi-flexible chips that integrate flexible units with semi-rigid ones such as thinned silicon integrated circuits, and lastly, flexible chips in which all components are inherently flexible. This perspective article analyzes technical challenges that arise concerning the development of sustainable materials and processing technologies, complex heterogeneous integration, as well as advanced packaging architectures, standardization, and reliability testing. The economic implications for the semiconductor technology transition to hybrid chips is presented in terms of manufacturing costs, economic feasibility, and market readiness. Key insights and future application opportunities are provided, while recent advancements in the field are summarized. This perspective article suggests that by addressing these challenges, hybrid chips have the potential to transform electronic components and systems across a wide range of industries and use case scenario. The advancement of hybrid chip technologies by enhancing the collaboration between industry and academia as well as policymakers will be a crucial part in the realization of required sustainability goals within the worldwide Chips Act initiative, while ensuring the technological progress has the right balance between improved performance and sustainability.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Hybrid chips as a paradigm shift toward sustainable electronics

New materials, advanced manufacturing, and research and development (R&D) on semiconductors have propelled world's economic growth enhancing citizens prosperity and comfort. Semiconductor chips, electronic components and systems are at the center of this technological innovation. R&D in semiconductor technologies has supported the abrupt development of human civilization reported the last 60 years. Semiconductors have become so ubiquitous in technological innovations that they are mistakenly considered by most people as a commodity. The COVID-19 pandemic and chip supply problems have focused attention on this key technology, whose market is expected to exceed $1 trillion USD by 2030. Only in 2021, the semiconductor industry delivered a record 1.15 trillion chips, with global revenues exceeding $500 billion, and dozens of new chip designs entering the market. However, continuous innovation in design and production is essential to keep semiconductor goods competitive, making this one of the most research-intensive sectors. It is estimated that 20% of revenue in the semiconductor value chain is spent on R&D. Many more innovations will be driving the digital transformation in the next decade.

However, conventional silicon chips are lacking in one area: sustainability. The high manufacturing temperatures and costs associated to silicon chips fabrication and the creation of electronic wastes (e-wastes) due to their limited recyclability, is not just a drawback for business but also harmful for the environment. While the semiconductor supply chain is working to achieve net-zero carbon emissions, the sector is still a long way from meeting the emissions targets outlined in the United Nations' 2016 Paris Agreement. A co-optimization strategy should be pursued in order to enhance performance, safety and security while minimizing resources consumption, costs, and environmental impact. This approach should handle associated environmental issues such as greenhouse gas emissions, human and environmental toxicity [1], while concepts such as the use of sustainable materials and fabrication processes, and assuring minimal environmental footprint throughout the device life cycle should be prioritized.

Customers nowadays demand intelligence in every object connected within the Internet of Things (IoT) network, however this requires IoT edge data processing that urges for better and more energy efficient hardware performance. To handle the data deluge in IoT, new technologies such as artificial intelligence (AI) and machine learning (ML) are required for resource-efficient deployment of smart, sustainable IoT systems. The majority of IoT devices are based on conventional silicon chips that integrate sensors, actuators and communication modules, microcontrollers, power management and data processing units. These chips are fabricated using inorganic materials processed on silicon substrates, which makes recycling challenging thus these chips are potentially harmful for the environment if not retrieved. Since conventional scaling of CMOS technology is no longer viable, industry must now innovate across all elements of system design for IoT devices to keep Moore's law at pace within a sustainable way. New advancements and innovations are required on materials, processes, chips’ architectural design and hybrid systems heterogeneous integration to address the challenges of sustainable IoT widespread deployment [2].

Hybrid chips are one of the emerging technologies that can help to overcome the current limitations in terms of energy consumption, sustainability, and performance that could shape the future of electronic systems for targeted applications (Fig. 1). Hybrid chips combine different materials and manufacturing technologies on the same substrate or package through advanced flexible, heterogeneous integration techniques with the focus of merging the advantages of each unit or technology toward enhanced performance and new levels of emerging functionalities. The categorization of the field of hybrid chips spans across (a) rigid hybrid chips that follow a multi-chiplet approach, (b) semi-flexible hybrid chips that integrate flexible units (evaporated or printed on flexible substrates) with semi-rigid ones such as thinned silicon integrated circuits (ICs), and lastly (c) flexible hybrid chips in which all components are inherently flexible. Figure 1 illustrates the overall structure of the perspective manuscript and depicts how the different topics are inter-related. Specifically, Fig. 1 depicts an overview of hybrid chips categories indicating the main features of each technology addressing sustainability (Sect. 2), and integration/packaging technologies (Sect. 3). The manuscript also addresses the opportunities (Sect. 4) and challenges (Sect. 5) that should be addressed by each technology. Key recent advancements of hybrid chips (Sect. 6) are also presented toward market applications. It is noted that semi-flexible (category b) and flexible (category c) hybrid circuits could adopt a multi-chiplet architecture incorporating therefore technological inputs of category a (Figs. 1 and 2).

Illustration of the overall structure of this perspective article. The core differences between rigid, semi-flexible and flexible hybrid chips are presented addressing key technological pillars, namely sustainability aspects (Sect. 2) and integration/packaging issues (Sect. 3), while opportunities (Sect. 4) and challenges (Sect. 5) are compared focusing on market exploitation (Sect. 6)

A schematic of a sophisticated flexible or semi-flexible package constituting a system of various SiPs. Part A: Targeting self-powered (autonomous) wireless devices, various types of ‘ambient’ energy supply from energy harvesting sources (solar, mechanical, RF, water, etc.) and associated energy storage units (supercapacitors, batteries) should be integrated, while developing micro-power management solutions for miniaturized systems operation. Part B: Multi-chiplet integration is the solution to the yield issues in larger chips, while facilitates splitting the design and implementing sub-systems into separate smaller dies with enhanced customization and lowered costs. Part C: Peripheral circuits to handle data processing enabled by either thinned Si IC including amplifiers, filters analog to digital converters or flexible units. Part D: Printed displays, antennas and sensors contribute to IoT devices communication. Interconnections between the various SiP and chips are realized by printing, vacuum techniques, laser technologies and flexible integration technologies

Regarding category (a) of hybrid chips, recent advances have been reported such as “multi-die” or “multi-chiplets” design approach toward “System-on-a-Chip” (SoC) integration and recently "System-in-a-Package" (SiP) approach. [3] The SiP approach offers significant flexibility, as chiplets can be mixed and matched depending on the application, leading to a scalable and customizable solution. Reduced system-level costs are offered by a multi-chiplet approach as a result of enhancing silicon yields while minimizing waste during chip manufacturing. Specifically, by using chiplets, reduced costs can be also achieved by producing high volumes of standardized chiplets and then combining them in various configurations, while an enhanced performance and extended functionality can be also enabled by this customization potential. There are at least two chiplet designs, namely chip partition and integration (driven by cost and technology optimization) and chip split and integration (driven by cost and yield) [3]. To make multi-chiplet designs viable, significant progress has been made in interconnect technologies, including development of inter-chiplet communication protocols, high-bandwidth interconnects, and efficient packaging techniques.

Heterogeneous integration is a critical step toward SiP implementation paving the way for high-performance chips that combine complementary components with distinct functions (such as data processing and I/O). This approach can be expanded also to systems that include units manufactured using different manufacturing processes including printed electronics and silicon technology [i.e., hybrid chips category (b)], or even systems developed initially on different substrates and heterogeneously integrated onto the same package. The heterogeneous integration approach can be extended to the board level, allowing many SiPs to be integrated on the same printed circuit board (PCB) in 2D, 2.5D, or 3D dimensions [2, 4]. Specifically, 2.5D packaging has become popular, in which chips are placed side-by-side on an interposer. This allows for high-density interconnects between chips avoiding complexities of 3D stacking. To this end, new materials like graphene, carbon nanotubes, and advanced polymers in packaging are required to improve electrical performance and heat dissipation in hybrid chips [5].

Hybrid chips that combine flexible electronics and silicon ICs, thus category (b) of hybrid circuits, are termed as semi-flexible hybrid chips (Fig. 2). These electronics have gained attention recently towards applications that require chips with large-area form factors, high-speed connectivity, low data latency, enhanced functionality, conformability, and low-cost fabrication. This is a very powerful and adaptable technology compatible with a wide range of applications in IoT technology [6,7,8,9]. Specifically, printed units provide the flexibility and scalability necessary for sensing and actuating, whereas semi-rigid silicon ICs are employed for implementing complex functions such as intense data processing and communication. Thinned Si IC can be mounted on flexible substrates using conventional manufacturing and assembly procedures such as pick-and-place technique, or even be integrated utilizing direct transfer printing [9]. It is expected that this novel hybrid chips approach will redefine how products are conceptualized, built, and manufactured overcoming technological challenges opening the path for new market opportunities across the whole value chain of the semiconductor ecosystem.

The third type of hybrid chips, namely category (c), addresses flexible hybrid chips in which all components are inherently flexible, being either printed or evaporated (Figs. 1 and 2). The best examples of this type of hybrid chips have been demonstrated by Pragmati IC company in collaboration with ARM industry. The team used Pragmatic's innovative commercial manufacturing approach, known as 'fab-in-a-box', along with its associated FlexLogIC foundry services. This approach has the potential for the development of flexible processing engines addressing IoT edge computing that do not rely on semi-rigid silicon-based components [10]. Such flexible hybrid chips could overcome key hurdles on developing energy efficient IoT devices with reduced cost while increasing sustainability since they rely on manufacturing at low temperatures with minimum wastes of resources [11, 12].

In this perspective, we firstly address in Sect. 2 the need to provide power for billions of IoT devices operation and address the energy demands for this big data processing. Moreover, we argue that the high temperature manufacturing of conventional silicon-based chips together with their limited recyclability and reconfigurability results in e-wastes, which have significant negative environmental impact. A technological transition from single SoC towards hybrid multi-chiplet based architectures is required to overcome the aforementioned issues (Sect. 3.1) implementing a heterogeneous integration and novel packaging of different SiP sub-systems (Sect. 3.2). Future opportunities and required steps towards enhancing the functionality and performance offered by hybrid chips are given toward novel applications including wearables and edge computing (Sect. 4). Challenges that should be addressed are discussed (Sect. 5) suggesting ways to overcome technical difficulties on materials and processes development level, heterogeneous integration, standardization, and reliability testing, in line with sustainability and circular economy plans. Emphasis is given to the economic implications for the required technology transition to hybrid chips discussing manufacturing costs, economic feasibility and market readiness (Sect. 5.4). Recent literature advancements are analyzed covering rigid hybrid chips enabled by heterogeneous integration and packaging technologies, demonstrations based on semi-flexible hybrid chips and finally recent highlights on novel flexible hybrid chips including commercial products (Sect. 6). The innovation potential and the market perspective of hybrid chips is described in Sect 7, pointing out that there is a need for developing European research infrastructures offering both rigid and flexible manufacturing facilities in a single place, while special focus should be given on hybrid integration and packaging technologies of hybrid chips (either rigid or flexible).

2 Addressing the manufacturing environmental impact and the power demands of internet of things technology

The world is facing multiple challenges related to climate change, as a result of the extended use of electronic gadgets and growing dependence on non-recyclable critical raw materials (CRM). The ever-increasing consumer demand for electronic devices is contributing to the world’s fastest-growing waste stream, known as e-waste [13]. The ever-shortening lifespan of smart devices has created a “tsunami of e-waste,” as the UN has characterized it, with 53.6 million tons accumulated each year, only 20% of which undergo formal e-recycling [14]. The global e-waste monitoring for 2020 shows that we are producing e-waste in the range of 7.3 kg per capita, which is expected to double every 5 years if no measures are taken. This should be reversed by adopting a “green technology” mindset, driving our prosperity for sustainability without sacrificing our digital growth. In addition to developing strategies to manage such e-waste, further challenges should be identified concerning the capability of manufacturing electronics within a holistic eco-design strategy [15]. The focus should be on low power consumption during product manufacturing and operation, while significantly lowering material usage compared to conventional processes. A sustainable approach should be adopted using components and processes based on abundant, recyclable materials with a much smaller environmental footprint towards a circular economy, as for example suggested within “Green Deal for Europe” initiative [16], positively impacting environmental decarbonization.

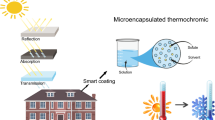

A novel technology of «responsible electronics» is required considering the Safe and Sustainable by Design (SSbD) framework and eco-design principles, towards producing systems able to be reused, recovered, and recycled thus going beyond silicon chips. This approach should be based on energy efficient manufacturing processes, requiring less CRM than conventional techniques to achieve the required circularity. These «responsible electronics» can be integrated into IoT applications requiring shorter device's lifespan and long-term usefulness,[17]while they should contain sustainable components with increased versatility to allow lower production cost and almost zero environmental impact. The world dependency on CRM, the high energy demand of semiconductor processing and the predicted massive e-waste force communities to set a new paradigm in the design of electronic products. Holistic approaches such as the SSbD and eco-design for sustainable products are instrumental to overcome these challenges. The combination of these strategies should thoroughly focus on safety (intrinsic hazard, occupational, environmental and consumer’s safety) and sustainability aspects across the full product’s life cycle stages such as raw materials acquisition, manufacturing, usage, and fate. Overall, sustainability plan for IoT applications should enhance the product’s design to maximize safety, minimize the use of resources and energy consumption, reduce carbon footprint and waste, increase durability and recyclability while keeping performance high.

The purpose of the IoT is to support and create an intelligent environment by incorporating a distributed network of wireless sensors connected to the cloud, and humans as well, while providing decision-making functions to these objects. As data volume of IoT systems expands exponentially [18], the need to address power consumption during operation and big data processing becomes a severe issue urging for development of novel systems with high flexibility, efficiency and speed to enable a long-term viability of such systems. Technologies implementing autonomous smart devices into an IoT network will lead to 79.4 zettabytes of data in 2025.[19]IoT edge devices[18]are usually not capable of data processing and rely on energy-consuming and high-latency cloud communication. Furthermore, the inherent bottlenecks of Si-based CMOS processors due to their energy inefficient von Neumann’s computation architecture [20], lead thus to unsustainable energy cost [21]. Most Si-based IoT devices depend on a battery as their power source, therefore, fail to meet the design goals of lifetime power supply, low-cost, and reliable sensing, demanding radically new device and computing principles. The parallel energy harvesting and edge computing features [22] in the same chip would enable battery-less IoT edge devices with decentralized data processing implemented directly on the edge device leading to a positive environmental, societal, and economic impact. Hence, the deployment of IoT technology will rely on a sustainable, low-cost chip manufacturing while developing self-powered systems.

The development of new innovative technologies based on IoT devices require therefore the cooperation of many complementary disciplines and research fields (Fig. 3). Novel IoT chips should demonstrate efficient on-chip data processing and multiple sensing functions, promising thus the implementation of IoT-edge devices with ultra-low power consumption. Hybrid chips are a potential candidate to drive this sustainable development offering several opportunities for expanding the available chips functionalities across a plethora of applications. Hybrid chips integrate dissimilar materials and technologies that would otherwise be difficult to be interconnected without developing specific heterogeneous integration approaches. 3D deployment and integration methods for the chip [23], module, and system level can contribute significantly to lowering further the manufacturing costs of components and systems. This emerging path leads to more versatile and efficient systems due to the ability to combine multiple manufacturing processes on a common sustainable substrate providing a clear route for low manufacturing costs and reduced CO2 emissions during device manufacturing and operation phase. Another advantage is their potential for up-scalable fabrication using manufacturing techniques such as additive manufacturing technologies (mainly semi-flexible and flexible hybrid chips). This technology transition would make a huge impact, particularly in reshaping the infrastructure and data transmission of the telecommunications sector and especially at radio-frequency (RF) front-ends, where millimeter-wave frequencies are crucial for the next generation of telecommunications beyond 5G [24].

Multi/interdisciplinary breakthroughs are needed for hybrid chips deployment. Research and industry collaboration should be established covering physics, chemistry, materials science, electrical engineering, advanced manufacturing technologies, and high-performance modeling to develop cutting-edge rigid, semi-flexible or flexible hybrid chips, for multiple applications

Printing technologies cut costs dramatically and reduce the maximum processing temperature with a huge positive impact on sustainability. Flexible electronics, an important unit of sustainable hybrid chips, are highly relevant for the challenges of the future as is evident by their huge market’s potential: IDTechEx predicted that the total market for flexible electronics, which was > 23Bn Euros in 2016, will grow and reach ~ 62Bn Euros in 10 years [25]. The number of possibilities offered by flexible or printed electronics technology is huge addressing various market domains. A novel holistic approach is therefore needed for hybrid chips to achieve the required sustainability, focusing on novel materials [26], advanced manufacturing and packaging enabling hybrid chips functional integration, and developing novel systems architecture.

3 Hybrid chips: architecture, integration and packaging

3.1 Paradigm transition from a system-on-a-chip to a system-in-a-package architecture

The SoC approach was one of the first examples of hybrid chips that combines multiple ICs in a single application processor chip, each one having different functionalities, such as a central processing unit (CPU), a graphics processing unit (GPU), and memory. This architecture has played a crucial role enabling more efficient and complicated functions toward improved data processing and memory units. Unfortunately, scaling down further SoC features is becoming increasingly complex and expensive. An industrial shift toward multi-chiplet design could be part of the solution to these challenges [27]. Multi-chiplet system designs can facilitate large-scale deployment of AI/ML, and enhance silicon yields, while decreasing material wastes during chip production. In a standard SoC, one chiplet performs computation-intensive tasks, while the other implements the I/O interface and a third one executes memory functions. This is especially significant for the automotive sector in terms of power management in autonomous driving. The Kraken SoC, for example, merges numerous acceleration engines and a set of peripherals from various types of sensors into a SiP. Using a heterogeneous architecture to handle difficult visual tasks, Kraken was shown to enable useful applications for unmanned aerial vehicles (UAVs) [28].

Nowadays, multi-chiplet SiP designs are replacing SoC approach [27]. Chiplet technology has become a popular technique that combines additional functions and capabilities enabling the improvement of system-level performance and power economy. As a solution to yield concerns in larger chips, chiplet integration permits separating the design and implementing sub-systems into separate smaller dies (like processors, memory, RF modules). A large-scale application-specific integrated circuit (ASIC) can be divided into several dies that are connected through chiplet integration forming a heterogeneous SoC. To facilitate efficient communication between the various chiplets, many dies prepared from different processing technologies can be combined utilizing dense parallel package interconnects. Recent advancements have seen the incorporation of even more diverse components, including analog, digital, and even optical components, leading to highly versatile chip solutions. SiP designs include advanced connectivity features, integrating components like 5G modems and Wi-Fi chips, vital for the IoT and smart device markets.

It has been shown that the SiP approach enables customization, high degrees of flexibility, and low costs when compared to alternative packaging options. The SiP architecture as a novel, advanced integration and packaging technology allows better performance in terms of density, power, and scaling down [29]. Within multi-die architecture, there are three different levels of integration. Figure 4 depicts that the smaller integration level is that of SoC. Multiple SoC can be coupled together toward more complex functions constituting the SiP integration level. Lastly, multiple SiP units can be integrated on the same PCB. Despite the numerous benefits of chiplets, multi-die systems have yet to gain general adoption—there are still advancements to be implemented. Integration technologies, power restrictions, and dedicated testing provide specific issues. The physical size of components, connectivity, layer transitions, and package size all restrict the ability to increase the bandwidth of the interface between chiplets. The 3D stacking capabilities of chiplets, on the other hand, may lead to a system with high-bandwidth interconnects between the chips while preserving a relatively small form factor and offering a solution to the heat dissipation issue when chips are packed together. Another barrier to multi-die systems further deployment is the lack of industrial standards. To this end, the Universal Chiplet Interconnect Express (UCle) [30], which was launched in 2022, is a major component in enabling chiplet further innovation. More details on potential barriers for hybrid chips technology deployment can be found in Sect. 5.

Different heterogeneous integration levels implemented in modern hybrid chips. The lowest integration level addresses the SoC approach, while a higher level is related to SiP implementation through multiple SoC integration. In complex hybrid chips, a third level of multiple SiP integration is implemented on PCB level

3.2 Heterogeneous integration and packaging technologies in rigid hybrid chips

Next-generation computing architectures require the ability to monolithically incorporate specialized accelerators to meet the demands of various applications [4]. A prerequisite for this is to develop monolithic interconnects that provide ultra-high bandwidth at very low power and extended capacity. 3D integration involves stacking multiple semiconductor layers or dies on top of each other. By stacking chips, data can travel shorter distances, reducing latency and improving overall chip performance. This is particularly beneficial for applications like high-performance computing and AI. Key metrics to monitor system’s operation are performance per Watt and performance per unit cost. Equally important is also how the system responds to thermal and power integrity issues associated with Moore's law and the ever-increasing integration density. Heterogeneous integration in standard rigid SiP hybrid chips is implemented using current generation 3D designs such as silicon interposers and omni-directional interconnect (ODI), while hybrid bonding and flip chip method provide powerful tools to address several of the above difficulties [31]. The flip chip is an improvement over wire bonding in terms of signal integrity, power integrity, flexibility, and downsizing. However, in the majority of the available heterogeneous integration approaches, materials and processes that are vastly different compared to standard packaging and silicon procedures are used, placing considerable constraints on the types and densities of integration that can be attained. Recent progress in techniques like Through-Silicon Vias (TSVs) and wafer bonding has improved the feasibility and reliability of heterogeneously integrated stacks.

Sophisticated packaging methods are used for SiPs such as fan-out wafer-level package (FOWLP), chip-on-wafer-on-substrate (CoWoS), Embedded Wafer-Level Ball Grid Array (eWLB) [32], Embedded Multi-Chip Interconnect Bridge (EMIB) [33] and others [2]. FOWLP provide a very high overall system density, which overcomes the issue of insufficient implant balls created by too many chip pins in typical wafer-level packages. The eWLB has evolved from FOWLP, and this style of packaging not only increases interconnects density but also decreases package size offering a significant amount of board space. Integrated 2.5D and 3D eWLB solutions are available compatible with improved heat dissipation and processing performance for 5G and AI applications. Finally, Intel has invested much R&D in EMIB packaging approach that is based on an organic-board-type package with outstanding electrical properties, offering enhanced shielding structure, as well as minimal crosstalk and losses.

3.3 Novel heterogeneous integration approaches in semi-flexible hybrid chips

Thinned silicon ICs are an essential component of semi-flexible hybrid chips. In a usual assembly process of semi-flexible hybrid chips, printed devices and circuits are firstly manufactured, while semi-rigid silicon components are fabricated in a later step. Thinned silicon ICs are particularly appealing for hybrid chips development on flexible substrates because they can be twisted or stretched up to a specific mechanical strain limit. To this end, a great amount of effort has been paid on developing ultrathin silicon ICs with thickness down to few μm that can be bent to a radius of curvature of 5 mm [34]. Various materials and methods have been used in recent years to transfer and mount Si ICs and flexible electronic components together onto flexible substrates [35] and stretchable substrates [36]. As a typical technique for connecting the circuits together, ultrathin ICs are embedded in a film toward a full system fabrication-in-a-foil approach [37]. Specifically, to connect Si ICs with printed sensors and circuits, an interposer is required that transmits the signal to a pitch spacing (> 100 μm); a processing compatible with printing technologies [8].

Semi-flexible hybrid chips also require passive components such as resistors, capacitors, and inductors in addition to silicon ICs. These surface mounted devices (SMDs) are commonly incorporated into flexible hybrid chips to provide circuit functionality. Silicon ICs and SMD passive components are connected using soldering or dispensing Isotropic conductive adhesives (ICAs) between the chip and the substrate. To align various chips, a flip-chip pick-and-place tool can be utilized. In a typical process, the substrate is first drilled to create the via holes that connect top circuitry to the bottom circuitry. Chip pad alignment to printed traces must be precise—alignment accuracies of tens of μm are needed for bonding tools [8]. NextFlex’s first-generation printed Arduino is a product fabricated using this process flow [8].

The printed units of semi-flexible hybrid chips can be fabricated by using various large-scale manufacturing technologies such as transfer printing (TP), contact printing (CP), in-tandem contact-transfer printing, and other advanced printing processes. These industrially compatible techniques can enable the accurate integration of devices of various dimensions onto planar or 3D layouts [36, 38]. These printing processes offer a low-cost approach to implement heterogeneous integration of microchips with other functional components, allowing to obtain high transfer yields of nano [9] or micro [39] chip size structures. For example, TP has been investigated for high transfer yield pick and place of microchips (100 µm) onto flexible substrates. [40] Although the pick-and-place method using elastomeric stamps works well for printing large microchips, it is difficult to be used for ultrasmall chips with size ≤ 100 μm and/or nanoscale materials with high transfer yield. This is because at these dimensions, adhesion forces such as electrostatic and Van Der Waals on the chip surface may prevail over gravity forces, introducing complications [31]. Furthermore, due to their ultra small size, thinned chips are more prone to fail during transfer than thicker chips [36]. These issues might be overcome by using the "direct roll transfer printing" technology, which has been proven to integrate laterally aligned nanoscale and microscale components with a 95% transfer yield [39]. However, the range of functional materials that may be printed using this method is restricted by the available wafers. Alternative nanostructure assembly methods, like CP [36], which use bottom-up grown nanomaterials to produce nanoscale electrical layers on diverse substrates, might circumvent such restrictions (Fig. 5).

A novel manufacturing approach for semi-flexible hybrid chips combining thinned Si ICs with printed units and interconnections on flexible substrate [28]. Stage 1: direct transfer printing of the ultrathin chips; Stage 2: contact printing of nanoscale electronic layers; and Stage 3: direct ink writing of the miniaturized metal tracks defining the device electrodes and interconnects. Copy rights belong to reference [28] that is an open access article distributed under the terms of the Creative Commons CC BY license

4 Opportunities

4.1 Hybrid chips for healthcare and wellbeing applications

With the development of ML and AI, new chips may now be created to support technologies such as wearable IoT incorporating neural networks and deep learning processes [41]. Wearable devices [42] and human–machine interfaces (HMI) are important components of IoT technological transformation, with applications in digital healthcare, automotive sector, autonomous robots [43], virtual reality (VR), and augmented reality (AR). The quality of the interactive experience with the real and virtual worlds is determined by the natural two-way interfaces allowed by wearables and HMI, as well as the real-time touch-based information they supply and receive. Digital healthcare requires wearable devices that can perform data processing through brain-computer [44]. Haptic technology advances [45, 46] coupled to these technologies are also expected to enhance the overall safety and users comfort in various fields.

Many essential IoT device challenges, including energy efficiency, flexibility [47], and processing speed, may be addressed by hybrid chip solutions, resulting in devices with longer lifespan and a better user experience. Hybrid chips combined with an AI-enabled materials synthesis and design methodology can even aid humans in overcoming difficulties that were previously unsolvable, i.e., enable the development of flexible, biocompatible wearable devices [48]. This can be achieved using material innovation enabled by hybrid organic and inorganic semiconductors opening the path for wearable devices [49] application in various domains and facilitating many different end-user needs. This includes healthcare applications such as brain-computer interfaces for self-management and screening, diagnostics, and treating neurological and mental disorders [50]. This kind of e-neuropatches and stimulation devices can improve the overall patient experience and bring solutions to them that were unattainable with conventional chips technology. A notable example of integrating haptic technology [50] into a wearable device is the potential to aid individuals with sensory impairments such as deafblind, improving their communication and accessibility capabilities and enhancing their quality of life. This haptic technology [51] can also be implemented in the automotive sector to simulate complex manufacturing processes and create touchable and interactive surfaces in vehicle interiors [52, 52] to improve the overall safety and comfort of the passengers. Furthermore, flexible hybrid chips could enable two-way tactile [53] communication for users in AR/VR applications. This would provide a more immersive and interactive experience for the end users within the tactile internet concept as in the case of the metaverse [54]. Hybrid chips can also offer remarkable advantages in the photonics packaging field [55] by improving the integration and functionality, which can lead to contributions in a plethora of applications such as data communications, sensors, and imaging.

By bringing together scientists from many disciplines, while merging multiple manufacturing techniques within a SiP approach, considerable advancement in wearables [18, 56] and IoT technologies is envisaged enabled by hybrid chips adaptability and enhanced functionality.

4.2 Hybrid chips for adaptive edge computing and robotics

Adaptive edge computing can greatly benefit from hybrid chips by enabling systems with significantly lower energy consumption and enhanced data processing energy efficiency. By leveraging hybrid chips' adaptive edge capabilities [57], IoT devices can also perform [58] data processing locally without relying on cloud communication. This architecture therefore effectively reduces the power and time needs improving the latency of such devices as well as security since all the data analysis will be done locally. This ensures that the IoT [59] systems remain functional even under challenging conditions. These emerging capabilities will also assist the sustainable growth of IoT [60] networks that are expected to reach soon billions of interconnected devices.

The compatibility of memristive technology with the CMOS process, makes the use of hybrid chips highly relevant in the context of energy-efficient, neuromorphic edge computing devices [58, 61]. This allows for unconventional circuit design and adaptation in ML algorithms taking advantage of the memristive device properties. Neuromorphic systems constitute a great opportunity for the future of electronics since they are scalable [62] and can combine both analog and digital synaptic functions compatible with large-scale integration circuits. This overcomes traditional limitations while offering the advantages of neuromorphic computing [41] revealing the beneficial role of hybrid chips as recently demonstrated in robotics [63]. Specifically, an autonomous standalone robot that uses integrated organic neuromorphic (organic electrochemical transistors and organic MEMS) was shown to learn through sensorimotor integration. Coupling neuromorphics with hybrid chips leads to robotic systems with low energy consumption and easy-to-tune architecture. These adaptable and decentralized autonomous robotic devices certainly pave the way toward more complex behaviors. Neuromorphic sensory systems can also be integrated on stretchable substrates. Combining various technologies and materials such as quantum dot light-emitting diodes, capacitive pressure sensors, resistive RAM synapses, neural network processing, as well as intrinsically stretchable materials (i.e., PDMS polymer), a highly versatile neuro synaptic system can be created. This hybrid system can adapt to different mechanical deformations, making it suitable for wearable electronics as well as HMI.

Distributed energy systems are an inseparable unit in the next-generation wearables and robotic systems. This novel architecture offers features such as high flexibility, availability, and eco-friendliness, while enables devices that are safe, have high efficiency, and are self-sustainable. Bioinspired distributed energy could enable novel technologies where energy sources are critically needed for autonomous robots to work in unstructured environments for extended periods [64]. Inspired by nature, multifunctionality integrates energy storage, actuation, and sensing in a combined unit within the device by using electroactive polymers and batteries, allowing this way to reducing the weight of the robots and perform more complex tasks. Specifically, distributed energy harvesting, and storage can benefit wearable systems and even a swarm of micro-/ nanorobots. This decentralized power structure constitutes an efficient solution for robotic applications while having the potential for universal application. All those benefits will contribute in making our everyday life smarter with applications in Big Data, AI analytics, IoT, autonomous robots [64], digital twin simulations, and neurotechnology.

5 Challenges

5.1 Steps for addressing the current challenges

The first step towards developing semi-flexible hybrid chips is to adapt and structurally integrate conventional semi-rigid circuits onto substrates that are commonly used in flexible electronics [50] (Fig. 6). This is an important path to develop (semi-) flexible hybrid chips exhibiting foldable and stretchable functions compatible with new generation of electronics that are required within IoT. The second step is to transfer and adopt the multi-chiplets approach [65] already developed in rigid hybrid chips technology, to (semi-) flexible hybrid chips (step 2 in Fig. 6). Integrating multiple components, such as sensors, energy generation and storage units and communication interfaces in a single platform or structure has been already demonstrated as a promising path in rigid hybrid chips technology. This approach allows for the heterogeneous integration of various materials and components into platforms targeting emerging applications with a key focus on low power consumption during manufacturing stages while producing components with energy-efficient operation. As a third set, a multitude of efficient manufacturing processes, methods, and testing schemes should be developed providing a comprehensive framework for the design, production, assembly as well as testing of the various components and systems (step 3). This will ensure sustainability and reliability during production, development, and evaluation.

Novel hybrid chips development require multi-disciplinary and multi-domain approaches that will enable seamless interconnections between different devices and modules. A flexible functional and heterogeneous integration [66] of technologies on the component, module and system level should be demonstrated (step 4). Overall, hybrid chips (rigid or flexible) approach allows fostering of innovation and sustainability in the semiconductors industry accelerating IoT’s mission. Below, we analyze the main challenges towards hybrid chips' further development, namely achieving reliable heterogeneous integration while developing suitable materials and processes towards sustainability in line with the electronic components and systems roadmap [67](Fig. 6).

5.2 Materials and Processes Development

Identifying the right materials and manufacturing processes to be developed is a crucial step and a significant challenge in the progression of hybrid chips. Specifically, (semi-) flexible hybrid chips require a multitude of processes, as well hybrid combinations, and novel additive manufacturing techniques, to ensure sustainable and cost-efficient manufacturing (Fig. 7). The transition to non-silicon and non-silicon compatible materials, or at least thinned Si ICs, requires substantial research to identify suitable substrates, active compounds, and packaging materials. These materials need to have properties that are either complementary or better than silicon [42, 68, 69] and offer new functionalities that expand the range of hybrid chip applications. Towards SiP implementation, power autonomy and power efficient computational resources are required that is achievable through a physical and functional integration. An extension of semiconductors coverage beyond silicon is required including advanced materials that are abundant, recyclable and non-toxic, as well as biocompatible / biodegradable substrates.

Layered 2D materials (LM) possess a great potential [68,69,70] thanks to their exceptional properties while at the same time offering easy integration processes with silicon CMOS technology making them the perfect candidate in order to expand conventional silicon chips functionalities. Unique properties such as high surface-to-volume ratio, tunable electronic properties as well as incredible mechanical and optoelectronic capabilities enable these materials to be applied in a number of applications from gas, chemical, and biosensing to events MEMS/NEMS, optoelectronics, photonics, neuromorphics and even quantum computing [68,69,70] 2D materials are particularly interesting because of their hybrid integration compatibility with conventional CMOS circuits such as transistors [72]. LM are usually grown on rigid substrates and then are transferred to flexible substrates, requiring the need of complex transferring process that could affect the quality and electrical properties of LM [73, 74].

Although LM possess promising properties for advancing chips technology, their limited manufacturing at scale, while adhering to industry standards, is still under progress. High processing temperatures are required for producing LM with high quality, while controlling the contact interfaces present difficulties. The performance of devices utilizing these materials is still limited and only demonstrated in lab scale, originating in low quality interfaces and contacts. Precise etching or layered 2D material removal poses another challenge. Meanwhile, the objective of the European Experimental Pilot Line for layered LM [71] is to overcome these manufacturing bottlenecks. Despite these challenges, LM are excellent candidates for various applications such as integrated circuits, neuromorphic computing, and quantum technologies. They could also be ideal for sensing applications requiring high sensitivity, photonic and optoelectronic applications due to their unique properties like low surface carrier scattering and direct band gap. Nevertheless, the successful integration of these materials on industrial level depends on whether the above mentioned technical challenges can be overcome [70].

Another factor to consider is the availability of these materials at large quantities as well as their sustainability (Fig. 7). These newly implemented materials and processes must be more environmentally friendly than their previous counterparts and need to be recyclable to minimize their environmental impact. The whole initiative should support circular economy while avoiding the e-waste issues of silicon-based technology [75]. The efficient recycling and reuse at the end of the life of new materials is also crucial, and it can substantially contribute to the overall sustainability of electronics and technology in general. At the same time, those materials and processes must maintain safety conditions both for the end user as well as for the people involved in the development process. There is a need, therefore, for non-toxic precursors and solvents to ensure that their use and disposal after usage do not negatively affect the environment. All the above need to be ensured while retaining high levels of performance and reliability for the intended use case scenario. This smooth technological process transition for hybrid chips is required to fulfill the prerequisites of chips industry and therefore ensure its success. Revolutionizing the materials used in chip applications has the potential to revolutionize the semiconductor sector and help advance beyond Moore’s Law.

5.3 Heterogeneous Integration, Scalability, Standardization, and Reliability Testing

Achieving heterogeneous integration and demonstrating scalability potential are key prerequisites for the successful deployment of hybrid chips, either being developed on rigid or flexible substrates. This development involves tackling issues of material compatibility as well as scalable manufacturing processes, system integration, standardization, testing, and reliability. Despite the many advantages of chiplets, multi-die systems have not yet seen widespread adoption—there are still many necessary innovations to be implemented related to rigid hybrid chips. Developing effective strategies for integrating various materials and technologies in hybrid chips requires addressing the complexity of heterogeneous integration [76]. All targeted sub-units of hybrid chips must be compatible with existing hardware and software infrastructures. Integrating different materials and technologies requires the consideration of material compatibility since different materials can have distinct electrical, mechanical, and thermal properties. This includes physical dimensions, power requirements, interface mismatch issues, and many more. Incompatibility therefore can significantly hinder adoption of emerging technologies. The physical size of components, interconnections, layer transitions, as well as the interface quality between chiplets and the size of the package could limit the bandwidth of targeted systems.

Semi-flexible hybrid chips require combining the manufacturing processes of silicon CMOS chips and flexible electronic components into a seamless, cost-effective manufacturing line. This is a complex activity since new equipment or significant modifications are required placing a barrier to fast adoption of this emerging technology. Existing electronic design automation tools optimized for rigid, planar substrates should be adjusted increasing complexity and cost, while new tools and design methodologies should be developed to address specifications of flexible hybrid chips. Ensuring compatibility between flexible hybrid systems and existing CMOS-based systems in terms of thermal and mechanical properties, required voltage levels, communication protocols, and power requirements is also essential. Flexible substrates typically have poorer thermal conductivity than silicon, posing challenges in heat management for high-power applications, while operate at different voltage and power levels. Notably to mention, differences in thermal expansion coefficients between silicon chips and flexible substrates can cause reliability issues, thus stress at the interface can lead to device failure.

Thinned silicon ICs, featuring tiny touch pads, are fragile, while standard assembling tools can damage the final hybrid chip as a result of enhanced heat conduction. There is also a need to design strategies for flexible interconnections to ensure efficient communication between subsystems, at required operation frequency and minimum signal noise. Developing interconnects that can withstand multiple bending and sending cycles, while maintaining high electrical conductivity is challenging. Conventional metallic interconnects may not be suitable to operate under these conditions, urging for the development of stretchable conductive materials, i.e., based on LM or other novel material. Demonstrating interconnections that allow transmission of low noise signals across hybrid systems can be demanding due to the different electrical performance of flexible materials especially at high frequencies.

Identified processes should allow scalability for larger use case scenarios [77] avoiding units failure considering relevant mechanical and thermal stress during fabrication (Fig. 5).This is a crucial step to ensure smooth system heterogeneous integration. The demonstration of large-scale hybrid chips is a major challenge. Scaling up manufacturing should be compatible with increased volume, while maintaining the same chips quality and yield. This is a demanding task for hybrid chips due to their inherent complexity and the required heterogeneous integration of multiple technologies on the same package. Maintaining the same performance across all chips at scaled up production becomes challenging, since slight variations in one sub-unit of the system can significantly impact the overall chip performance. One of the advantages of hybrid chips is their customization features rendering them applicable to various applications such as consumer electronics, automotive, or medical devices. At the same time, however, this induces a barrier for the upscaling of hybrid chip technology because each application field has specific requirements that all should be taken in account to meet these diverse needs. Managing heat dissipation and power becomes more challenging for upscaled demonstrations. This is crucial in applications like data centers or high-performance computing, where the density of computing power (and hence heat generation) is very high.

The scalability of hybrid chip technologies is also dependent on the availability and current cost of precursor materials, especially if CRM are part of the hybrid chip, making large-scale production financially or logistically challenging. The upscaling of semi-flexible hybrid chips depends on the availability and cost-effectiveness of flexible substrate materials like polyimide, parylene, or other polymers. Scaling up their production involves adapting existing fabrication techniques (like lithography) for flexible substrates or developing new methods that can reliably be used to print flexible chips on these materials. Moreover, in semi-flexible chips peripheral units like batteries, antennas, and sensors (not all necessarily flexible), should be integrated with flexible units. The integration of flexible units with conventional CMOS electronics, and hybrid chips into existing systems in general, requires the development of standardized methodologies whereas a specific focus should be given on interconnect and communication standards. Hybrid chips should effectively communicate with other components thus enabling their seamless integration and their wider adaptability. UCle will likely be a critical part of enabling chiplet innovation in rigid hybrid chips.

Another important ingredient for hybrid chips’ further deployment is the development of reliability testing protocols to verify whether a product can operate consistently over the duration of a given life cycle. Developing strategies for efficient testing methods to ensure their performance and reliability could also give feedback to standardization methodologies. When it comes to package reliability study, possible difficulties include warpage, chip cracking, delamination, toughness fracture, plastic deformation, and many more. The system can fail in a variety of ways, including stress fracture, high-temperature deformation and degradation, open circuit, short circuit, line impedance mismatch, electromagnetic interference, and many others. Maintaining consistent performance and reliability as (semi-)flexible hybrid chips production scales is challenging due to potential variability in flexible substrates and the sensitivity of organic materials used in some flexible electronics. In particular, ensuring compatibility and reliable electrical connections as production scales is crucial- a demanding task that requires extensive testing at various conditions. Accelerated lifespan testing, which is often employed in conventional silicon devices, may also be applied to hybrid chip’s reliability testing. Mechanical tests encompass the investigation of bonding processes, materials, and their tensile strength during bending, stretching, and twisting. The interfaces between rigid components and printed circuit lines should be tested using repetitive bending at a defined radius or shear force testing. This development of strategies for efficient testing [3], failure analysis, and fault tolerance will be critical to maintain the high standards required by semiconductors industry. Three factors—thermal management, mechanical stress, and electrical properties—can be investigated in specific use cases in order to detect and improve package reliability. The lack of standardized processes and materials for flexible electronics compared to the well-established standards in silicon-based manufacturing can be a limiting factor for scaling production.

Though the transition to (semi-) flexible hybrid chips adopting a multi-chiplet approach provides certain challenges, it opens the path for a variety of emerging applications. To address these challenges and effectively scale and integrate flexible hybrid chip technologies, ongoing R&I is crucial. Collaborations between academia, industry, and material science experts are essential to advance materials, manufacturing processes, and design tools. Additionally, developing universal standards and protocols for flexible chips will play a critical role in enabling their wider adoption and integration in existing products. This paradigm transition is expected to be a slow process, requiring incremental advancements in technology, manufacturing, and design methodologies. However, the potential applications of these lightweight, and versatile electronic devices are significant, securing already a lot of investments. Lastly, the integration of hybrid chips into consumer products requires society’s adaptation in new technologies, while the benefits of these new chips should communicated to potential users allowing their successful integration into the market. Overcoming those obstacles will bring us one step closer to realizing market products based on efficient hybrid chips.

5.4 Economic implications for the technology transition to hybrid chips: manufacturing costs, economic feasibility and market readiness

A significant investment is required in R&D of hybrid chips, as described in previous sections, including addressing the cost of developing new materials, processes, and heterogeneous integration methods. While manufacturing costs of chiplet-based designs are in principle lower than standard CMOS (better yield due to smaller area), overall costs of rigid hybrid chips are still less clear. This is due to the complexity of integrating different technologies, the need for specialized equipment, and potentially lower yields in the manufacturing process at least during the initial production phase. Although the initial costs of developing and manufacturing hybrid chips are high, they may offer long-term savings in terms of energy efficiency, performance, and miniaturization benefits. More R&D is required on design, architecture, verification, and testing in order for this technology to offer systems with lower cost. In the near future, rigid hybrid chips may use materials that are less common or more expensive than those used in conventional silicon chips, however the economy of scale can reverse this situation in a longer term. After establishing the required infrastructures and technological tools for these emerging chips, production pace can ramp up leading to optimized processes reducing thus corresponding manufacturing costs.

The paradigm shift to flexible hybrid chips manufacturing is even more ambitious compared to rigid hybrid chips since this transition is a costly and time-consuming process that requires new manufacturing facilities, equipment, and specialized skill sets, leading to significant investment and training costs. Establishing a reliable supply chain for novel materials and components used in flexible hybrid chips is crucial and can be a severe limiting factor. Compatibility with current technologies and standards is crucial. As with any emerging technology, there is a risk associated with the uncertainty of market acceptance. The market readiness of semi-flexible or flexible hybrid chips is even less established compared to rigid hybrid chips. Although there have been significant advancements, it is still an emerging field compared to conventional silicon-based technology and rigid hybrid chips. Integrating flexible chips into existing product lines may require important redesigning effort, impacting their readiness for market exploitation, depending on how easily they can be integrated into existing systems and infrastructures. The market adoption also depends on consumer awareness and on what benefits flexible chips can offer to their lives. In specific applications like wearable technology, the long-term benefits due to the durability and versatility of flexible chips may justify the higher initial costs. Furthermore, there is strong potential to create new product concepts such as foldable smartphones and smart textiles, establishing significant market opportunities, which can be an important factor in the cost–benefit analysis. The application of hybrid chips is foreseen in smartphones and laptops, while the challenge is to integrate them without significantly increasing the cost or affecting device form factors. Another targeted domain is the automotive sector (electric and autonomous vehicles) that can benefit from the advanced capabilities of hybrid chips.

The market is more likely to adopt hybrid chips if they offer significant performance benefits over conventional chips. This includes factors like increased performance, higher speed and efficiency, or extended functionality. This path requires reliability and safety standards. While hybrid chips can significantly improve performance and energy efficiency, integrating them into existing data center infrastructures requires careful management of power and cooling systems. In medical applications, the challenge is not just technical integration but also compliance with healthcare regulations and ensuring reliability. Hybrid chips could revolutionize this sector, but integration requires robustness in harsh environments and seamless communication with control systems. Hybrid chips might open new market opportunities in fields like AI, quantum computing, AR/VR features, or IoT, where conventional chips might not be competitive. This potential for establishing new markets can justify the initial high costs or the high risk that companies should take aiming at gaining a significant competitive advantage. Hybrid chips might offer environmental benefits, like reduced energy consumption, low manufacturing temperatures, extended flexibility, and emerging functions that can be a significant factor in their overall cost–benefit analysis, especially in a market increasingly concerned with sustainability.

Semiconductor chips in general have a very high market value and have a very high compound annual growth rate (CAGR). A study from custom market insights (Fig. 8) showed that they could reach a market of 1.12 trillion by 2023 [78]. The GAGR for this study was approximately at 7.1% but in 2023 according to Gartner a decline of the market was reported by 10.9%, but it is expected to reach back on target at 2024 with a rise of 17% [79]. On the other hand, the growth for hybrid chips is multiple times higher, signifying their projected use case scenarios (Fig. 8). According to Veracious Statistics Research, the market value for hybrid chips at 2020 was 21.14 billion with an CAGR of 41.2% that based on our estimations (Fig. 8) could reach a staggering 236.56 billion market size in 2027 almost half of the current semiconductor market [80]. Flexible hybrid chips also exhibit approximately double growth rates in comparison to conventional semiconductor chips. The market value at 2021 was approximately 125 million with a projected growth of 16% reaching close to 411 million in 2029 and approximately 306 million in 2027 according to a statistical research by maximize market research [81]. This market analysis for each technology with the projected market growth indicates the projections of the market for hybrid chips is highly favorable.

In summary, while the transition to hybrid chip technologies presents significant economic challenges, including high initial costs and market adoption barriers, it also offers potential long-term benefits like performance improvements, new market opportunities, and environmental advantages. Balancing the high initial costs and market readiness issues against the potential long-term benefits and opportunities is crucial in assessing the feasibility of transitioning from conventional silicon chip technologies to rigid or (semi-)flexible hybrid chips. The decision to invest in hybrid chips technology should be based on a careful consideration of these factors, alongside the constantly evolving landscape of consumer demands and technological advancements.

5.5 Sustainability and Circular Economy

The sustainability aspect of minimizing environmental impact that spans across various categories such as greenhouse gas emissions, human and ecological toxicity as well as the depletion of natural resources, is pivotal for the successful and sustainable development of Hybrid Chips. As a notably example, market estimates indicate that ~ 40 billion passive RFID tags are produced annually, with ~ 24 billion used in retail tagging [82]. Considering only the greenhouse gas emissions associated with tag production, (~ 20–120 g CO2 eq.) [83], this corresponds to 1 – 5 million tons of greenhouse gas (GHG) emissions, with additional environmental impacts arising from contamination of paper or recycling waste streams. Therefore, design for energy efficiency and durability, repairability, upgradability, maintenance, reuse and recycling will be an essential part of IoT device development. This would bring IoT devices in line with regulations, e.g., EU Eco-design directives, which are currently in place for large electronics items [15], and are foreseen for consumer electronics devices, including phones, tablets and chargers.

In order to promote sustainable practices, it is important to consider the repairability and reusability of hybrid chips during the design phase [84]. This could work by including the standardization of the process steps in order to accommodate these practices, such as designing modular components or employing standardized connections and individual parts without the need to discard the whole device. This is also crucial to ensure that hybrid chips can be easily disassembled and sorted through the recycling process. In that way, valuable resources can be conserved, limiting the environmental impact [13, 16] of hybrid chips. Biodegradable materials are another sustainable approach allowing them to be naturally disassembled at the end of their use and their lifecycle. To address this, we need to take into account the expected lifetime period [85] of the hybrid chips and provide an assessment that can lead to overall improvements in the chips designing process and reduce the environmental footprint as well as prolong their life duration leading to better-performing devices with high durability. It’s therefore important that hybrid chips are designed by considering circular economy and promoting sustainable practices.

6 Recent advancements in hybrid chips’ prototypes and products

In previous sections, we have introduced three main categories of hybrid chips, namely rigid hybrid chips, semi-flexible and flexible hybrid chips. Besides, basic elements of the various hybrid chips’ architecture, integration and packaging technologies were presented, revealing that concepts from one chip category can be applied to others. For instance, the multi-chiplet approach of rigid hybrid chips could be applied also in flexible hybrid chips upon required modifications. Moreover, all the above centralized SiP advanced packaging solutions, implemented either on rigid or flexible substrates, have their own characteristics and advantages aiming at increasing the power density, reduce size and enhance system performance for targeted applications. Specific modifications are applied depending on the application such as developing consumer electronics, healthcare devices, wireless communication units, power modules, processors, MEMS based sensors, lasers, circuits for industrial automation, automotive, and data centers, just to name a few examples. In the following section, we summarize recent advancements across the various hybrid chips categories.

6.1 Advances in rigid hybrid chips

Progress in advanced packaging technologies such as SiP, 3D integration, and multi-chiplet designs enabled enhanced performance, functionality, reduced manufacturing costs and enhanced reusability through reconfiguration process [86] for application-specific developments. Sophisticated packaging technologies are being tailored for AI and ML applications where high-bandwidth memory integration and energy-efficient designs are important. Multi-SiP technology has been implemented in various rigid hybrid chips such as wireless communication systems, power supply units, CPUs, lasers, and MEMS-based sensors. Specifically, multi-SiP technology has been reported as one of the best pathways in developing MEMS-based sensors offering scaled down systems with light-weight [87, 88]. Photonic silicon-based sensors can be used to improve the performance of medical diagnostics by speeding up processes like antimicrobial susceptibility testing. Specifically, it was shown that the use of sensors in 3D printed microfluidic devices reduces the time required for a diagnosis [89]. Besides, there is an important advancement of using SiP technology in laser packaging. Following this approach, a miniature laser or other optical components are attached to the chip to form a complete system, which is then soldered onto a PCB and connected to an electrical pin [90].

A next-level heterogeneous integration architecture has been recently released by Intel, termed as quasi-monolithic chips (QMC) approach, implemented in Intel Processors [23] constituting a groundbreaking advancement in rigid hybrid chips. QMC enables combinations of silicon processes and packaging techniques to create 3D architectures with ultra-high interconnections density to fit future computing and AI needs [23]. It uses inorganic materials like silicon dioxide while maintaining the chips cleanliness in the integration process as well as improving the thermomechanical stability of the structure. This arrangement allows for adjustable interconnections while being highly scalable. To achieve near-monolithic interconnections, the development of a modular QMC is implemented using the UCle standard. This hybrid interconnection approach enables chipset interoperability with a power consumption of ten times less in terms of performance than regular die-to-die interconnects. QMC uses advanced hybrid bonding instead of soldered connections between the chips, while it uses a fine-pitch hybrid bonding layer as well as an ultra-thick oxide deposition. Overall, QMC is making advances in heterogeneous integration, interconnections density as well as modularity and combines elements from silicon processing and advanced packaging techniques, making it a serious candidate for the progression of hybrid chips, especially in comparison to conventional architectures. In order to maximize its benefits, modular chiplet interfaces should be developed to enable mix and match of chiplets between different chiplets, e.g., through chiplet interconnect standards [30]. These advances in rigid hybrid chips are reshaping the semiconductor industry, enabling more powerful, efficient, and compact electronic devices. As these technologies continue to evolve, they will play a critical role in the development of next-generation electronics across various sectors.

6.2 Advances in semi-flexible hybrid chips

The motivation of developing semi-flexible hybrid chips is to combine the advantages of both silicon ICs and printed/flexible electronics toward meeting the requirements of emerging application domains. This hybrid approach overcomes the limited performance of flexible electronics in intensive tasks such as data processing or communication by replacing them with silicon chips, while the final hybrid chip retains sufficient mechanical flexibility and stretchability enabled by the flexible units overcoming limits of rigid silicon chips in a clever manner. As an example, printing circuits currently demonstrate low-speed communication in the frequency range relevant for IoT applications such as e-label sensors, e-skin, bioelectronics, HMI, and mobile device technologies [8, 9]. On the other hand, flexible units can be embedded in real-world objects and on human bodies offering distributed monitoring and recording of a wide range of chemical, physical, and biological information. They can bend, fold, and stretch, which is essential for applications in wearable electronics, medical devices, and flexible displays. Printed sensors are used in semi-flexible hybrid chips to convert physical and chemical variables such as temperature, light, pressure, and chemical concentrations, to electrical signals, while energy harvesters provide the necessary operational power. Inputs from these electrical signals are usually processed with silicon chips that include analogue and digital circuitry to receive and process sensory input, execute signal processing, and transmit data to an external host through printed antennas or show information on a printed display. It is therefore important that conventional silicon-based CMOS techniques to be merged with other technologies, particularly printed electronics, to complement the promise of low-cost flexible chips.

Semi-flexible hybrid chips enabled by printed electronic components offer unique advantages such as manufacturing on soft substrates at large areas with high throughput and scalability, while these emerging device concepts with free-of-form structure could have a vast number of sensing applications. These include developments in skin-like electronics that can monitor health parameters and flexible sensors that can be integrated into textiles, in wearables and robotics, as well as in industrial, environmental, and agricultural sensing [91]. Radio-frequency identification (RFID) labels printed on IoT edge objects have been fabricated for logistics/tracking of fragile, sensitive, or costly goods. Such tags typically include a silicon IC, a printed antenna, and printed sensors. Printed electronics, on the other hand, suffer from batch-to-batch and device-to-device process variability, which should be reduced to ensure proper circuit performance. Because of the limited variability and performance of printed units at large area, only small modular circuits have been demonstrated as the first semi-flexible hybrid chips, while silicon ICs provided the demanding functionality. The number of contact pads grows according to the number of I/O required to interact with all the subunits of an ASIC chip. The number of required pads in modern ASIC chips has been increased, while their assembly method limits chip designs resulting in costly manufacturing. In complex chips, the pads should cover most of the silicon-chip surface, making the technology too costly for many of the targeted e-label applications. Ersman et al. recently demonstrated that printed electronic components based on organic electrochemical transistors can be produced and integrated with silicon ASIC toward semi-flexible hybrid chips implementation reducing the required number of pads while cutting production costs dramatically [92].

Christou et al. recently showed the sequential application of direct TP and CP to demonstrate the integration of nano- to chip-scale structures on flexible substrates, offering a novel printing platform for semi-flexible hybrid chips. [9] The team demonstrated that an initially 520 μm -thick Si chip was thinned down to 35 μm utilizing a backside lapping approach aided by a poly(methyl methacrylate) (PMMA) sacrificial layer. The thinned chips were then carefully integrated onto flexible substrates via direct TP. The applied contact force was an important parameter in determining the transfer yield of direct TP. It was reported that an applied force of 5 N was adequate to remove the ultra-thin chips off the stage without causing any cracks or defects. A novel printing platform was then developed to merge conventionally made and in-house thinned chips with sophisticated nanoscale electronic layers of nanowires. The researchers used direct ink write (DIW) printing to define the metal electrodes or interconnections for the semi-flexible hybrid system on a flexible substrate (Fig. 3). Specifically, direct TP method was employed to place MOSFETs based on ultrathin silicon chips at selected location, while photodetectors were built using ZnO nanowires (formed by DIW technique) connected to the ultrathin chips using a custom made semi-automated contact printing system.

A high transistor density integration was recently demonstrated utilizing LM of hexagonal boron nitride. These devices were fabricated using a 180 nm CMOS platform achieving high endurances > 5 million cycles for a 5by5 memristive transistor crossbar [72]. Another example of hybrid chips integrating LM was demonstrated using molybdenum disulfide (MoS2). Films of MoS2 have been synthesized at very low temperatures of about 150 °C, while their unique optoelectronic functionalities are paving the way for many novel applications of flexible hybrid electronics [73]. A wafer scale synthesis of MoS2 at temperatures below 300 °C compatible to industrial scale production was recently reported, while direct integration with CMOS circuits was show cased indicating that the integration of LM with conventional CMOS silicon electronics is possible and efficient [74]. All the above showcase the added functionalities of LM integration with silicon chips that can lead to enhanced performance.