Abstract

In this paper, a gallium antimonide junctionless tunnel field-effect transistor based on electrically doped concept (GaSb–EDTFET) is studied and simulated. The performance of the device is analyzed based on the energy band diagram and electric field profile. The on-current, transconductance, and cut-off frequency are enhanced in case of GaSb–EDTFET compared with Si-EDTFET due to the combination of the high tunneling efficiency of the narrow bandgap and the high-electron mobility of GaSb. On the other hand, the Gaussian-doping profile decreases the ambipolar and off current by increasing the tunneling barrier length at the drain/channel interface. Hence, applying Gaussian-doping profile on GaSb–EDTFET makes it a suitable candidate for analog and digital applications. Next, heterostructure channel/source interface EDTFET is studied which uses GaSb for the source and AlGaSb for the drain and channel regions. Then, it has been optimized by numerical simulation in terms of aluminum (Al) composition. The optimal Al composition was founded to be around 10% (x = 0.1). It is shown that the blend of Gaussian-doping profile and the heterostructure channel/source interface with optimal Al composition remarkably reduces ambipolar current amount to a value of 1.3 × 10−23 A/μm. The improvements in terms of Ioff, Ion, Ion/Ioff rate, subthreshold swing, transconductance, cut-off frequency, and also suppressed ambipolar behavior are illustrated by numerical simulations.

Similar content being viewed by others

Introduction

In recent years, the scaling of conventional CMOS transistors and supply voltage have been faced with problems such as high off-state current, SCEs, DIBL, and subthreshold swing limits of 60 mV/dec at room temperature [1,2,3]. Therefore, some various device structures such as double gate [4], tri-gate [5], gate-all-around (GAA) MOSFET [6], and junctionless field-effect transistor JLFET [7] have been reported. JLFET has been fabricated without using PN junctions at the lateral junctions. Although it simplifies the fabrication process, it also suffers from the high off-state current. Tunneling field-effect transistors (TFETs) recently replaced the conventional MOSFET due to its steeper subthreshold swing (SS) (< 60 mV/dec) and low off-state current (Ioff) which leads to the low values of power consumption [8,9,10,11,12]. The achievement was obtained due to the band-to-band tunneling (BTBT) carriers rather than drift–diffusion over the barrier. One of the drawbacks of the performance of TFETs is the inferior on-state current (Ion) because of the insufficient quantum BTBT limited by the large bandgap of silicon. Hence, it can be solved using low bandgap semiconductors [13]. Lately, different methods of improving the performance of TFETs have been presented such as gate engineering [14], using heterostructures and high-k dielectric [15]. TFETs also suffer from ambipolar behavior [16, 17], which is concluded from the presence of symmetric areas of P+ and N+ in the source and the drain, the overlapping between the valence band of the channel, and the conduction band of the drain under negative gate bias. In this condition, the channel is accumulated by holes due to BTBT at drain/channel interface. Therefore, it has created a high current drive at the negative voltage similar to the positive voltage. To overcome the ambipolar behavior, researchers have used hetero-gate dielectrics, gate workfunction engineering, asymmetric doping for source and drain [18], Gaussian-doping profiles, and gate–drain overlapping [14, 16, 17, 19–22].

Another drawback in the down-scaling process of TFETs is to fabricate metallurgical junctions due to the need for the creation of abrupt junctions at high temperatures which is difficult and expensive [7]. This problem can be solved using junctionless TFETs (JLTFETs) [22, 23]. JLTFET uses high-doping concentrations in the drain, channel, and source. It has provided N+–I–P+ for N-JLTFETs similar to doping profile of an N-TFET using two methods. One method is the use of the charge plasma concept, wherein the desired doping profile is created by choosing appropriate workfunctions for the gates called the polarity gate (PG) located at the source region and the control gate (CG) located at the middle with a lower workfunction than PG for being a nearly intrinsic channel [24,25,26,27]. As the same way, p-channel JLTFET has the similar structure [28]. Another method to create N+–I–P+ in JLTFET is using the electrically doped concept, in which P+ region underneath PG is created by applying an appropriate external bias voltage. These devices are known as EDTFET [29,30,31]. The other type of JLTFETs known as dopingless TFETs suppresses the need of a higher thermal budget and expensive thermal annealing technique due to refusing the physical doping [32,33,34,35,36]. In this structure, the drain region is also gated for creating N+ using charge plasma or electrically doped concepts. JLTFETs also include inferior Ion and ambipolar behavior. To overcome these problems, different methods have been investigated, such as: using heterostructures at source/channel interfaces [37,38,39,40,41], the assumption of gate workfunction engineering [42,43,44,45], the adoption of hetero-gate dielectrics [46,47,48,49], using Gaussian-doping profiles [22, 50, 51], applying source pockets [52], the consideration of strain engineering [53, 54], using ferroelectric insulators [40], and drain workfunction engineering for DLTFET [55, 56].

The rest of this paper is structured as follows. In Sect. 2, device simulations and structures are discussed. In Sect. 3, the DC characteristics for the GaSb–EDTFET are presented which clarify its improvements in analog applications over a basic Si-EDTFET. In Sect. 4, Gaussian-doping distribution is proposed to decrease the ambipolar current. Section 5 is dedicated to the analysis and calculation of analog parameters, cut-off frequency, and transconductance for the GD–GaSb–EDTFET. In Sect. 6, heterostructure channel/source interface EDTFET is studied which applies AlxGa1−xSb for the channel and drain regions and GaSb for the source region (AlGaSb–GaSb–EDTFET). With respect to the Al fraction (x), the bandgap energy of AlxGa1-xSb and, consequently, the tunneling probability and the device current vary. Thus, the optimal Al composition is extracted in AlGaSb based on the improving ambipolar current, off-current, on-current, on-to-off current ratio, threshold voltage, and subthreshold swing. Then, it is presented a performance comparison between the structures in DC parameters is presented. Section 7 concludes this paper.

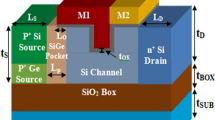

Device structure and simulation

A cross-sectional view of conventional Si-EDTFET is shown in Fig. 1a, GD–GaSb–EDTFET in Fig. 1b and GD–AlGaSb–GaSb−EDTFET in Fig. 1c. A III–V semiconductor has been used in the GD–GaSb–EDTFET, which has a narrow bandgap (0.72 eV) and high carrier mobility [57, 58]. In the GD–AlGaSb–GaSb–EDTFET device, GaSb is used at the source side and AlGaSb at the drain and the channel sides to improve the device performance. It is considered that the channel, source, and drain are heavily n-type doped (1 × 1019 cm−3) in the case of the conventional EDTFET. For the proposed devices (GD–GaSb–EDTFET and GD–AlGaSb–GaSb–EDTFET), Gaussian-doping profile is allocated to channel and drain, although source is kept the uniform doping. All devices consist of two isolated gates (CG and PG) with the same workfunction equal to 4.7 eV. The polarity gate bias voltage VPG = − 1.2 V has been considered for obtaining the desired carriers concentration in the source region. It also provides a concentration gradient at the source/channel interface [30, 31]. In addition, the spacer length (Lgap) is kept 5 nm for creating N+-doped pocket layer near to the source. The doping profile of N+–I–N+–P+ TFET is formed by electrical doped concept rather than physical doping. High-k dielectric was also used to improve the subthreshold swing and on-state current [15]. The rest of the device design parameters used in the simulations are listed in Table 1.

All the electrical characteristics were obtained from 2D ATLAS device simulator [59]. A nonlocal BTBT model to calculate band-to-band tunneling of charge carriers between source and channel was included. In this model, the spatial variation of energy bands is taken into account and also the recombination–generation rate at each location is considered based on the electric field to model the tunneling process. The Shockley–Read–Hall model was also used to incorporate the minority recombination due to the presence of high-impurity concentration in the channel and the interface trap effect. It takes into consideration the phonon transitions that occur in the presence of defects or traps within the forbidden gap of the semiconductor. Fermi–Dirac statistics was invoked to calculate the intrinsic carrier concentration required in the expressions for SRH recombination. Auger recombination is a non-radiative process involving three carriers. It occurs when an electron and hole recombine, but instead of producing light, either an electron is raised higher into the conduction band or a hole is pushed deeper into the valence band. Auger recombination is significant in non-equilibrium conditions when the carrier density is very high. To consider this effect, auger recombination model was included. High doping often leads to narrowing of bandgap and is essential to consider especially within the devices which are based on tunneling mechanism. Therefore, bandgap narrowing model is also incorporated. The quantum confinement model was activated to consider quantum confinement effects on BTBT.

DC-performance analysis

In this section, The DC performance and the comparison of Si and GaSb based on electrically doped concept have been analyzed. Tunneling devices have transported the phenomena entirely different from bulk MOSFET devices. Drive current in TFETs is computed based on band-to-band tunneling from the valence band of source to the conduction band of channel. Electron/hole tunneling probability in this research is calculated using the nonlocal BTBT model on the basis of the Wentzele–Kramere–Brillouin method. Band-to-band tunneling probability strongly depends on material/device parameters such as the screening tunneling barrier length (Λ), energy bandgap (Eg), band energy difference between the valence and conduction bands of tunneling regions (ΔΦ), and effective mass of charge carriers (m∗), according to Eq. (1) [3, 60–62], wherein h and q are the Planck constant and electron charge, respectively:

Tunneling barrier length (Λ) given by Eq. (2) is sensitive to the dielectric thickness (tox), semiconductor channel thickness (tSi), dielectric constant of the gate material, and semiconductor (εSi, εox):

In the N-TFET device, drain is always biased with positive voltage to allow the connections between source–channel and the drain–channel will be in reverse bias. Device current is proportional to tunneling probability, which itself depends on the variation of band structure at the source/channel and drain/channel interfaces. The band structure is changed by varying gate and drain voltages. By overlapping the conduction band with the valence band, tunneling probability is increased at regions. At on state, under the positive gate voltage, an overlap occurs between the conduction band of the channel and the valence band of the source. According to Eq. (1), to increase on-state current of EDTFETs, lower bandgap material can be used. In Fig. 2, it is observed that the on-state current in case of GaSb–EDTFET is higher due to the presence of lower bandgap (0.72 V) of gallium antimonide. At the ambipolar state, in which negative gate voltage is applied, an overlap is created between the conduction band of the drain and the valence band of the channel. Therefore, the ambipolar current is also increased in case of GaSb–EDTFET by applying lower bandgap material. Increasing current is explainable based on the energy band diagram. In Fig. 3a, b, it can be observed that the tunneling barrier length is narrow at the drain/channel interface (at off state) and is also thin at the source/channel interface (at on state) in case of GaSb–EDTFET. The electron-tunneling rate can also represent the increasing current. Figure 3c shows the higher electron-tunneling rate for GaSb–EDTFET at on state. The current is also proportional to the electron-tunneling rate, which depends on the transmission probability, according to Eq. (1). Therefore, the on-state current significantly increases due to the improving tunneling rate.

Gaussian-doping profile

To reduce off and ambipolar current, the tunneling barrier length at the drain/channel interface must be increased at off and ambipolar states, which can be achieved by applying the Gaussian-doping profile [51]. Based on the results obtained from Sect. 3, the GaSb–EDTFET has higher on-current than the Si-EDTFET. To improve the performance of the GaSb–EDTFET in digital applications, in addition to analog applications, along with increasing the on-current, reducing the off and ambipolar current is considered. Therefore, in this section, the impact of the Gaussian-doping profile on the performance of the GaSb–EDTFET is studied by applying it in the drain and channel. Figure 4 illustrates the contour plot of the Gaussian net doping of the device. Accordingly, source is n-type-doped uniformly with a concentration of 1 × 1019 cm−3. The peak of Gaussian doping is at the source/channel interface and diminishes exponentially along the channel to drain. Thus, a lower concentration is observed at the channel and drain regions. The lower number of electrons tunneling at the drain/channel interface using Gaussian doping supports the reduction of the off and ambipolar current.

In Atlas, Gaussian doping is defined, according to the following equation:

where peak is the amount of peak of Gaussian profile and the char represents the standard deviation of doping.

The decrease of the off and ambipolar current by applying Gaussian doping to GaSb–EDTFET device (GD–GaSb–EDTFET) is shown in Fig. 5. Energy band diagram of the structures at off state, wherein gate voltage is zero, is represented in Fig. 6a. It illustrates that no overlap happens between the conduction band of the channel and the valence band of the source. It is also observed that the tunneling barrier length is higher by applying Gaussian doping. Therefore, at off state, according to Eq. (1), the probability of the tunneling is diminished, and consequently, the current is reduced. Similarly, it accrues at ambipolar state. The electric field is obtained from the gradient of the energy band diagram. As can be seen in Fig. 6b, there are two peaks at source/channel and drain/channel interfaces in the electric field profile of GaSb–EDTFET, because the doping profile is N+–I–P+. In the GD–GaSb–EDTFET, the gradient of the energy band diagram at drain/channel interface is neglected due to Gaussian-doping profile; consequently, the electric field profile at this interface is negligible; therefore, the off current is reduced. The ambipolar performance is also similar to off state.

The performance of the device in the subthreshold region is often based on the subthreshold swing. Point subthreshold swing (SSp) represents the reverse of the slope of the transfer characteristic under log scale for Ids. Since the average subthreshold swing (SSave) is independent of the step size of gate voltage, it is more common to use. The entire range of gate voltage up to threshold voltage (Vth) is used to calculate SSave, according to Eq. (4) [13, 19]:

where Vth is the threshold voltage obtained at the drain-to-source current which is 10−7 A/μm [1]. Voff voltage denotes the voltage at Vgs equals to zero. Based on the calculations, in addition to improving the parameters in terms of Iambipolar, Ion, Ioff, and Ion/Ioff ratios in the GD–GaSb–EDTFET compared to the conventional EDTFET, the threshold voltage and subthreshold swing have also been rectified. Vth is 0.6 V and SSave is 56 mV/dec for the GD–GaSb–EDTFET, compared to 0.78 V and 84 mV/dec for the conventional EDTFET.

Analog performance

In this section, the analog performance of the GD–GaSb–EDTFET compared to the conventional EDTFET is analyzed. Cut-off frequency (fT) and transconductance (gm) of the structures are obtained and compared. The parameter gm is the ratio of the variation in the drain current to the variation in the gate voltage of the device. By increasing the gate–source voltage, the number of electrons injected from the source\channel interface is incremented due to the quantum-tunneling phenomenon; therefore, the gm parameter is increased which has the significant role to determine cut-off frequency.

The parameter fT, determined by fT = gm/2πCgg, is evoked from a small-signal ac solution at a frequency of 1 MHz, wherein Cgg represents the total gate capacitance and is defined by CG = ∂Qch/∂Vgs. Qch is the total charge in the channel. By assuming a good gate electrostatic control, the parasitic capacitance can be negligible [61]. Therefore, it is considered that the charge in the channel and gate is the same. Significantly enhancement analog performance of GD–GaSb–EDTFET is observed in terms of gm and fT compared to the conventional EDTFET in Fig. 7a, b.

Heterostructure EDTFET

In the previous section, the ambipolar and off current were decreased using the Gaussian-doping profile. In the rest of this research, heterostructure channel/source interface EDTFET is investigated. Heterostructure TFETs employ a low bandgap material at the source region resulting in the improved on-current. However, the ambipolar behavior can be suppressed using a wide bandgap material at the source and drain side. Therefore, the AlGaSb at the channel and drain side and the GaSb at source side are chosen with the uniformly doping profile. To optimize the performance of the heterostructure device, more mole fraction x of aluminum is investigated in the drain and channel side as AlxGa1-xSb. By increasing the Al fraction, the bandgap energy of AlxGa1-xSb becomes larger, and as a result, the tunneling probability at the channel/drain interface decreases according to Eq. (1). The transfer characteristic of the heterostructure EDTFET with different Al composition (x) values is presented in Fig. 8. It is observed that, by the increment of the value of x, off current is effectively reduced and consequently suppressed the ambipolar behavior because of gate-induced drain leakage (GIDL) at the drain and channel junction. The extracted Ion, Ioff, Ion/Ioff ratio, Iamb, SSave, and Vth as a function of Al composition are illustrated in Fig. 9. It is explicit that Ion, Ioff, and Iamb reduce by increasing of mole fraction x. Therefore, higher Ion, lower Iamb, and Ioff cannot occur at the same time. Hence, by trading-off between the above parameters, Al mole fraction is chosen 10% (x = 0.1). In spite of reducing on-current by increasing Al mole fraction, as shown in Fig. 8, Ion is still improved compared to the conventional Si-EDTFET, in addition to reduce Ioff, Iamb by selecting 0.1 for Al mole fraction. By extracting from the transfer characteristic (Id–Vgs) of Al0.1GaSb–GaSb–EDTFET device, Ion is 0.25 mA/μm, Ioff is 2.2 × 10−18 A/μm, Iamb is 3 × 10−18 A/μm, Vth is 0.63 V, and SSave is 59 mV/dec.

In the following, the combination of the two above methods, heterostructure and Gaussian-doping profile, on EDTFET (GD–Al0.1GaSb–GaSb–EDTFET) is investigated and DC parameters’ device is obtained using the extract of transfer characteristic (Id-Vgs). SSp is 37 mV/dec, Ion is 6.2 × 10−5 A/μm, Ioff is 1.7 × 10−19 A/μm, Ion/Ioff ratio is 3.6 × 1014, and Iamb is 1.3 × 10−23 A/μm. Therefore, it is clear that Iamb has declined sharply.

Figure 10 shows a comparison between the two methods and the blend of them based on Id–Vgs curve. As it is explicit from the figure, the method of the applying Gaussian-doping profile, GD–GaSb–EDTFET, and the use of the heterostructure (Al0.1GaSb–GaSb–EDTFET) results in almost the same decrease in Iamb. However, by combining these two methods, GD–Al0.1 GaSb–GaSb–EDTFET, Ioff is decreased and Iamb is sharply reduced. However, from Ion and Vth point of view, both of them are slightly undermined.

According to the results obtained in Table 2, Ion, Ioff, Ion/Ioff, Iamb, and Vth of both the proposed devices) GD–GaSb–EDTFET and GD–Al0.1GaSb–GaSb–EDTFET( have been improved as compared with the conventional Si-EDTFET device; therefore, both the proposed devices are the suitable candidates for analog and digital applications. By the comparison of the two proposed devices with each other and based on the results of Table 2, transconductance and cut-off frequency curves (Fig. 11), it can be found that the GD–GaSb–EDTFET is more suitable for analog applications because of higher amounts of Ion, gm, fT, and Vth than those of the GD–Al0.1GaSb–GaSb–EDTFET. In addition, Ioff, Iamb, the Ion/Ioff ratio, and the SSP extracted from the GD–Al0.1GaSb–GaSb–EDTFET are better than the GD–GaSb–EDTFET, so the GD–Al0.1GaSb–GaSb–EDTFET is the more proper candidate for digital applications.

Conclusion

In this paper, a junctionless tunnel field-effect transistor was simulated based on electrically doped concept using two-dimensional Silvaco TCAD. To increase on-state current, GaSb, a III–V semiconductor, was used which has narrow bandgap and high carrier mobility. On-state current with a value of 0.25 mA/μm at Vds = 1 V and Vgs = 1.2 V in case of GaSb–EDTFET was found to increase significantly compared to the conventional EDTFET. Then, the Gaussian-doping profile was used to reduce Ioff and Iamb. Wherein Iamb is 9.9 × 10−19 A/μm, Ioff is 1.2 × 10−18 A/μm, Ion is 2.5 × 10−4 A/μm, Ion/Ioff ratio is 2.1 × 1014, and the subthreshold swing (SS) is 56 mV/dec. In the process of improving the performance of the device at both the analog and digital applications, heterostructure source/channel interface was used; therefore, GaSb was allocated to source and AlGaSb to channel and drain regions. Then, the optimal Al composition for AlGaSb was founded to be around 10% (x = 0.1) by trading-off DC characteristics. The next Gaussian-doping profile was used in drain and channel. This Gaussian structure called the GD–Al0.1GaSb–GaSb–EDTFET has Iamb of 1.3 × 10−23 A/μm, Ioff of 1.7 × 10−19 A/μm, Ion of 6.2 × 10− 5 A/μm, the Ion/Ioff ratio of 3.6 × 1014, and SS of 37 mV/dec, which has a remarkable improvement over the conventional Si-EDTFET. fT and gm of devices were also investigated and the results demonstrated that the proposed devices were significantly better as compared with the conventional EDTFET. According to the numerical simulations, these proposed devices can also be the suitable candidates for analog and digital applications.

References

Boucart, K., Ionescu, A.M.: Double-gate tunnel FET with high-k gate dielectric. IEEE Trans. Electron Dev. 54(7), 1725–1733 (2007)

Pal, A., Dutta, A.K.: Analytical drain current modeling of double-gate tunnel field-effect transistors. IEEE Trans. Electron Dev. 63(8), 3213–3221 (2016)

Ionescu, A.M., Riel, H.: Tunnel field-effect transistors as energy-efficient electronic switches. Nature 479(7373), 329–338 (2011)

Colinge, J.P.: FinFETs and Other Multi-gate Transistors, vol. 73. Springer, New York (2008)

Kim, S.H., Yokoyama, M., Nakane, R., Ichikawa, O., Osada, T., Hata, M., Takenaka, M., Takagi, S.: High performance tri-gate extremely thin-body InAs-on-insulator MOSFETs with high short channel effect immunity and V th tunability. IEEE Trans. Electron Dev. 61(5), 1354–1360 (2014)

Sharma, D., Vishvakarma, S.K.: Precise analytical model for short-channel quadruple-gate gate-all-around MOSFET. IEEE Trans. Nanotechnol. 12(3), 378–385 (2013)

Colinge, J.P., Lee, C.W., Afzalian, A., Akhavan, N.D., Yan, R., Ferain, I., Razavi, P., O’neill, B., Blake, A., White, M., Kelleher, A.M.: Nanowire transistors without junctions. Nat. Nanotechnol. 5(3), 225–229 (2010)

Bhuwalka, K.K., Schulze, J., Eisele, I.: Scaling the vertical tunnel FET with tunnel bandgap modulation and gate workfunction engineering. IEEE Trans. Electron Dev. 52(5), 909–917 (2005)

Nirschl, T., Fischer, J., Fulde, M., Bargagli-Stoffi, A., Sterkel, M., Sedlmeir, J., Weber, C., Heinrich, R., Schaper, U., Einfeld, J., Neubert, R.: Scaling properties of the tunneling field effect transistor (TFET): device and circuit. Solid-State Electr. 50(1), 44–51 (2006)

Zhang, Q., Zhao, W., Seabaugh, A.: Low-subthreshold-swing tunnel transistors. IEEE Electron Dev. Lett. 27(4), 297–300 (2006)

Wang, P.F., Hilsenbeck, K., Nirschl, T., Oswald, M., Stepper, C., Weis, M., Schmitt-Landsiedel, D., Hansch, W.: Complementary tunneling transistor for low power application. Solid-State Electr. 48(12), 2281–2286 (2004)

Choi, W.Y., Park, B.G., Lee, J.D., Liu, T.J.K.: Tunneling field-effect transistors (TFETs) with subthreshold swing (SS) less than 60 mV/dec. IEEE Electron Dev. Lett. 28(8), 743–745 (2007)

Kao, K.H., Verhulst, A.S., Vandenberghe, W.G., Soree, B., Groeseneken, G., De Meyer, K.: Direct and indirect band-to-band tunneling in germanium-based TFETs. IEEE Trans. Electron Dev. 59(2), 292–301 (2012)

Yadav, D.S., Sharma, D., Raad, B.R., Bajaj, V.: Impactful study of dual work function, underlap and hetero gate dielectric on TFET with different drain doping profile for high frequency performance estimation and optimization. Superlattices Microstruct. 96, 36–46 (2016)

Rahi, S.B., Asthana, P., Gupta, S.: Heterogate junctionless tunnel field-effect transistor: future of low-power devices. J. Comput. Electron. 16(1), 30–38 (2017)

Abdi, D.B., Kumar, M.J.: Controlling ambipolar current in tunneling FETs using overlapping gate-on-drain. IEEE J. Electron Dev. Soc. 2(6), 187–190 (2014)

Vladimirescu, A., Amara, A., Anghel, C.: An analysis on the ambipolar current in Si double-gate tunnel FETs. Solid-State Electr. 70, 67–72 (2012)

Nigam, K., Sharma, D.: Approach for ambipolar behaviour suppression in tunnel FET by workfunction engineering. Micro Nano Lett. 11(8), 460–464 (2016)

Madan, J., Chaujar, R.: Gate drain underlapped-PNIN-GAA-TFET for comprehensively upgraded analog/RF performance. Superlattices Microstruct. 102, 17–26 (2017)

Ilatikhameneh, H., Ameen, T.A., Klimeck, G., Appenzeller, J., Rahman, R.: Dielectric engineered tunnel field-effect transistor. IEEE Electron Dev. Lett. 36(10), 1097–1100 (2015)

Vijayvargiya, V., Vishvakarma, S.K.: Effect of drain doping profile on double-gate tunnel field-effect transistor and its influence on device RF performance. IEEE Trans. Nanotechnol. 13, 974–981 (2014)

Raad, B., Nigam, K., Sharma, D., Kondekar, P.: Dielectric and work function engineered TFET for ambipolar suppression and RF performance enhancement. Electron. Lett. 52(9), 770–772 (2016)

Ghosh, B., Bal, P., Mondal, P.: A junctionless tunnel field effect transistor with low subthreshold slope. J. Comput. Electron. 12(3), 428–436 (2013)

Goswami, Y., Ghosh, B., Asthana, P.K.: Analog performance of Si junctionless tunnel field effect transistor and its improvisation using III–V semiconductor. RSC Adv. 4(21), 10761–10765 (2014)

Ghosh, B., Akram, M.W.: Junctionless tunnel field effect transistor. IEEE Electron Dev. Lett. 34(5), 584–586 (2013)

Anand, S., Amin, S.I., Sarin, R.K.: Performance analysis of charge plasma based dual electrode tunnel FET. J. Semicond. 37(5), 054003 (2016)

Rahi, S.B., Ghosh, B.: High-k double gate junctionless tunnel FET with a tunable bandgap. RSC Adv. 5(67), 54544–54550 (2015)

Nigam, K., Pandey, S., Kondekar, P.N., Sharma, D., Parte, P.K.: A barrier controlled charge plasma-based TFET with gate engineering for ambipolar suppression and RF/linearity performance improvement. IEEE Trans. Electron Dev. 64(6), 2751–2757 (2017)

Akram, M.W., Ghosh, B., Bal, P., Mondal, P.: P-type double gate junctionless tunnel field effect transistor. J. Semicond. 35(1), 014002 (2014)

Nigam, K., Pandey, S., Kondekar, P., Sharma, D., Verma, M., Gedam, A.: Performance estimation of polarity controlled electrostatically doped tunnel field-effect transistor. Micro Nano Lett. 12(4), 239–244 (2017)

Nigam, K., Kondekar, P., Sharma, D., Raad, B.R.: A new approach for design and investigation of junction-less tunnel FET using electrically doped mechanism. Superlattices Microstruct. 98, 1–7 (2016)

Lahgere, A., Sahu, C., Singh, J.: Electrically doped dynamically configurable field-effect transistor for low-power and high-performance applications. Electron. Lett. 51(16), 1284–1286 (2015)

Anand, S., Sarin, R.K.: Analog and RF performance of doping-less tunnel FETs with Si0.55Ge0.45 source. J. Comput. Electron. 15(3), 850–856 (2016)

Kumar, M.J., Janardhanan, S.: Doping-less tunnel field effect transistor: design and investigation. IEEE Trans. Electron Dev. 60(10), 3285–3290 (2013)

Cecil, K., Singh, J.: Influence of Germanium source on dopingless tunnel-FET for improved analog/RF performance. Superlattices Microstruct. 101, 244–252 (2017)

Thathachary, A.V., Agrawal, N., Liu, L., Datta, S.: Electron transport in multigate Inx Ga1–xAs nanowire FETs: from diffusive to ballistic regimes at room temperature. Nano Lett. 14(2), 626–633 (2014)

Lahgere, A., Panchore, M., Singh, J.: Dopingless ferroelectric tunnel FET architecture for the improvement of performance of dopingless n-channel tunnel FETs. Superlattices Microstruct. 96, 16–25 (2016)

Abadi, R.M.I., Ziabari, S.A.S.: Representation of type I heterostructure junctionless tunnel field effect transistor for high-performance logic application. Appl. Phys. A 122(6), 616 (2016)

Rahi, S.B., Ghosh, B., Bishnoi, B.: Temperature effect on hetero structure junctionless tunnel FET. J. Semicond. 36(3), 034002 (2015)

Asthana, P.K., Goswami, Y., Basak, S., Rahi, S.B., Ghosh, B.: Improved performance of a junctionless tunnel field effect transistor with a Si and SiGe heterostructure for ultra low power applications. RSC Adv. 5(60), 48779–48785 (2015)

Gundapaneni, S., Konar, A., Bajaj, M., Murali, K.: Improved performance of junctionless tunnel FETs with source/channel heterostructure. In: Jain, V., Verma, A. (eds.) Physics of Semiconductor Devices. Environmental Science and Engineering, pp. 289–290. Springer, Cham (2013)

Cecil, K., Singh, J.: Performance enhancement of dopingless tunnel-FET based on Ge-source with high-k. IEEE International Symposium on Nanoelectronic and Information Systems, pp.19–22 (2015)

Tirkey, S., Nigam, K., Pandey, S., Sharma, D., Kondekar, P.: Investigation of gate material engineering in junctionless TFET to overcome the trade-off between ambipolarity and RF/linearity metrics. Superlattices Microstruct. 109, 307–315 (2017)

Abadi, R.M.I., Ziabari, S.A.S.: Improved performance of nanoscale junctionless tunnel field-effect transistor based on gate engineering approach. Appl. Phys. A. 122(11), 988 (2016)

Bal, P., Ghosh, B., Mondal, P., Akram, M.W., Tripathi, B.M.M.: Dual material gate junctionless tunnel field effect transistor. J. Comput. Electr. 13(1), 230–234 (2014)

Bashir, F., Loan, S.A., Rafat, M., Alamoud, A.R.M., Abbasi, S.A.: A high performance gate engineered charge plasma based tunnel field effect transistor. J. Comput. Electron. 14(2), 477–485 (2015)

Rahimian, M., Fathipour, M.: Improvement of electrical performance in junctionless nanowire TFET using hetero-gate-dielectric. Mater. Sci. Semicond. Process. 63, 142–152 (2017)

Anand, S., Sarin, R.K.: Dual material gate doping-less tunnel FET with hetero gate dielectric for enhancement of analog/RF performance. J. Semicond. 38(2), 024001 (2017)

Raad, B.R., Nigam, K., Sharma, D., Kondekar, P.N.: Performance investigation of bandgap, gate material work function and gate dielectric engineered TFET with device reliability improvement. Superlattices Microstruct. 94, 138–146 (2016)

Ram, M.S., Abdi, D.B.: Dopingless PNPN tunnel FET with improved performance: design and analysis. Superlattices Microstruct. 82, 430–437 (2015)

Goswami, Y., Asthana, P., Basak, S., Ghosh, B.: Junctionless tunnel field effect transistor with nonuniform doping. Int. J. Nanosci. 14(03), 1450025 (2015)

Aghandeh, H., Ziabari, S.A.S.: Gate engineered heterostructure junctionless TFET with Gaussian doping profile for ambipolar suppression and electrical performance improvement. Superlattices Microstruct. 111, 103–114 (2017)

Ahish, S., Sharma, D., Vasantha, M.H., Kumar, Y.B.N.: Device and circuit level performance analysis of novel InAs/Si heterojunction double gate tunnel field effect transistor. Superlattices Microstruct. 94, 119–130 (2016)

Visciarelli, M., Gnani, E., Gnudi, A., Reggiani, S., Baccarani, G.: Impact of strain on tunneling current and threshold voltage in III–V nanowire TFETs. IEEE Electron Dev. Lett. 37(5), 560–563 (2016)

Abadi, R.M.I., Ziabari, S.A.S.: Representation of strained gate-all-around junctionless tunneling nanowire filed effect transistor for analog applications. Microelectron. Eng. 162, 12–16 (2016)

Yadav, D.S., Verma, A., Sharma, D., Tirkey, S., Raad, B.R.: Comparative investigation of novel hetero gate dielectric and drain engineered charge plasma TFET for improved DC and RF performance. Superlattices Microstruct. 111, 123–133 (2017)

Yadav, D.S., Raad, B.R., Sharma, D.: A novel gate and drain engineered charge plasma tunnel field-effect transistor for low sub-threshold swing and ambipolar nature. Superlattice Microstruct 100(266), 266–273 (2016)

Yogesh, G., Pranav, A., Bahniman, G.: Nanoscale III–V on Si-based junctionless tunnel transistor for EHF band applications. Nanoscale 38(5), 054002 (2017)

Chin, V.W.L.: Electron mobility in GaSb. Solid-State Electr. 38(1), 59–67 (1995)

Silvaco Inc.: Atlas User’s Manual. Silvaco Inc., Santa Clara (2017)

Sze, S.M., Ng, K.K.: Physics of Semiconductor Devices. Wiley (2007)

Asthana, P.K., Ghosh, B., Rahi, S.B.M., Goswami, Y.: Optimal design for a high performance H-JLTFET using hfo2 as a gate dielectric for ultra low power applications. RSC Adv. 4(43), 22803–22807 (2014)

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Open Access This article is distributed under the terms of the Creative Commons Attribution 4.0 International License (http://creativecommons.org/licenses/by/4.0/), which permits unrestricted use, distribution, and reproduction in any medium, provided you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made.

About this article

Cite this article

Abedini, M., Sedigh Ziabari, S.A. & Eskandarian, A. Representation of heterostructure electrically doped nanoscale tunnel FET with Gaussian-doping profile for high-performance low-power applications. Int Nano Lett 8, 277–286 (2018). https://doi.org/10.1007/s40089-018-0250-6

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s40089-018-0250-6