Abstract

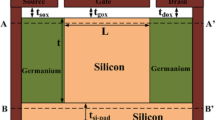

Ge-source dopingless tunnelling field effect transistor (Ge-source DLTFET) with the optimization of dielectric oxide thickness under the source and the gate contacts is proposed and investigated by calibrated 2D TCAD device simulation. As the structure is realized using dopingless technique, this enables lower thermal budget, higher immunity towards the random dopant fluctuations (RDFs) effects and velocity degradation effects. The optimization of dielectric thickness has been done to tune the carrier concentrations induced in source and channel regions in order to improve the device performance. The drive current is magnificently enhanced along with ION/IOFF ratio, peak transconductance and ultra-steep subthreshold slope (SS) is reported for the optimized Si-DLTFET. In addition to this by deploying Ge-source instead of Si source in optimized Si-DLTFET increases ON current slightly and OFF current gets reduced by the order of two as compared to the optimized Si-DLTFET. This improves the ION/IOFF ratio, the reported drive current for Ge-source DLTFET is 5.1 × 10−4 A/μm, along with ION/IOFF ratio as 1.54 × 1013, peak transconductance as 1.26 mS/μm and ultra-steep SS as 1.69 mV/decade. Further, the analog, RF and linearity performance parameters have also been investigated for both the structures and demonstrated notable improvement. The energy efficiency investigation reveals a significant reduction in energy-delay product. Further the linearity analysis is also presented for the reported device structure. This paper indicates the potentials of optimized Si-DLTFET and Ge-source DLTFET as promising candidates for low power analog and RF applications and Ge-source DLTFET has better device dc performance.

Similar content being viewed by others

Data Availability

Not applicable.

References

Kilchytska V, Neve A, Vancaillie L, Levacq D, Adriaensen S, van Meer H, De Meyer K, Raynaud C, Dehan M, Raskin JP, Flandre D (2003) Influence of device engineering on the analog and RF performances of SOI MOSFETs. IEEE Transactions on Electron Devices 50(3):577–588

Kumar NM, Syamal B, Sarkar CK (2010) Influence of channel and gate engineering on the analog and RF performance of DG MOSFETs. IEEE Transactions on Electron Devices 57(4):820–826

Masuda H, Nakai M, Kubo M (1979) Characteristics and limitation of scaled-down MOSFET's due to two-dimensional field effect. IEEE Transactions on Electron Devices 26(6):980–986

Bangsaruntip S, Cohen GM, Majumdar A, Sleight JW (2010) Universality of short-channel effects in undoped-body silicon nanowire MOSFETs. IEEE Electron Device Letters 31(9):903–905

J.P. Colinge, FinFETs and other multi-gate transistors, New York: Springer, (Vol. 73),2008

Nirschl T, Fischer J, Fulde M, Bargagli-Sto A, Sterkel M, Sedlmeir J, Weber C, Heinrich R, Schaper U, Einfeld J, Neubert R (2006) Scaling properties of the tunnelling field effect transistor (TFET): device and circuit. Solid State Electron 50(1):44–51

Koswatta SO, Lundstrom MS, Nikonov DE (2009) Performance comparison between pin tunneling transistors and conventional MOSFETs. IEEE Transactions on Electron Devices 56(3):456–465

Boucart K, Riess W, Ionescu AM (2009) Lateral strain profile as key technology booster for all-silicon tunnel FETs. IEEE Electron Device Lett 30(6):656–658

Boucart K, Ionescu AM (2007) Double-gate tunnel FET with high-k gate dielectric. IEEE Trans Electron Devices 54(7):1725–1733

Choi WY, Park BG, Lee JD, Liu TJK (2007) Tunneling field-effect transistors (TFETs) with subthreshold swing (SS) less than 60 mV/dec. IEEE Electron Device Lett 28(8):743–745

Jhaveri R, Nagavarapu V, Woo JC (2010) Effect of pocket doping and annealing schemeson the source-pocket tunnel field-effect transistor. IEEE Transactions on Electron Devices 58(1):80–86

Kumar MJ, Nadda K (2012) Bipolar charge-plasma transistor: a novel three terminal device. IEEE Trans Electron Devices 59(4):962–967

Ramaswamy S, Kumar MJ (2014) Junctionless impact ionization MOS: proposal and investigation. IEEE Trans Electron Devices 61(12):4295–4298

Amin SI, Sarin RK (2015) Charge-plasma based dual-material and gate-stacked architecture of junctionless transistor for enhanced analog performance. Superlattice Microst 88:582–590

R.J. Hueting, B. Rajasekharan,C. Salm, and J. Schmitz, The charge plasma PN diode. IEEE Electron Device Lett, 29(12), pp. 1367–1369, 2008

Damrongplasit N, Shin C, Kim SH, Vega RA, Liu TJK (2011) Study of random dopant fluctuation effects in germanium-source tunnel FETs. IEEE Trans Electron Devices 58(10):3541–3548

Damrongplasit N, Kim SH, Liu TJK (2013) Study of random dopant fluctuation induced variability in the raised-Ge-source TFET. IEEE Electron Device Lett 34(2):184–186

Duan X, Zhang J, Wang S, Li Y, Xu S, Hao Y (2018) A high-performance gate engineered InGaN dopingless tunnel FET. IEEE Trans Electron Devices 65(3):1223–1229

Singh S, Kondekar PN (2017) A novel electrostatically doped ferroelectric Schottky barrier tunnel FET: process resilient design. J Comput Electron 16(3):685–695

Hur J, Moon DI, Han JW, Kim GH, Jeon CH, Choi YK (2017) Tunneling effects ina charge-plasma dopingless transistor. IEEE Trans Nanotechnol 16(2):315–320

Singh S, Singh AP, Kondekar PN (2017) A novel self-aligned charge plasma Schottky barrier tunnel FET using work function engineering. Microelectron Eng 168:67–75

Kumar MJ, Janardhanan S (2013) Doping-less tunnel field effect transistor: design and investigation. IEEE Trans Electron Devices 60(10):3285–3290

Nadda K, Kumar MJ (2015) Vertical bipolar charge plasma transistor with buried metal layer. Sci Reports 5:7860

Bashir F, Loan SA, Rafat M, Alamoud ARM, Abbasi SA (2015) A high-performance source engineered charge plasma-based Schottky MOSFET on SOI. IEEE Trans Electron Devices 62(10):3357–3364

Haynes WM (2014) CRC handbook of chemistry and physics. CRC press

Ranade P, Takeuchi H, King TJ, Hu C (2001) Work function engineering of molybdenum gate electrodes by nitrogen implantation. Electrochem Solid-State Lett 4(11):G85–G87

S. Saurabh, and M.J. Kumar, Fundamentals of tunnel field-effect transistors. CRC Press, 2016

ATLAS User Manual, Silvaco International, Santa Clara, CA (2015)

Singh S, Kondekar PN (2016) A novel process variation immune dopingless zero subthreshold slope and zero impact ionization FET (DL-Z2FET) based on transition metals. J Comput Electron 15(1):67–75

Singh S, Kondekar PN, Singh AP (2017) Investigation of analog/radio frequency figures-of-merits of charge plasma schottky barrier tunnel field effect transistor. J Nanoelectron Optoelectron 12(4):365–374

Singh S, Kondekar PN, Sinha R (2017) Estimation of analog/radiofrequency figures-of-merits and circuit performance of dynamically reconfigurable electrostatically doped silicon nanowire schottky barrier FET. J Nanoelectron Optoelectron 12(4):343–351

Bashir F, Loan SA, Rafat M, Alamoud ARM, Abbasi SA (2015) A high performance gate engineered charge plasma based tunnel field effect transistor. J Comput Electron 14(2):477–485

Loan SA, Kumar S, Alamoud AM (2016) A novel double gate metal source/drain Schottky MOSFET as an inverter. Superlattice Microst 91:78–89

S.H. Kim, H. Kam, C. Hu, and T.J.K. Liu, Germanium-source tunnel field effect transistors with record high ION/IOFF. Symposium on VLSI Technology, pp. 178–179, 2009

Singh S, Kondekar PN, Jaiswal NK (2016) Label-free biosensor using Nanogap embedded dielectric modulated Schottky tunneling source impact ionization MOS. Microelectron Eng 149:129–134

N. Mendiratta, and S.L. Tripathi, 18nm n-channel and p-channel Dopingless asymmetrical Junctionless DG-MOSFET: low power CMOS based digital and memory applications, 2021

M. Sajad, A. Singh, N. Kumar, S.I. Amin, and S. Anand, Design and analysis of negative capacitance based dual material dopingless tunnel FET. Superlattices and Microstructures, pp. 106964, 2021

Arun AV, Sruthy KS, Jacob J Dual material gate tunnel field effect transistor based Dopingless 1T DRAM. In 2021 international conference on communication, control and information sciences (ICCISc) (Vol. 1, pp. 1-5). IEEE, 2021. June

M. Caymax, G. Eneman, F. Bellenger, C. Merckling, A. Delabie, G. Wang, R. Loo, E. Simoen, J. Mitard, B. De Jaeger, et al. Germanium for advanced CMOS anno 2009: A SWOT analysis. In Proceedings of the IEEE International Electron Devices Meeting (IEDM), Baltimore, MD, USA, 7–9 December 2009

Kuzum D, Krishnamohan T, Nainani A, Sun Y, Pianetta PA, Wong HS, Saraswat KC (2011) High-mobility Ge N-MOSFETs and mobility degradation mechanisms. IEEE Trans Electron Devices 58:59–66

H. Matsubara, T. Sasada, M. Takenaka, and S. Takagi, Evidence of low interface trap density in GeO2/Ge metal-oxide-semiconductor structures fabricated by thermal oxidation. Appl Phys Lett. 93(3), p.032104, 2008

Acknowledgements

The authors are grateful to the National Institute of Technology, Jamshedpur, India for providing the computational resources.

Author information

Authors and Affiliations

Contributions

All authors have equal contribution.

Corresponding author

Ethics declarations

Ethics Approval and Consent to Participate

Not applicable.

Consent for Publication

Author’s name

Kumari Nibha Priyadarshani.

Sangeeta Singh.

Kunal Singh.

Affiliation

National Institute of Technology Patna, India.

National Institute of Technology Patna, India.

National Institute of Technology Jamshedpur, India.

Conflicts of Interest/Competing Interests

The authors declare that there are no conflicts of interest related to this article.

Additional information

Publisher’s Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Priyadarshani, K.N., Singh, S. & Singh, K. Ultra Steep Ge-Source Dopingless Tunnelling Field Effect Transistor with Enhanced Drive Current: DC to Linearity Characteristics Analysis. Silicon 14, 5863–5876 (2022). https://doi.org/10.1007/s12633-021-01339-2

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s12633-021-01339-2