Abstract

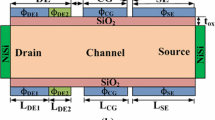

This work investigates a process-variation resilient electrostatically-doped ferroelectric Schottky-barrier tunnel FET (ED-FE-SB-TFET) based on negative capacitance (NC). The key attributes of ED-FE-SB-TFET are perovskite ferroelectric (FE) gate stack-induced NC behavior and electrostatic doping to induce pockets at both source/drain and channel interfaces. The positive feedback among the electric dipoles in FE material leads to intrinsic voltage amplification and enhanced gate controllability, thus it facilitates faster switching transitions. The proposed ED-FE-SB-TFET endeavors to create a substantial reduction in the ambipolar current (\(I_\mathrm{Amb}\)), steep sub-threshold slope, paramount boost in drive current, lower drain-induced barrier-lowering, and enhanced scalability. It also obviates the need for metallurgical doping, hence ion-implantation or dopant segregation techniques employed for planar SB-TFETs pocket-doping are no longer required, and it also modifies effective Schottky barrier height and Schottky tunneling barrier width significantly to enhance the device behavior. It offers a simplified fabrication process, and it is highly resilient towards process variations, doping control issues, and random dopant fluctuations. Moreover, there is a reduced thermal budget that facilitates its fabrication on single crystal silicon-on-glass substrate realized by wafer scale epitaxial transfer. Results reveal its potential as strong candidate for next generation, scaled and low power applications.

Similar content being viewed by others

References

Vardi, M.Y.: Moore’s law and the sand-heap paradox. Commun. ACM 57(5), 5–5 (2014)

Kuhn, K.J.: Considerations for ultimate CMOS scaling. IEEE Trans. Electron Devices 59(7), 1813–1828 (2012)

Salahuddin, S., Datta, S.: Use of negative capacitance to provide voltage amplification for low power nanoscale devices. Nano Lett. 8(2), 405–410 (2008)

Zhirnov Victor, V., Cavin, R.K.: Nanoelectronics: negative capacitance to the rescue ? Nat. Nanotechnol. 3(2), 77–78 (2008)

Singh, S., Pal, P., Mittal, R., Tamia, A., Kondekar, P.N.: Silicon on ferroelectric Tunnel FET (SOFTFET) for low power application. In: IEEE International Conference on Emerging Electronics (ICEE), pp. 1–3. IISc Bangalore (2014)

Salvatore, G.A., Bouvet, D., Ionescu, A.M.: Demonstration of subthrehold swing smaller than 60 mV/decade in Fe-FET with P (VDF-TrFE)/\(\text{Si}O_{2}\) gate stack. In: IEEE International Electron Devices Meeting (IEDM), pp. 1–4 (2008)

Alexandru, R., Salvatore, G.A., Jimenez, D., Ionescu, A.M.: Metal-ferroelectric-meta-oxide-semiconductor field effect transistor with sub-60 mV/decade subthreshold swing and internal voltage amplification. In: IEEE International Electron Devices Meeting (IEDM), pp. 16.1–16.3 (2010)

Ionescu, A.M., Lattanzio, L., Salvatore, G.A., De Michielis, L., Boucart, K., Bouvet, D.: The hysteretic ferroelectric tunnel FET. IEEE Trans. Electron Devices 57(12), 3518–3524 (2010)

Salvatore, G.A., Lattanzio, L., Bouvet, D., Ionescu, A.M.: Modeling the temperature dependence of Fe-FET static characteristics based on Landau’s theory. IEEE Trans. Electron Devices 58(9), 3162–3169 (2011)

Lee, M.H., Lin, J.C., Wei, Y.T., Chen, C.W., Tu, W.H., Zhuang, H.K., Tang, M.: Ferroelectric negative capacitance hetero-tunnel field-effect-transistors with internal voltage amplification. In: IEEE International Electron Devices Meeting (IEDM), pp. 4.5.1–4.5.4 (2013)

Jhaveri, R., Nagavarapu, V., Woo, J.: Asymmetric Schottky tunneling source SOI MOSFET design for mixed-mode applications. IEEE Trans. Electron Devices 56(1), 93–99 (2009)

Kim, J., Jhaveri, R., Woo, I.J., Yang, C.K.K.: Circuit-level performance evaluation of Schottky tunneling transistor in mixed-signal applications. IEEE Trans. Nanotechnol. 10(2), 291–299 (2011)

Guin, S., Chattopadhyay, A., Karmakar, A., Mallik, A.: Impact of a pocket doping on the device performance of a Schottky tunneling field-effect transistor. IEEE Trans. Electron Devices 61(7), 2515–2522 (2014)

Zhang, M., Knoch, J., Zhao, Q.T., Lenk, S., Breuer, U., Mantl, S.: Schottky barrier height modulation using dopant segregation in Schottky-barrier SOI-MOSFETs. In: Proceedings of 35th European IEEE Solid-State Device Research Conference, pp. 457–460 (2005)

Singh, S., Kondekar, P.N.: Dopingless super-steep impact ionisation MOS (dopingless-IMOS) based on work-function engineering. Electron. Lett. 50(12), 888–889 (2014)

Kumar, M.J., Nadda, K.: Bipolar charge-plasma transistor: a novel three terminal device. IEEE Trans. Electron Devices 59(4), 962–967 (2012)

Nadda, K., Jagadesh Kumar, M.: Schottky collector bipolar transistor without impurity doped emitter and base: design and performance. IEEE Trans. Electron Devices 60(9), 2956–2959 (2013)

Kumar, M.J., Janardhanan, S.: Doping-less tunnel field effect transistor: design and investigation. IEEE Trans. Electron Devices 60(10), 3285–3290 (2013)

Singh, S., Kondekar, P.N.: Circuit performance & sensitivity analysis of charge plasma based super-steep negative capacitance junctionless tunnel field effect transistor. J. Nanoelectron. Optoelectron. 12(5), 442–451 (2017)

Singh, S., Singh, A.P., Kondekar, P.N.: A novel self-aligned charge plasma Schottky barrier tunnel FET using work function engineering. Microelectron. Eng. 168, 67–75 (2017)

Singh, S., Kondekar, P.N., Singh, A.P.: Investigation of analog/RF figures-of-merits of charge plasma Schottky barrier tunnel FET. J. Nanoelectron. Optoelectron. (Accepted)

Teh, W.H., Trigg, A., Tung, C.H., Kumar, R., Balasubramanian, N., Kwong, D.L.: 200 mm wafer-scale epitaxial transfer of single crystal Si on glass by anodic bonding of silicon-on-insulator wafers. Appl. Phys. Lett. 87(7), 073107 (2005)

Nadda, K., Kumar, M.J.: Thin-film bipolar transistors on recrystallized polycrystalline silicon without impurity doped junctions: proposal and investigation. J. Disp. Technol. 10(7), 590–594 (2014)

Kima, H.S., Blick, R.H., Kim, D.M., Eom, C.B.: Bonding siliconon-insulator to glass wafers for integrated bio-electronic circuits. Appl. Phys. Lett. 85(12), 2370–2372 (2004)

ATLAS Device Simulation Soft: Silvaco. Santa Clara, CA, USA (2012)

Kale, S., Kondekar, P.N.: Ferroelectric Schottky barrier tunnel FET with gate-drain underlap. Superlattices Microstruct. 89, 225–230 (2016)

Mehta, H., Kaur, H.: Modeling and simulation study of novel Double Gate Ferroelectric Junctionless (DGFJL) transistor. Superlattices Microstruct. 97, 536–547 (2016)

Saeidi, A., Biswas, A., Ionescu, A.M.: Modeling and simulation of low power ferroelectric non-volatile memory tunnel field effect transistors using silicon-doped hafnium oxide as gate dielectric. Solid State Electron. 124, 16–23 (2016)

Mikolajick, T., Müller, S., Schenk, T., Yurchuk, E., Slesazeck, S., Schröder, U., Flachowsky, S., van Bentum, R., Kolodinski, S., Polakowski, P., Müller, J.: Doped hafnium oxide—an enabler for ferroelectric field effect transistors. Adv. Sci. Technol. 95, 136–145 (2014)

Kojima, T., Sakai, T., Watanabe, T., Funakubo, H., Saito, K., Osada, M.: Large remanent polarization of \((Bi, Nd)_{4}Ti_{3}O_{12}\) epitaxial thin films grown by metalorganic chemical vapor deposition. Appl. Phys. Lett. 80(15), 2746–2748 (2002)

Shieh, J., Yeh, J.H., Shu, Y.C., Yen, J.H.: Hysteresis behaviors of barium titanate single crystals based on the operation of multiple 90 switching systems. Mater. Sci. Eng. B 161(1), 50–54 (2009)

Roy, A., Prasad, R., Auluck, S., Garg, A.: Engineering polarization rotation in ferroelectric bismuth titanate. Appl. Phys. Lett. 102(18), 182901 (2013)

Cross, L.E.: Ferroelectric ceramics: tailoring properties for specific applications. In: Ferroelectric Ceramics, pp. 1–85. Birkhäuser, Basel (1993)

Acknowledgements

Authors are thankful to Dr. Neeraj K. Jaiswal, faculty of Physics at PDPM-Indian Institute of Information Technology, Design and Manufacturing, Jabalpur, India, for his guidance in device physics. We also thank PDPM Indian Institute of Information Technology, Design and Manufacturing, Jabalpur for providing infrastructure facilities.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Singh, S., Kondekar, P.N. A novel electrostatically doped ferroelectric Schottky barrier tunnel FET: process resilient design. J Comput Electron 16, 685–695 (2017). https://doi.org/10.1007/s10825-017-0987-6

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10825-017-0987-6