Abstract

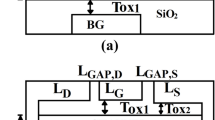

Doping-less tunnel field effect transistor (DLTFET) based on charged plasma (CP) concept has emerged as an energy-efficient transistor for low-power analog/RF and digital applications. With that in mind, we investigate a Si0.6Ge0.4/Ge heterojunction DLTEFT with a high-κ dielectric (HJ HD DLTFET). In this device, the drain is made up of Si0.6Ge0.4 and source, and the channel is made up of Germanium. Additionally, a high-κ dielectric (TiO2) has been used to suppress off-state current and provide better insulation. Moreover, a comparative analysis is performed between conventional DLTFET and HJ HD DLTFET using the ATLAS device simulator. The simulation results for HJ HD DLTFET offers an improvement in on-state current (~1000 μA/μm), improved ION/IOFF ratio (~1014), and subthreshold swing (~36.14 mV/decade) at 1.5 V of the gate voltage (VG) and 0.3 V of the drain voltage (VD). The distinguishable characteristics demonstrated by HJ HD DLTFET recommends its competence in low-voltage and low-power analog/RF applications.

Access this chapter

Tax calculation will be finalised at checkout

Purchases are for personal use only

Similar content being viewed by others

References

A.C. Seabaugh, Q. Zhang, Low-voltage tunnel transistors for beyond CMOS logic. Proc IEEE 98, 2095–2110 (2010). https://doi.org/10.1109/JPROC.2010.2070470

A.M. Ionescu, H. Riel, Tunnel field-effect transistors as energy-efficient electronic switches. Nature 479, 329–337 (2011). https://doi.org/10.1038/nature10679

A. Seabaugh, Fundamentals and current status of steep-slope tunnel field-effect transistors. Eur. Solid-State Device Res. Conf. 34–35 (2011). https://doi.org/10.1109/ESSDERC.2011.6044238

N. Damrongplasit, S.H. Kim, T.J.K. Liu, Study of random dopant fluctuation induced variability in the raised-ge-source TFET. IEEE Electron Device Lett. 34, 184–186 (2013). https://doi.org/10.1109/LED.2012.2235404

B.R. Raad, K. Nigam, D. Sharma, P.N. Kondekar, Performance investigation of bandgap, gate material work function and gate dielectric engineered TFET with device reliability improvement. Superlattices Microstruct 94, 138–146 (2016). https://doi.org/10.1016/j.spmi.2016.04.016

S. Sahoo, S. Dash, G.P. Mishra, Work-function modulated hetero gate charge plasma TFET to enhance the device performance, in Proceedings of 3rd International Conference on 2019 Devices for Integrated Circuit, DevIC 2019 (IEEE), pp. 461–464 (2019)

B. Raad, K. Nigam, D. Sharma, P. Kondekar, Dielectric and work function engineered TFET for ambipolar suppression and RF performance enhancement. Electron Lett 52, 770–772 (2016). https://doi.org/10.1049/el.2015.4348

G.D. Das, S. Dash, G.P. Mishra, Impact of hetero-dielectric engineering on the performance of single gate tunnel FET, in 2018 International Conference on Control, Power, Communication and Computing Technologies, ICCPCCT 2018 (IEEE, 2018), pp. 114–117

C. Anghel, P. Chilagani, A. Amara, A. Vladimirescu, Tunnel field effect transistor with increased on current, low-k spacer and high-k dielectric. Appl Phys Lett 96, 122104 (2010). https://doi.org/10.1063/1.3367880

A. Chattopadhyay, A. Mallik, Impact of a spacer dielectric and a gate overlap/underlap on the device performance of a tunnel field-effect transistor. IEEE Trans. Electron. Devices 58, 677–683 (2011). https://doi.org/10.1109/TED.2010.2101603

Y. Zhao, C. Wu, Q. Huang et al., A novel tunnel FET design through adaptive bandgap engineering with constant sub-threshold slope over 5 decades of current and high ION/IOFF Ratio. IEEE Electron. Device Lett. 38, 540–543 (2017). https://doi.org/10.1109/LED.2017.2679031

M. Haris, S.A. Loan, M. Mainuddin, Dual material gate dopingless InAs TFET for low power applications, in IMPACT 2017 - International Conference on Multimedia, Signal Processing and Communication Technologies (IEEE, 2018), pp. 114–117

B.V. Chandan, S. Dasari, K. Nigam et al., Impact of gate material engineering on ED-TFET for improving DC/analogue-RF/linearity performances. Micro Nano Lett. 13, 1653–1656 (2018). https://doi.org/10.1049/mnl.2018.5131

M.S. Ram, D.B. Abdi, Dopingless tunnel FET with a hetero-material gate: Design and analysis, in 2014 IEEE 2nd International Conference Emerging Electronics Mater to Devices, ICEE 2014 (2014), pp. 2–5. https://doi.org/10.1109/ICEmElec.2014.7151152

N.T.F. Transistor, S. Saurabh, M. Jagadesh Kumar, S. Member, Novel Attributes of a Dual Material Gate 58, 404–410 (2011)

V. Nagavarapu, R. Jhaveri, J.C.S. Woo, The tunnel source (PNPN) n-MOSFET: A novel high performance transistor. IEEE Trans. Electron Devices 55, 1013–1019 (2008). https://doi.org/10.1109/TED.2008.916711

M.J. Kumar, S. Janardhanan, Doping-less tunnel field effect transistor: Design and investigation. IEEE Trans. Electron Devices 60, 3285–3290 (2013). https://doi.org/10.1109/TED.2013.2276888

S.H. Kim, S. Agarwal, Z.A. Jacobson et al., Tunnel field effect transistor with raised germanium source. IEEE Electron Device Lett. 31, 1107–1109 (2010). https://doi.org/10.1109/LED.2010.2061214

M. Luisier, G. Klimeck, Atomistic full-band design study of InAs band-to-band tunneling field-effect transistors. IEEE Electron Device Lett. 30, 602–604 (2009). https://doi.org/10.1109/LED.2009.2020442

D.S. Yadav, D. Sharma, A. Kumar et al., Performance investigation of hetero material (InAs/Si)-based charge plasma TFET. Micro Nano Lett. 12, 358–363 (2017). https://doi.org/10.1049/mnl.2016.0688

H.W. Kim, J.H. Kim, S.W. Kim et al., Tunneling field-effect transistor with Si/SiGe material for high current drivability. Jpn. J. Appl. Phys. 53, 4 (2014). https://doi.org/10.7567/JJAP.53.06JE12

S. Sharma, B. Kaur, Performance investigation of asymmetric double-gate doping less tunnel FET with Si/Ge heterojunction. IET Circuits, Devices Syst. 14, 695–701 (2020). https://doi.org/10.1049/iet-cds.2019.0290

K.H. Kao, A.S. Verhulst, W.G. Vandenberghe et al., Direct and indirect band-to-band tunneling in germanium-based TFETs. IEEE Trans. Electron Devices 59, 292–301 (2012). https://doi.org/10.1109/TED.2011.2175228

H.K. Sung, H. Kam, C. Hu, T.J.K. Liu, Germanium-source tunnel field effect transistors with record high ION/IOFF. Dig. Tech Pap Symp. VLSI Technol. 178–179 (2009)

K.K. Bhuwalka, J. Schulze, I. Eisele, Performance enhancement of vertical tunnel field-effect transistor with SiGe in the δp+ layer. Jpn. J. Appl. Phys. Part 1 Regul. Pap. Short Notes Rev. Pap. 43, 4073–4078 (2004). https://doi.org/10.1143/JJAP.43.4073

S.-Y. Chung, Si/SiGe heterostructures: Materials, physics, quantum functional devices and their integration with heterostructure bipolar transistors (2005)

C. Anghel, P. Chilagani, A. Amara, A. Vladimirescu, Tunnel field effect transistor with increased on current, low-k spacer and high-k dielectric. Appl. Phys. Lett. 96, 4–7 (2010). https://doi.org/10.1063/1.3367880

B. Ghosh, M.W. Akram, Junctionless tunnel field effect transistor. IEEE Electron Device Lett. 34, 584–586 (2013). https://doi.org/10.1109/LED.2013.2253752

(2016) ATLAS User’s Manual, Silvaco. Santa Clara, CA, USA

W. Shockley, W.T. Read, Statistics of the recombinations of holes and electrons. Phys. Rev. 87, 835–842 (1952). https://doi.org/10.1103/PhysRev.87.835

K. Nigam, P. Kondekar, D. Sharma, DC characteristics and analog/RF performance of novel polarity control GaAs-Ge based tunnel field effect transistor. Superlattices Microstruct. 92, 224–231 (2016). https://doi.org/10.1016/j.spmi.2016.01.032

S. Mookerjea, R. Krishnan, S. Datta, V. Narayanan, On enhanced miller capacitance effect in interband tunnel transistors. IEEE Electron. Device Lett. 30, 1102–1104 (2009). https://doi.org/10.1109/LED.2009.2028907

Y. Yang, X. Tong, L.T. Yang et al., Tunneling field-effect transistor: Capacitance components and modeling. IEEE Electron. Device Lett. 31, 752–754 (2010). https://doi.org/10.1109/LED.2010.2047240

P.K. Verma, S.K. Gupta, An improved analog/RF and linearity performances with small-signal parameter extraction of virtually doped recessed source/drain dopingless junctionless transistor for radio-frequency applications. Silicon (2020). https://doi.org/10.1007/s12633-020-00518-x

T. Han, H. Liu, S. Chen et al., A doping-less tunnel field-effect transistor with Si0.6Ge0.4 heterojunction for the improvement of the on–off current ratio and analog/RF performance. Electronics 8, 574 (2019). https://doi.org/10.3390/electronics8050574

Author information

Authors and Affiliations

Corresponding author

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2022 The Author(s), under exclusive license to Springer Nature Singapore Pte Ltd.

About this paper

Cite this paper

Sharma, S., Basu, R., Kaur, B. (2022). Performance Evaluation of a Novel Si0.6Ge0.4/Ge Doping-Less TFET for Enhanced Low Power Analog/RF Applications. In: Dhawan, A., Tripathi, V.S., Arya, K.V., Naik, K. (eds) Recent Trends in Electronics and Communication. VCAS 2020. Lecture Notes in Electrical Engineering, vol 777. Springer, Singapore. https://doi.org/10.1007/978-981-16-2761-3_77

Download citation

DOI: https://doi.org/10.1007/978-981-16-2761-3_77

Published:

Publisher Name: Springer, Singapore

Print ISBN: 978-981-16-2760-6

Online ISBN: 978-981-16-2761-3

eBook Packages: EngineeringEngineering (R0)