Abstract

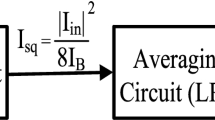

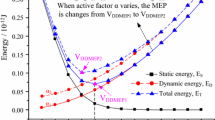

A high speed low power current-mode square-rooting/geometric-mean circuit is presented in this paper. The up-down topology with MOS translinear loop in sub-threshold is the basic building block of the proposed circuit which leads to lower supply voltage requirement and body effect issues. This design is also helpful to implement the square-rooting operation of a signal and geometric-mean of two variable signals both with adjustable gain. The performance has been simulated using HSPICE software in 0.18 µm TSMC (level-49 parameters) CMOS technology. Post-layout simulation results with 1-V DC supply voltage show that the maximum linearity error of 1.3%, the − 3 dB bandwidth of 21.9 MHz and maximum power consumption of 700 nW are granted. Monte Carlo analysis is also performed to ensure the stability and robustness of the circuit’s performance in the presence of the PVT (process, voltage and temperature) variations.

Similar content being viewed by others

References

Filanovsky, M., & Baltes, H. P. (1992). Simple CMOS analog square-rooting and squaring circuits. IEEE Transactions Circuits and Systems-I,39(4), 312–315.

Chaisayun, I. (2007). A current-mode square-rooting circuit using negative feedback technique. In The 2007 ECTI international conference (pp. 77–80).

Dejhan, K., & Netbut, C. (2007). New simple square-rooting circuits based on translinear current conveyors. International Journal of Electronics,94(7), 707–723.

Riewruja, V. (2008). Simple square-rooting circuit using OTAs. Electronics Letters,44(17), 1000–1002.

Sakul, Ch. (2008). A CMOS square-rooting circuits. In 23rd International technical conference on circuits/systems, computers and communications (ITC-CSCC2008) (pp. 537–540).

Riewruja, V., & Kamsri, T. (2009). Square-rooting and absolute function circuits using operational amplifiers. IET Circuits, Devices and Systems,3(2), 57–63.

Tangsrirat, W., Pukkalanun, T., Mongkolwai, P., & Surakampontorn, W. (2011). Simple current-mode analog multiplier, divider, square-rooter and squarer based on CDTAs. International Journal of Electronics and Communications (AEÜ),65(3), 198–203.

Shaterian, M., Twigg, C. M., & Azhari, S. J. (2013). An MTL-based configurable block for current-mode nonlinear analog computation. IEEE Transactions Circuits and Systems-II,60(9), 587–591.

AL-Absi, M. A., & As-Sabban, I. A. (2013). A new square-root circuit using short channel MOSFETs with compensation for error resulting from carrier mobility reduction. Lecture Notes on Photonics and Optoelectronics.,1(1), 6–8.

Thakral, B. (2015). Design of low power current mode square-root circuit. International Journal of Engineering and Manufacturing.,4, 23–29.

Al-Suhaibani, E. S., & Al-Absi, M. A. (2015). A new CMOS current-mode controllable-gain square rooting circuit using MOSFET in subthreshold. Analog Integrated Circuits and Signal Processing,82(2), 431–434.

Keleş, S., Keleş, F., & Kuntman, H. H. (2019). Square root circuit using FGMOS translinear principle. Analog Integrated Circuits and Signal Processing,98(1), 101–107.

Nikseresht, S., & Azhari, S. J. (2018). A new current-mode computational analog block free from the body-effect. Integration, the VLSI Journal. https://doi.org/10.1016/j.vlsi.2018.10.008.

Lopez-Martin, A. J., & Carlosena, A. (2003). A 1.5 V current-mode CMOS RMS-to-DC converter. Analog Integrated Circuits and Signal Processing,36(1), 137–143.

Kompitaya, P., & Kaewdang, Kh. (2011). A low-voltage low-power CMOS weak inversion true RMS-to-DC converter. Electronics, Computer, Telecommunications and Information Technology (ECTI),2011, 94–97.

Shaterian, M., Twigg, Ch M, & Azhari, S. J. (2015). MTL-based implementation of current-mode CMOS RMS-to-DC converters. International Journal of Circuit Theory and Applications,43(6), 793–805.

Toumazou, C., Lidgey, F. J., & Haigh, D. G. (1990). Analogue IC design: The current-mode approach. London: IEE Press.

Maryan, M. M., & Azhari, S. J. (2017). A MOS translinear cell-based configurable block for current-mode analog signal processing. Analog Integrated Circuits and Signal Processing,92(1), 1–13.

Seevinck, E., Vittoz, E. A., Plessis, M. D., Joubert, T.-H., & Beetge, W. (2000). CMOS translinear circuits for minimum supply voltage. IEEE Transactions Circuits and Systems-II,47(12), 1560–1564.

Maryan, M. M., & Azhari, S. J. (2018). CMOS design of computational current-mode static and dynamic functions based on analog translinear cell. Computers and Electrical Engineering,68, 629–645.

Tanno, K., Sugahara, Y., & Tamura, H. (2011). High-linear four-quadrant multiplier based on MOS weak-inversion region translinear principle with adaptive bias technique. TENCON,2011, 680–684.

Wiegerink, R. J., & Seevinck, E. (1993). Analysis and synthesis of MOS translinear loops. Dordrecht: Kluwer Academic Publisher.

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Maryan, M.M., Azhari, S.J. & Ghanaatian, A. An up-down topology based-current mode adjustable-gain square-rooting/geometric-mean circuit. Analog Integr Circ Sig Process 102, 283–291 (2020). https://doi.org/10.1007/s10470-019-01470-6

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-019-01470-6