Abstract

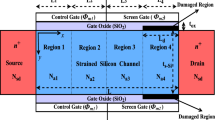

A new analytical model for the subthreshold swing of nanoscale undoped trigate silicon-on-insulator metal–oxide–semiconductor field-effect transistors (MOSFETs) is proposed, based on the channel potential distribution and physical conduction path concept. An analytical model for the potential distribution is obtained by solving the three-dimensional (3-D) Poisson’s equation, assuming a parabolic potential distribution between the lateral gates. In addition, mobile charges are considered in the model. The proposed analytical model is investigated and compared with results obtained from 3-D simulations using the ATLAS device simulator and experimental data. It is demonstrated that the analytical model predicts the subthreshold swing with good accuracy for different lengthes, thicknesses, and widths of channel.

Similar content being viewed by others

References

Iwai, H.: Roadmap for 22 nm and beyond. Microelectron. Eng. 86, 1520–1528 (2009)

Collaert, N., De Keersgieter, A., Dixit, A., Ferain, I., Lai, L.-S., Lenoble, D., Mercha, A., Nackaerts, A., Wong, H.-S.P., Boeuf, F.:Multi-gate devices for the 32 nm technology node and beyond. In: Solid-State Device Research Conference, pp. 143–146 (2007)

Lemnios, Z.J., Radack, D.J., Zolper, J.C.:The future of silicon-on-insulator (SOI) technology in microelectronic systems. In: Proceedings of the International SOI Conference, pp. 9–13 (2004)

Cristoloveanu, S., Ferlet-Cavrois, V.: Introduction to SOI MOSFETs: Context, radiation effects, and future trends. Int. J. High Speed Electron. Syst. 14(2), 465–487 (2004)

Ortiz-Conde, A., García-Sánchez, F. J.:Multi-gate 3-D SOI MOSFETs as the mainstream technology in high speed CMOS applications. In: Proceedings of the 11th IEEE International Symposium on EDMO, pp. 115–121 (2003)

Colinge, J.P.: FinFETs and Other Multi-Gate MOSFETs. Springer, Berlin (2008)

Son, A., Kim, J., Jeong, N., Choi, J., Shin, H.: Improved explicit current-voltage model for long-channel undoped surrounding-gate metal oxide semiconductor field effect transistor. J. Appl. Phys. 48, 412–413 (2009)

Frank, D.J., Dennard, R.H., Nowak, E., Solomon, P.M., Taur, Y., Wong, H.-S.P.: Device scaling limits of Si MOSFETs and their application dependencies. Proc. IEEE 89(3), 259–288 (2001)

Doyle, B., Arghavani, R., Barlage, D., Datta, S., Doczy, M., Kavalieros, J., Murthy, A., Chau, R.: Transistor elements for 30 nm physical gate lengths and beyond. Intel Technol. J. 6(2), 42–54 (2002)

Fossum, J.G., Trivedi, V. P., Wu, K.: Extremely scaled fully depleted SOI CMOS. In: Proceedings of the IEEE International SOI Conference, pp. 135–136 (2002)

Fossum, J.G.: Physical insights on nanoscale multi-gate CMOS design. Solid State Electron. 51(2), 188–194 (2007)

Tsormpatzoglou, A., Tassis, D.H., Dimitriadis, C.A., Ghibaudo, G., Collaert, N., Pananakakis, G.: Analytical threshold voltage model for lightly doped short-channel tri-gate MOSFETs. Solid State Electron. 57(1), 31–34 (2011)

Kloes, A., Weidemann, M., Iniguez, B.: Analytical 3D approach for modeling the electrostatic potential in triple-gate SOI MOSFETs. In: Proceedings of the IEEE Conference on Electron Devices Solid-State Circuits EDSSC, pp. 103–106 (2007)

Ferain, I., Colinge, C., Colinge, J.: Multigate transistors as the future of classical metal-oxide-semiconductor field-effect transistors. Nature 479(7373), 310–316 (2011)

Colinge, J.: Multiple-gate SOI MOSFETs. Solid State Electron. 48(6), 897–905 (2004)

Cartwright, J.: Intel enters the third dimension. Nature. (2011). doi:10.1038/news.2011.274. http://www.nature.com/news/2011/110506/full/news.2011.274.html

Ghani, T., Mistry, K., Packan, P., Thompson, S., Stettler, M., Tyagi, S., Bohr, M.: Scaling challenges and device design requirements for high performance sub 50 nm gate length planar CMOS transistors. In: VLSI Symposium on Digest of Technical Papers, pp. 174–175 (2000)

Pao, H.C., Sah, C.T.: Effects of diffusion current on characteristics of metal-oxide (insulator)-semiconductor transistors. Solid State Electron. 9(10), 927–937 (1966)

Yu, B., Song, J., Yuan, Y., Lu, W., Taur, Y.: A unified analytic drain-current model for multiple-gate MOSFETs. IEEE Trans. Electron Devices 55(8), 2157–2163 (2008)

Duarte, Sung-Jin Choi, J.P., Moon, Dong-Il, Ahn, Jae-Hyuk: A universal core model for multiple-gate field-effect transistors. Part I: charge model. IEEE Trans. Electron Devices 60(2), 840–848 (2013)

Duarte, Sung-Jin Choi, J.P., Moon, Dong-Il, Ahn, Jae-Hyuk: A universal core model for multiple-gate field-effect transistors. Part II: Drain current model. IEEE Trans. Electron Devices 60(2), 848–854 (2013)

Tsormpatzoglou, A., Dimitriadis, C., Clerc, R., Pananakakis, G., Ghibaudo, G.: Semianalytical modeling of short-channel effects in lightly doped silicon trigate MOSFETs. IEEE Trans. Electron Devices 55(10), 2623–2631 (2008)

Abd El Hamid, H., Guitart, J.R., Kilchytska, V., Flandre, D., Iniguez, B.: A 3-D analytical physically based model for the subthreshold swing in undoped trigate FinFETs. IEEE Trans. Electron Devices 54(9), 2487–2496 (2007)

Akarvardar, K., Mercha, A., Cristoloveanu, S., Gentil, P., Simoen, E., Subramanian, V., Claeys, C.: A two-dimensional model for interface coupling in triple-gate transistors. IEEE Trans. Electron Devices 54(4), 767–775 (2007)

Sun, Xin, Liu, Tsu-Jae King: Scale-length assessment of the trigate. IEEE Trans. Electron Devices 56(11), 2840–2842 (2009)

Young, K.K.: Short-channel effect in fully-depleted SOI MOSFETs. IEEE Trans. Electron Devices 36(2), 399–402 (1989)

Tsormpatzoglou, A., Dimitriadis, C.A., Clerc, R., Rafhay, Q., Pananakakis, G., Ghibaudo, G.: Semi-analytical modeling of short-channel effects in Si and Ge symmetrical double-gate MOSFETs. IEEE Trans. Electron Devices 54(8), 1943–1952 (2007)

Atlas User’s Manual, Device Simulation Software, software version, 5, Silvaco, Santa Clara (2008)

Vimala, P., Balamurugan, B.: Analytical model for nanoscale tri-gate SOI MOSFETs including quantum effects. IEEE Trans. Electron Devices 2(1), 1–7 (2014)

Tosaka, Y., Suzuki, K., Sugii, T.: Scaling-parameter-dependent model for subthreshold swing S in double-gate SOI MOSFET’s. IEEE Electron Device Lett. 15(11), 466–468 (1994)

Author information

Authors and Affiliations

Corresponding author

Appendices

Appendix A

Potential distribution

(a.1) \(C_{2}\) coefficient:

Inserting (35), (36), and (37) into (38), the coefficient \(C_{2}\) is obtained as a function of \(\varphi _\mathrm{f} (x)\) as follows:

(a.2) \(a_{2}(x, z)\):

Using Eq. 7 in Eq. 15, \(a_{2}\) is obtained as

(a.3) Coefficients \(k_{1}, k_{2}, \ldots , k_{8}\)

The coefficients \(k_{1}, k_{2}, \ldots , k_{8}\) are as follows:

(a.4) Tailor expansion

The Tailor expansion of the exponential term in Eq. 20 is as follows:

Appendix B

Subthreshold swing

where

Rights and permissions

About this article

Cite this article

Ghanatian, H., Hosseini, S.E. Analytical modeling of subthreshold swing in undoped trigate SOI MOSFETs. J Comput Electron 15, 508–515 (2016). https://doi.org/10.1007/s10825-016-0817-2

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10825-016-0817-2