Abstract

This study presents a gate-all-around InAs–Si vertical tunnel field-effect transistor with a triple metal gate (VTG-TFET). We obtained improved switching characteristics for the proposed design because of the improved electrostatic control on the channel and the narrow bandgap source. It shows an Ion of 392 μA/μm, an Ioff of 8.8 × 10−17 A/μm, an Ion/Ioff ratio of about 4.4 × 1012, and a minimum subthreshold slope of 9.3 mV/dec at Vd = 1 V. We also analyze the influence of the gate oxide and metal work functions on the transistor characteristics. A numerical device simulator, calibrated to the experimental data of a vertical InAs–Si gate all around TFET, is used to accurately predict different features of the device. Our simulations demonstrate that the proposed vertical TFET, as a fast-switching and very low power device, is a promising transistor for digital applications.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

Introduction

MOSFETs' scaling down to enhance the device performance and increment the integration density has been pursued for decades [1,2,3]. However, short-channel MOSFETs cannot meet low-power application requirements due to the non-scalable subthreshold slope (SS) at 25 °C. For solving this problem, TFETs have been introduced [4,5,6,7,8,9]. The band-to-band tunneling (BTBT) current mechanism in TFETs is based on controlling quantum tunneling across the barrier rather than modulating thermionic emission over a barrier as in conventional FETs. Despite sub-60 mV/dec subthreshold swing, large Ion to the Ioff current value (Ion/Ioff), and very low Ioff, low Ion, and ambipolar current are disadvantages of TFETs. Vertical TFETs (VTFETs) are proposed to resolve the shortcomings of conventional TFETs [10,11,12,13,14,15]. VTFETs benefit from tunneling all over the source-channel interface that enhances the tunneling current. Further improvement may be obtained by employing low-bandgap semiconductors like Ge, InAs, and SiGe in the source side [12, 16,17,18,19,20,21,22], and using heterojunction of III–V compounds at the source-channel interface [11, 23]. Although the techniques mentioned above have significantly enhanced the conventional TFETs' switching properties, but the obtained results are far away for real-world applications, particularly in terms of drive current. The other drawback is the complexity of the fabrication process of some of the proposed structures.

This paper proposes a gate-all-around InAs–Si vertical TFET with the Triple Metal Gate (TMG) and investigates its switching behavior by using a calibrated numerical device simulator. The main idea of our work is the enhancement of on-state current by employing a narrow bandgap source and improvement of the device electrostatics by using the triple metal gate technique. In the next section, we describe the device structure, study the device operation by using a calibrated simulation framework and investigate the switching characteristics. Finally, we compare the achievements made by our device against those of some recently developed TFETs and conclude the paper.

Device architecture

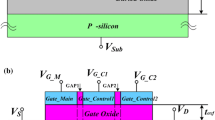

A 3-D view of the VTG-TFET is demonstrated in Fig. 1a. The device has an inverse T-shaped structure in which the InAs source region is located at the base, and silicon channel and drain sides are stacked on the source. The oxide region surrounds the Fin-shaped semiconductor region. Gate is symmetrically composed of three different metals, and their work functions are selected in a way that the best device performance is obtained. The channel length (LCH), the source length (LS), the drain length (LD), the channel thickness (TCH), and the dielectric thickness (TOX) are 50 nm, 70 nm, 30 nm, 10 nm, and 2 nm, respectively. It should be noted that HfO2 is employed as the gate oxide. The doping densities of the P-type InAs source area, the N-type silicon channel side, and the N-type silicon drain side are NS = 5 × 1019 cm−3, NCH = 5 × 1015 cm−3, and ND = 8 × 1018 cm−3, respectively. In order to reduce the ambipolar current, the drain region is not heavily doped. Figure 1b illustrates an InAs–Si gate all around TFET (GAA-TFET) that we use as a reference structure. SILVACO TCAD [24] is utilized as a simulation framework to investigate the device's electrical characteristics. We initially calibrated the simulator by regenerating the experimental results of a vertical InAs–Si TFET [25] to validate our simulation results, as depicted in Fig. 2.

Calibration of the I–V characteristic of vertical InAs–Si TFET [25] and silvaco results

Suitable physical models contain non-local BTBT, non-local trap-assisted tunneling (TAT), Shockley Read Hall (SRH) recombination, Fermi distribution, BGN, CVT, and drift–diffusion, are activated in the silvaco software. The effective tunneling masses of electron and hole are 0.322m0 and 0.549m0 for Si, and 0.026m0 and 0.57m0 for InAs, respectively [7, 26]. It should be noted that due to the large thickness of the Fin-shaped channel, the quantum confinement effects are not taken into account. The proposed and reference structures simulations consider two donor-like and acceptor-like traps with corresponding material-dependent parameters (shown in Table 1). As mentioned above, three metal gates are employed to modulate the energy bands and conduction of different channel parts and achieve the best switching performance of TFET. From the source side to the drain side, the work functions of the gate materials are set to 4.15 eV, 4.33 eV, and 4.15 eV, respectively. In Fig. 3, we show diagrams of energy bands for both devices in OFF-state (Vg = 0 V, Vd = 1 V) and ON-state (Vg = 1 V, Vd = 1 V) condition at the A–B cutline. As shown in the figures, using a narrow bandgap semiconductor in the source area expands the tunneling window across the junction in ON-state; moreover, the very low effective tunneling mass of charge carriers increases the BTBT tunneling rate. These features raise the Ion of the design structure. On another side, the OFF-state current may be considerably suppressed due to the straddling band alignment of the heterojunction and higher work function of the middle gate material.

A comparison among the transfer characteristics of VTG-TFET and that of reference structure is demonstrated in Fig. 4. We can understand from the figure that employing the triple metal gate (TMG) strategy leads to achieving a better electrostatic control on the channel and consequently lower Ioff, steeper SS, and higher ON-state current for the proposed structure. In Table 2, we evaluate the results of these TFETs quantitatively. As can be inferred from the table, we obtain a better ION/IOFF value in our VTG-TFET due to the lower Ioff and enhancement of the Ion current.

The lateral electric field of VTG-TFET and GAA-TFET along the A–B cutline at Vd = Vg = 1 V is shown in Fig. 5. It is known that the BTBT generation rate depends on the electric field; hence, it is expected that the proposed structure with a higher peak of the electric field and a steeper gradient of the energy bands profile at the tunneling junction provides a larger ON-state current. The BTBT value of both structures at the same bias points is illustrated in Fig. 6.

Figure 7 demonstrates the transfer characteristics of VTG-TFET at various drain voltages. As expected, the Ion increases by larger the drain voltage, while the Ioff and subthreshold slope are almost constant. In the short channel devices, the effect of the drain voltage variation on the electrostatic of the channel and tunneling distance enhances, and as a result, the transfer characteristic of the structure changes more. The proposed TFET's switching behavior is also studied for various gate oxide materials.

As shown in Fig. 8a, employing a dielectric material with higher-κ amplifies the electric field in the lateral position and at the tunneling interface. Furthermore, at the same applied voltages, it results in a smaller tunneling range (see Fig. 8b). Three different dielectric materials of HfO2 (ɛ = 25), Al2O3 (ɛ = 9), and SiO2 (ɛ = 3.9) are considered for the gate oxide. The enhanced electric field and shortened tunneling distance increase the BTBT generation rate for a device with higher-κ dielectric, as depicted in Fig. 8c. Figure 8d exhibits the I–V curve of VTG-TFET for three gate oxide materials. The steeper SS and higher Ion of the device with higher-κ dielectric are attributed to the increased electrostatic integrity of the channel and enhanced tunneling generation rate, respectively. In the multi-metal gate transistors, workfunction engineering to achieve the best device performance is necessary. Our device potentially has three metal gates with three various work functions. We name the workfunctions of the drain-side, middle and source-side gates, ϕ1, ϕ2, and ϕ3, respectively. Table 3 illustrates changing the Ion, Ioff, Ion/Ioff value, and subthreshold slope of VTG-TFET for ϕ2 = 4.33 eV and ϕ3 = 4.15 eV, while ϕ1 changes. It is expected that the work function of the drain-side gate has no significant impact on the switching specification of the design. The I–V curve for various of ϕ1 is plotted in Fig. 9.

The impact of the middle-gate workfunction is studied in Table 3. This gate can create a potential barrier at the middle of the channel that significantly blocks the leakage current and consequently reduces the off-state current.

It should be noted that ϕ2 does not modulate the on-state current considerably, as shown in Fig. 10.

The most influential work function on the switching performance of the device is that of source-side gate metal because of its vicinity to the tunneling junction. As depicted in Table 4, it can noticeably control the off-state current, on-state current and the steepness of the subthreshold slope. It is also illustrated in Fig. 11, where the I–V curve of VTG-TFET with various source-side gate metal work functions is exhibited. Ambipolar conduction is one of the main drawbacks of TFETs. In the case of VTG-TFET, we obtain the ambipolar characteristic of the design (as depicted in Fig. 12). It is anticipated that the ambipolarity is diminished noticeably due to the wide bandgap semiconductor employed in the channel-drain junction and different work functions of the gate metals.

For the sake of completeness, we propose a fabrication process flow to realize VTG-TFET, as depicted in Fig. 13. The fabrication methods of the vertical FETs are discussed in early studies [28,29,30]. Our proposed process starts with formation of a crystalline heterostructure of InAs/i-Si/Si (70/50/30 nm) using MOCVD on the silicon substrate. Then e-beam lithography is employed to create the SiO2 mask. TCP-RIE dry etching is carried out to form basic trapezoidal nanowire. The process is followed by anisotropic wet etching in TMAH acid to shrink the width of the nanowire. This method etches the nanowire layer under the oxide cover exclusively in the lateral direction that causes a very steep layer, as seen in Fig. 13a. The solution material helps to eliminate the plasma harm and even to clean the etched material surfaces. With such a technique, we can obtain the nanowire with a width of 10 nm. After removing the oxide mask, 2 nm ALD HfO2 gate oxide and the stack of metal gates are deposited (Fig. 13b2, b3, b4). Figure 13b-2 shows the metal 3 deposition. After that, we deposit the metal gate 2, and 1, and etched center between two FETs as shown Fig. 13b-3, and 4. Then 20 nm PECVD silicon dioxide were progressively deposited (Fig. 13b-5). The structure is covered with photoresist (PR), which facilitates eliminating the PR/SiO2/Metal/ HfO2 coats just at the top of the nanowire using dry etching (Fig. 13b-6). The oxide material surrounding the gate metals protects them from being etched, as seen in Fig. 13b-7. Additional oxide material is deposited and etched to enable formation of ohmic contacts (Fig. 13b-9). Finally, the metal electrodes have been created using rapid thermal annealing in N2 atmosphere. The complete architecture of the VTG-TFET (without isolation) is depicted in Fig. 13c.

Achievements made by the proposed TFET are given in Tab. 5 and are analyzed versus the certain recently released TFETs. The provided data demonstrate that VTG-TFET has a great result in low operational voltage and is a reasonable alternative for low-power applications. Figure 14a demonstrates the output characteristics for both devices. It is depicted that; the results confirm the improvement of Ion in the proposed device. Figure 14b shows the impact of trap states on the transfer characteristics of VTG-TFET.

In last section, we investigate the radio frequency (RF) characteristic for both devices. Figure 15a and b illustrates the transconductance (gm) and transition frequency (fT). The fT of FETs is given by [33, 34]:

As discussed, improvement of Ion in the proposed device leads the higher gm. The enhanced gm and lower parasitic capacitance in the VTG-TFET leads the higher fT which is depicted in Fig. 15b.

Conclusion

A gate-all-around vertical TFET based on the InAs–Si heterojunction with a triple metal gate is proposed in this paper. Because of its excellent switching capabilities, our device is demonstrated to be an attractive design in low-power digital applications. An Ion of 392 μA/μm, an Ioff of 8.8 × 10−17 A/μm, an Ion/Ioff current ratio of about 4.4 × 1012, and a minimum subthreshold slope (SS) of 9.3 mV/decade at 1 V operating voltage are obtained for VTG-TFET. The impact of gate metal work functions and gate dielectric materials are also investigated. To ensure the validation of the extracted data, the simulation software has been calibrated with the fabricated vertical InAs–Si gate-all-around TFET.

Availability of data and materials

The data that support the findings of this study are available from the corresponding author, upon reasonable request.

Change history

12 February 2024

A Correction to this paper has been published: https://doi.org/10.1186/s11671-024-03968-z

References

Makris N, Bucher M, Jazaeri F, Sallese JM. CJM: a compact model for double-gate junction FETs. IEEE J Electron Devices Soc. 2019;7(October):1191–9. https://doi.org/10.1109/JEDS.2019.2944817.

Moon DI, Choi SJ, Duarte JP, Choi YK. Investigation of silicon nanowire gate-all-around junctionless transistors built on a bulk substrate. IEEE Trans Electron Devices. 2013;60(4):1355–60. https://doi.org/10.1109/TED.2013.2247763.

Madadi D, Orouji AA. Investigation of 4H–SiC gate-all-around cylindrical nanowire junctionless MOSFET including negative capacitance and quantum confinements. Eur Phys J Plus. 2021;136(7):785. https://doi.org/10.1140/epjp/s13360-021-01787-0.

Bagga N, Dasgupta S. Surface potential and drain current analytical model of gate all around triple metal TFET. IEEE Trans Electron Devices. 2017;64(2):606–13. https://doi.org/10.1109/TED.2016.2642165.

Shaker A, Maged A, Elshorbagy A, AbouElainain A, Elsabbagh M. Source-all-around tunnel field-effect transistor (SAA-TFET): proposal and design. Semicond Sci Technol. 2020;35(2):025007. https://doi.org/10.1088/1361-6641/ab5d86.

Garg S, Saurabh S. Improving the scalability of SOI-based tunnel FETs using ground plane in buried oxide. IEEE J Electron Devices Soc. 2019;7:435–43. https://doi.org/10.1109/JEDS.2019.2907314.

Keighobadi D, Mohammadi S, Fathipour M. An analytical drain current model for the cylindrical channel gate-all-around heterojunction tunnel FETs. IEEE Trans Electron Devices. 2019;66(8):3646–51. https://doi.org/10.1109/TED.2019.2922232.

Liu KM, Cheng CP. Investigation on the effects of gate-source overlap/underlap and source doping gradient of n-type si cylindrical gate-all-around tunnel field-effect transistors. IEEE Trans Nanotechnol. 2020;19:382–9. https://doi.org/10.1109/TNANO.2020.2991787.

Oliva N, Backman J, Capua L, Cavalieri M, Luisier M, Ionescu AM. WSe2/SnSe2 vdW heterojunction tunnel FET with subthermionic characteristic and MOSFET co-integrated on same WSe2 flake. npj 2D Mater Appl. 2020;4(1):1–8. https://doi.org/10.1038/s41699-020-0142-2.

Hu VPH, Lin HH, Lin YK, Hu C. Optimization of negative-capacitance vertical-tunnel FET (NCVT-FET). IEEE Trans Electron Devices. 2020;67(6):2593–9. https://doi.org/10.1109/TED.2020.2986793.

Krishnaraja A, Svensson J, Lind E, Wernersson LE. Reducing ambipolar off-state leakage currents in III-V vertical nanowire tunnel FETs using gate-drain underlap. Appl Phys Lett. 2019. https://doi.org/10.1063/1.5115296.

Vanlalawpuia K, Bhowmick B. Investigation of a Ge-source vertical TFET with delta-doped layer. IEEE Trans Electron Devices. 2019;66(10):4439–45. https://doi.org/10.1109/TED.2019.2933313.

Memisevic E, Svensson J, Lind E, Wernersson LE. Vertical nanowire TFETs with channel diameter down to 10 nm and point SMIN of 35 mV/decade. IEEE Electron Device Lett. 2018;39(7):1089–91. https://doi.org/10.1109/LED.2018.2836862.

Cutaia D, et al. Vertical InAs-Si gate-all-around tunnel FETs Integrated on Si using selective epitaxy in nanotube templates. IEEE J Electron Devices Soc. 2015;3(3):176–83. https://doi.org/10.1109/JEDS.2015.2388793.

Tripathy MR, et al. Device and circuit-level assessment of GaSb/Si heterojunction vertical tunnel-FET for low-power applications. IEEE Trans Electron Devices. 2020;67(3):1285–92. https://doi.org/10.1109/TED.2020.2964428.

Li C, Yan ZR, Zhuang YQ, Zhao XL, Guo JM. Ge/Si heterojunction L-shape tunnel field-effect transistors with hetero-gate-dielectric. Chin Phys B. 2018. https://doi.org/10.1088/1674-1056/27/7/078502.

Paras N, Chauhan SS. A novel vertical tunneling based Ge-source TFET with enhanced DC and RF characteristics for prospect low power applications. Microelectron Eng. 2019;217:111103. https://doi.org/10.1016/j.mee.2019.111103.

Tripathy MR, Singh AK, Samad A, Baral K, Singh PK, Jit S. Performance comparison of Ge/Si hetero-junction vertical tunnel FET with and without gate-drain underlapped structure with application to digital inverter. 2020. pp. 1–4. https://doi.org/10.1109/edtm47692.2020.9117840.

Cutaia D, Moselund KE, Schmid H, Borg M, Olziersky A, Riel H. Complementary III-V heterojunction lateral NW Tunnel FET technology on Si. Dig Tech Pap Symp VLSI Technol. 2016;2016-Septe(619509):4–5. https://doi.org/10.1109/VLSIT.2016.7573444.

Singh S, Raj B. Modeling and simulation analysis of SiGe heterojunction Double gate vertical t-shaped tunnel FET. Superlattices Microstruct. 2020;142:106496. https://doi.org/10.1016/j.spmi.2020.106496.

Asthana PK, Goswami Y, Basak S, Rahi SB, Ghosh B. Improved performance of a junctionless tunnel field effect transistor with a Si and SiGe heterostructure for ultra low power applications. RSC Adv. 2015;5(60):48779–85. https://doi.org/10.1039/c5ra03301b.

Bayani AH, Dideban D, Akbarzadeh M, Moezi N. Benchmarking performance of a gate-all-around germanium nanotube field effect transistor (GAA-GeNTFET) against GAA-CNTFET. ECS J Solid State Sci Technol. 2017;6(4):M24–8. https://doi.org/10.1149/2.0211704jss.

Tripathy MR, Kumar Singh A, Chander S, Singh PK, Baral K, Jit S. Device-level performance comparison of some pocket engineered III-V/Si hetero-junction vertical tunnel field effect transistor. In: ICDCS 2020 - 2020 5th international conference on devices, circuits and systems, 2020. pp. 180–183. https://doi.org/10.1109/ICDCS48716.2020.243576.

Silvaco ATLAS. Device simulation software, Santa Clara, CA, USA, 2015. [Online]. Available: https://silvaco.com/.

Cutaia D et al. Fabrication and analysis of vertical p-type InAs-Si nanowire tunnel FETs. In: EUROSOI-ULIS 2015: 2015 joint international EUROSOI workshop and international conference on ultimate integration on silicon. 2015. pp. 61–64. https://doi.org/10.1109/ULIS.2015.7063773.

Städele M, Sacconi F, Di Carlo A, Lugli P. Enhancement of the effective tunnel mass in ultrathin silicon dioxide layers. J Appl Phys. 2003;93(5):2681–90. https://doi.org/10.1063/1.1541107.

Soniya SS, Raj B, Singh S, Wadhwa G. An analytical modeling for dual source vertical tunnel field effect transistor. Int J Recent Technol Eng. 2019;8(3):603–8. https://doi.org/10.35940/ijrte.B2253.098319.

Tomioka K, Gamo H, Motohisa J. (Invited) vertical tunnel FET technologies using III-V/Si heterojunction. ECS Trans. 2019;92(4):71–8. https://doi.org/10.1149/09204.0071ecst.

Hanna AN, Fahad HM, Hussain MM. InAs/Si hetero-junction nanotube tunnel transistors. Sci Rep. 2015;5(1):9843. https://doi.org/10.1038/srep09843.

Lee H, Cho Y, Jeon S, Shin M. First-Principles-based quantum transport simulations of interfacial point defect effects on InAs nanowire tunnel FETs. IEEE Trans Electron Devices. 2021;68(11):5901–7. https://doi.org/10.1109/TED.2021.3112395.

Choi Y, Hong Y, Ko E, Shin C. Optimization of double metal-gate InAs/Si heterojunction nanowire TFET. Semicond Sci Technol. 2020;35(7):075024. https://doi.org/10.1088/1361-6641/ab8b1f.

Kumar N, Raman A. Prospective sensing applications of novel heteromaterial based dopingless nanowire-TFET at low operating voltage. IEEE Trans Nanotechnol. 2020;19:527–34. https://doi.org/10.1109/TNANO.2020.3005026.

Acknowledgements

Not applicable.

Funding

No fund.

Author information

Authors and Affiliations

Contributions

DM: Conceptualization, Writing—original draft, Software. SM: review & editing. Both authors read and approved the final manuscript.

Authors’ Information

Dariush Madadi received the MSc degree in nanoelectronics engineering from Semnan University, Semnan, Iran, in 2020. Madadi's research interests include simulation of nanoscale transistors, including MOSFETs, TFETs, and solar-cell devices.

Saeed Mohammadi received the Ph.D. degree in nanoelectronics engineering from the University of Tehran, Tehran, Iran, in 2011. Since 2012, he has been an Assistant Professor with the Department of Electrical and Computer Engineering, Semnan University, Semnan, Iran. His research interests include the modeling and simulation of nanoscale transistors, including MOSFETs, TFETs, Graphene and other novel 2D material-based devices.

Corresponding author

Ethics declarations

Ethics approval and consent to participate

Not applicable.

Consent for publication

Not applicable.

Research involving human participants and/or animals

Not applicable.

Competing interests

The authors declare that they have no competing interests.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

The original online version of this article was revised to correct citations [33] and [34], and their respective references in the reference list.

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Madadi, D., Mohammadi, S. Switching performance assessment of gate-all-around InAs–Si vertical TFET with triple metal gate, a simulation study. Discover Nano 18, 37 (2023). https://doi.org/10.1186/s11671-023-03816-6

Received:

Accepted:

Published:

DOI: https://doi.org/10.1186/s11671-023-03816-6