Abstract

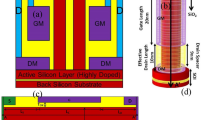

In this paper, the proposed architecture of electrostatic doped based nanotube tunnel field-effect transistor (NT-TFET) has been discussed. The proposed architecture of NT-TFET structure showed improved performance as compared to nanowire TFET (NW-TFET) with the same physical parameters. To analyze the performance of electrostatic doped based NT-TFET, different parameters like device parameter, analog parameter and linearity parameter have been discussed. Electron/hole concentration, electric field, electric potential, energy band diagram and non-local band-to-band tunneling rate (BTBT) have been analyzed as several device parameters. The tunneling rate and tunneling area are greater in NT-TFET as compare to NW-TFET. Analog parameters include drain current, ON-current (ION), OFF-current (IOFF), ION/IOFF, intrinsic gain, output conductance, sub-threshold slope, and threshold voltage have been analyzed. The Drain current (IDS) of value 3*10−5 A/μm, OFF-current is of the order of ~ 10−19 and higher ION/IOFF current ratio of 2*1012 are obtained. The proposed architecture of electrostatic doped based nanotube TFET (NT-TFET) has improved the drain current, steep sub-threshold, OFF-current, and ION/IOFF current ratio.

Similar content being viewed by others

References

Saurabh S, Kumar MJ (2016) Fundamentals of Tunnel Field-Effect Transistors. CRC Press, Boca Raton. https://doi.org/10.1201/9781315367354

Wang P-F, Hilsenbeck K, Nirschl T, Oswald M, Stepper C, Weis M, Schmitt-Landsiedel D, Hansch W (2004) Complementary tunneling transistor for low power application. Solid State Electron 48(12):2281–2286. https://doi.org/10.1016/j.sse.2004.04.006

Schaller RR (1997) Moore’s law: past, present and future. IEEE Spectr. 34(6):52–59. https://doi.org/10.1109/6.591665

Yan R-H, Ourmazd A, Lee KF (1992) Scaling the Si MOSFET: from bulk to SOI to bulk. IEEE Trans. Electron Devices 39(7):1704–1710. https://doi.org/10.1109/16.141237

Choi WY, Park B-G, Lee JD, Liu T-JK (2007) Tunneling field-effect transistors (TFETs) with subthreshold swing (SS) less than 60 mV/dec. IEEE Electron Device Lett. 28(8):743–745. https://doi.org/10.1109/LED.2007.901273

Assaderaghi F, Parke S, Sinitsky D, Bokor J, Ko PK, Hu C (1994) A dynamic threshold voltage MOSFET (DTMOS) for very low voltage operation. IEEE Electron Device Lett. 15(12):510–512. https://doi.org/10.1109/55.338420

Murphy EL, Good Jr RH (1956) Thermionic emission, field emission, and the transition region. Phys. Rev. 102(6):1464. https://doi.org/10.1103/PhysRev.102.1464

T. Krishnamohan, D. Kim, S. Raghunathan, and K. Saraswat (2008) Double-gate strained-Ge heterostructure tunneling FET (TFET) with record high drive currents and 60 mV/dec subthreshold slope. In: Proc. IEEE Int. Electron Devices Meeting, pp. 1–3. https://doi.org/10.1109/IEDM.2008.4796839,

Wang P-F, Hilsenbeck K, Nirschl T, Oswald M, Stepper C, Weis M, Schmitt-Landsiedel D, Hansch W (2004) Complementary tunneling transistor for low power application. Solid State Electron 48(12):2281–2286. https://doi.org/10.1016/j.sse.2004.04.006

Choi WY, Park B-G, Lee JD, Liu T-JK (2007) Tunneling field-effect transistors (TFETs) with subthreshold swing (SS) less than 60 mV/dec. IEEE Electron Device Lett. 28(8):743–745. https://doi.org/10.1109/LED.2007.901273

Kuhn KJ (2012) Considerations for ultimate CMOS scaling. IEEE Trans. Electron Devices 59(7):1813–1828

Mamidala MK, Vishnoi R, Pandey P (2016) Tunnel Field-Effect Transistors (TFET): Modelling and Simulation. Wiley, West Sussex

Hueting RJE, Rajasekharan B, Salm C, Schmitz J (2008) The charge plasma P-N diode. IEEE Electron Device Lett. 29(12):1367–1368. https://doi.org/10.1109/LED.2008.2006864

Shekhar D, Raman A (2020) Design and analysis of dual-gate misalignment on the performance of dopingless tunnel field effect transistor. Appl. Phys. A Mater. Sci. Process. 126:441. https://doi.org/10.1007/s00339-020-03615-1

Sehwag V, Maji S, Sharad, M (2016) Variation Aware Performance Analysis of TFETs for Low-Voltage Computing. 2016 IEEE International Symposium on Nanoelectronic and Information Systems (iNIS). https://doi.org/10.1109/iNIS.2016.032

S. Sahoo, S. Dash and G. P. Mishra. Work-function modulated hetero gate charge plasma TFET to enhance the device performance. 2019 Devices for Integrated Circuit (DevIC), pp. 461–464. https://doi.org/10.1109/DEVIC.2019.8783943, Kalyani, (2019)

Kumar N, Raman A (2019) Design and investigation of charge-plasma-based work function engineered dual-metal-heterogeneous gate Si-Si0.55Ge0.45 GAA-cylindrical NWTFET for ambipolar analysis. IEEE Trans. Electron Devices 66(3):1468–1474. https://doi.org/10.1109/TED.2019.2893224

Shreya S, Kumar N, Anand S et al (2020) Performance analysis of a charge plasma junctionless nanotube tunnel FET including the negative capacitance effect. J. Elec. Mater. 49:2349–2357. https://doi.org/10.1007/s11664-020-07969-3

Agarwal H, Kushwaha P, Lin YK, Kao MY, Liao YH, Dasgupta A, Salahuddin S, Hu C (2019) Proposal for capacitance matching in negative capacitance field-effect transistors. IEEE Electron Device Lett. 40(3):463–466. https://doi.org/10.1109/LED.2019.2891540

Gupta AK, Raman A, Kumar N (2020) Charge-plasma-based negative capacitance ring-FET: design, investigation and reliability analysis. J. Elec. Mater. https://doi.org/10.1007/s11664-020-08205-8

Gupta AK, Raman A, Kumar N (2019) Design and investigation of a novel charge plasma-based core-shell ring-TFET: analog and linearity analysis. IEEE Trans. Electron Devices 66(8):3506–3512. https://doi.org/10.1109/TED.2019.2924809

Kumar S, Raj B (2016) Analysis of IO N and ambipolar current for dualmaterial gate-drain overlapped DG-TFET. J. Nanoelectron. Optoelectron. 11(3):323–333. https://doi.org/10.1166/jno.2016.1902

A. K. Gupta, A. Raman and N. Kumar. Cylindrical nanowire-TFET with core-shell channel architecture: design and investigation. Silicon. 1–8 (2019). https://doi.org/10.1007/s12633-019-00331-1

Chen ZX, Yu HY, Singh N, Shen NS, Sayanthan RD, Lo GQ, Kwong DL (2009) Demonstration of tunneling FETs based on highly scalable vertical silicon nanowires. IEEE Electron Device Lett. 30(7):754–756. https://doi.org/10.1109/LED.2009.2021079

Sahay S, Kumar MJ (2016) A novel gate-stack-engineered nanowire FET for scaling to the sub-10-nm regime. IEEE Trans. Electron Devices 63(12):5055–5059. https://doi.org/10.1109/TED.2016.2617383

KUMAR N, Raman A Novel design approach of extended gate-on-source based charge-plasma vertical-nanowire TFET: proposal and extensive analysis. IEEE Trans. Nanotechnol. https://doi.org/10.1109/TNANO.2020.2993565

Sahay S, Kumar MJ (2017) Nanotube junctionless FET: proposal, design, and investigation. IEEE Trans. Electron Devices 64(4):1851–1856. https://doi.org/10.1109/TED.2017.2672203

Kumar N, Mushtaq U, Amin SI, Anand S (2019) Design and performance analysis of dual-gate all around core-shell nanotube TFET. Superlattice. Microst. 125:356–364. https://doi.org/10.1016/j.spmi.2018.09.012

Sahay S, Kumar MJ (2017) Comprehensive analysis of gate-induced drain leakage in emerging FET architectures: nanotube FETs versus nanowire FETs. IEEE Access 5:18918–18926. https://doi.org/10.1109/ACCESS.2017.2751518

Musalgaonkar G, Sahay S, Saxena RS, Kumar MJ (2019) A line tunneling field-effect transistor based on misaligned core–shell gate architecture in emerging nanotube FETs. IEEE Trans. Electron Devices 66(6):2809–2816. https://doi.org/10.1109/TED.2019.2910156

Lan Wei, S. Oh and H. P. Wong. Performance benchmarks for Si, III–V, TFET, and carbon nanotube FET – re-thinking the technology assessment methodology for complementary logic applications. 2010 International Electron Devices Meeting, pp. 16.2.1–16.2.4. San Francisco, (2010). https://doi.org/10.1109/IEDM.2010.5703373

Apoorva N, Kumar S, Amin I, Anand S (2020) Design and performance optimization of novel core–shell dopingless GAA-nanotube TFET with Si0.5Ge0.5-based source. IEEE Trans. Electron Devices 67(3):789–795. https://doi.org/10.1109/TED.2020.2965244

Tsividis Y, Mc Andrew C (2011) Operation and Modeling of the MOS Transistor. Oxford University Press, Oxford

Yadav S, Madhukar R, Sharma D, Aslam M, Soni D, Sharma N (2018) A new structure of electrically doped TFET for improving electronic characteristics. Appl. Phys. 124(7):517. https://doi.org/10.1007/s00339-018-1930-9

Gundapaneni S, Ganguly S, Kottantharayil A (2011) Enhanced electrostatic integrity of short channel junctionless transistor with high-k spacers. IEEE Electron Device Lett. 32(10):1325–1327. https://doi.org/10.1109/LED.2011.2162309

Sahay S, Kumar MJ (2015) Controlling the drain side tunneling width to reduce ambipolar current in tunnel FETs using heterodielectric BOX. IEEE Trans. Electron Devices 62(11):3882–3886. https://doi.org/10.1109/TED.2015.2478955

Na MH, Nowak EJ, Haensch W, Cai J (2002) The effective drive current in CMOS inverters. IEDM Tech. Dig.:121–124. https://doi.org/10.1109/IEDM.2002.1175793

ATLAS (2011) User’s manual, version 5. SILVACO, Santa Clara

Patel J, Sharma D, Yadav S, Lemtur A, Suman P (2019) Performance improvement of nano wire TFET by hetero-dielectric and hetero-material: at device and circuit level. Microelectron. J. 85:72–82. https://doi.org/10.1016/j.mejo.2019.02.004

Dewey G et al (2011) Fabrication, characterization, and physics of III–V heterojunction tunneling Field Effect Transistors (H-TFET) for steep sub-threshold swing. EDM Tech. Dig.:33.6.1–33.6.4. https://doi.org/10.1109/IEDM.2011.6131666

Tomioka K, Yoshimura M, Fukui T (2013) Sub 60 mV/decade switch using an InAs nanowire–Si heterojunction and turn-on voltage shift with a pulsed doping technique. Nano. Lett. 13(12):5822–5826. https://doi.org/10.1021/nl402447h

Gandhi R, Chen Z, Singh N, Banerjee K, Lee S (2011) Vertical Si-nanowire n-type tunneling FETs with low subthreshold swing (≤50 mV/decade) at room temperature. IEEE Electron Device Lett. 32(4):437–439. https://doi.org/10.1109/led.2011.2106757

Hanna AN, Hussain MM (2015) Si/Ge hetero-structure nanotube tunnel field effect transistor. J. Appl. Phys. 117(1):014310. https://doi.org/10.1063/1.4905423

Musalgaonkar G, Sahay S, Saxena RS, Kumar MJ (2019) Nanotube tunneling FET with a core source for ultrasteep subthreshold swing: a simulation study. IEEE Trans. Electron Devices:1–8. https://doi.org/10.1109/ted.2019.2933756

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher’s Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Gupta, A.K., Raman, A. Electrostatic-Doped Nanotube TFET: Proposal, Design, and Investigation with Linearity Analysis. Silicon 13, 2401–2413 (2021). https://doi.org/10.1007/s12633-020-00584-1

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s12633-020-00584-1