Abstract

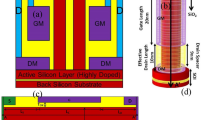

This paper examines, an electrostatically configured Nano-Tube Tunnel Field-Effect Transistor (ED-NTTFET). During the fabrication process, different charges such as fixed charge, oxide trapped charge, and interface trapped charge have been produced at the gate oxide interface. So the effect of positive and negative interface trapped charge (+ITC & -ITC) has been proposed for the first time for electrostatic doped-based Nano-Tube TFET (ED-NTTFET). There are two types of techniques, charge plasma (EP) based technique and electrostatic doped (ED) technique is used to produce the induced charge in the intrinsic channel region. In the charged plasma (CP) technique, the metal work-function is used to produce the induced charge while in the electrostatic doped (ED) technique electrostatic voltage is applied across the source and drain side to produce the induced charge in the intrinsic channel region. Analysis of the various device parameters such as hole/electron concentration, energy diagram, electric field, tunneling rate, driving current, OFF current, ON current, ION/IOFF, threshold voltage, and average sub-threshold slope in the presence of interface trapped charge (ITC). Due to positive interface trapped charge electric field and band to band tunneling rates are improved. So the drain current of the device also improved from the 2.94*10−5 A/um2 to 5.35*10−5A/um2. Linearity parameters such as second & third order trans-conductance (gm2 & gm3), second & third order voltage intercept point (VIP2 & VIP3), second & third order harmonics distortions (HD2 & HD3) and intermodulation distortions (IMD) have been discussed. The negative interface trapped charge (-ITC) degrades the linearity parameter of the device and the positive interface trapped charge (+ITC) improves the linearity parameter of the device. The proposed electrostatic doped nano-tube TFET (ED-NTTFET) produced higher cut-off frequency at lowers operating gate voltage.

Similar content being viewed by others

References

Yan R-H, Ourmazd A, Lee KF (1992) Scaling the Si MOSFET: from bulk to SOI to bulk. IEEE Trans Electron Devices 39(7):1704–1710. https://doi.org/10.1109/16.141237

Schaller RR (1997) Moore’s law: past, present and future. IEEE Spectr 34(6):52–59. https://doi.org/10.1109/6.591665

Ieong M, Doris B, Kedzierski J, Rim K, Yang M (2004) Silicon device scaling to the sub-10-nm regime. Science 306(5704):2057–2060. https://doi.org/10.1126/science.1100731

Mikolajick T, Häublein V, Ryssel H (1997) The effect of random dopant fluctuations on the minimum channel length of short-channel MOS transistors. Appl Phys A Mater Sci Process 64(6):555–560. https://doi.org/10.1007/s003390050516

Shin C, Sun X, Liu TK (2009) Study of random-dopant-fluctuation (RDF) effects for the Trigate bulk MOSFET. IEEE Trans Electron Devices 56(7):1538–1542. https://doi.org/10.1109/TED.2009.2020321

Chatzikyriakou E, Redman-White W, Groot CHD (2017) Total ionizing dose, random dopant fluctuations, and its combined effect in the 45nm PDSOI node. Microelectron Reliab 68:21–29. https://doi.org/10.1016/j.microrel.2016.11.007

Yoon J, Baek R (2018) Study on random dopant fluctuation in Core–Shell tunneling field-effect transistors. IEEE Trans Electron Devices 65(8):3131–3135. https://doi.org/10.1109/TED.2018.2846782

Damrongplasit N, Kim SH, Liu TK (2013) Study of random dopant fluctuation induced variability in the raised-Ge-source TFET. IEEE Electron Device Lett 34(2):184–186. https://doi.org/10.1109/LED.2012.2235404

Saurabh S, Kumar MJ (2016) Fundamentals of tunnel field-effect transistors. CRC Press, Boca Raton. https://doi.org/10.1201/9781315367354

Mamidala MK, Vishnoi R, Pandey P (2016) Tunnel field-effect transistors (TFET): Modelling and simulation. Wiley, West Sussex

Gupta AK, Raman A, Kumar N (2019) Cylindrical Nanowire- TFET with Core-Shell Channel Architecture: Design and Investigation. Silicon: 1–8. https://doi.org/10.1007/s12633-019-00331-1

Sahay S, Kumar MJ (2017) Nanotube Junctionless FET: proposal, design, and investigation. IEEE Trans Electron Devices 64(4):1851–1856. https://doi.org/10.1109/TED.2017.2672203

Chen ZX, Yu HY, Singh N, Shen NS, Sayanthan RD, Lo GQ, Kwong DL (2009) Demonstration of tunneling FETs based on highly scalable vertical silicon nanowires. IEEE Electron Device Lett 30(7):754–756. https://doi.org/10.1109/LED.2009.2021079

Krishnamohan T, Kim D, Raghunathan S, Saraswat K (2008) Double-gate strained-Ge heterostructure tunneling FET (TFET) with record high drive currents and 60 mV/dec subthreshold slope. Proc. IEEE Int. Electron Devices Meeting: 1–3, https://doi.org/10.1109/IEDM.2008.4796839

Kumar N, Raman A (2019) Design and investigation of charge-plasma-based work function engineered dual-metal-heterogeneous gate Si-Si0.55Ge0.45 GAA-cylindrical NWTFET for Ambipolar analysis. IEEE Trans Electron Devices 66(3):1468–1474. https://doi.org/10.1109/TED.2019.2893224

Choi WY, Lee W (2010) Hetero-gate-dielectric tunneling fieldeffect transistors. IEEE Trans Electron Devices 57(9):2317–2319. https://doi.org/10.1109/TED.2010.2052167

Kondekar PN, Nigam K, Pandey S, Sharma D (2016) Design and analysis of polarity controlled electrically doped tunnel FET with bandgap engineering for analog/RF applications. IEEE Trans Electron Devices 64(2):412–418. https://doi.org/10.1109/TED.2016.2637638

Gupta AK, Raman A, Kumar N (2019) Design and investigation of a novel charge plasma-based Core-Shell ring-TFET: analog and linearity analysis. IEEE Trans Electron Devices 66(8):3506–3512. https://doi.org/10.1109/TED.2019.2924809

Kumar N, Mushtaq U, Amin SI, Anand S (2019) Design and performance analysis of dual-gate all around core-shell nanotube TFET. Superlattices Microstruct 125:356–364. https://doi.org/10.1016/j.spmi.2018.09.012

Mallik K, Falster RJ, Wilshaw PR (2003) Semi-insulating’ silicon using deep level impurity doping: problems and potential. Semiconductor Sci Technol 18(6):517. https://doi.org/10.1088/0268-1242/18/6/321

Hasan S, Wang J, Lundstrom M (2004) Device design and manufacturing issues for 10 nm-scale MOSFETs: a computational study. Solid State Electron 48(6):867–875. https://doi.org/10.1016/j.sse.2003.12.022

Zubel I (1998) Silicon anisotropic etching in alkaline solutions II on the influence of anisotropy on the smoothness of etched surfaces. Sensors Actuators A Phys 70(3):260–268. https://doi.org/10.1016/S0924-4247(98)00142-3

Gilmer GH, De La Rubia TD, Stock DM, Jaraiz M (1995) Diffusion and interactions of point defects in silicon: molecular dynamics simulations. Nucl Instrum Methods Phys Res, Sect B 102(1–4):247–255. https://doi.org/10.1016/0168-583X(95)80150-K

Madan J, Chaujar R (2017) Numerical simulation of N+ source pocket PIN-GAA-tunnel FET: impact of interface trap charges and temperature. IEEE Trans Electron Devices 64(4):1482–1488. https://doi.org/10.1109/TED.2017.2670603

Tong HD, Chen S, van der Wiel WG, Carlen ET, van den Berg A (2009) Novel top-down wafer-scale fabrication of single crystal silicon nanowires. Nano Lett 9(3):1015–1022. https://doi.org/10.1021/nl803181x

Gupta AK, Raman A, Kumar N (2020) Charge-plasma-based negative capacitance ring-FET: design, investigation and reliability analysis. J Elec Mater 49:4852–4863. https://doi.org/10.1007/s11664-020-08205-8

Kumar N, Raman A (2019) Performance assessment of the charge-plasma-based cylindrical GAA vertical nanowire TFET with impact of Interface trap charges. IEEE Trans Electron Devices 66(10):4453–4460. https://doi.org/10.1109/TED.2019.2935342

ATLAS (2011) User’s manual, version 5. SILVACO, Santa Clara

Narang R, Saxena M, Gupta RS, Gupta M (2011) Linearity and analog performance analysis of double gate tunnel FET: effect of temperature and gate stack. Int J VLSI Design Commun Syst 2(3):185. https://doi.org/10.1007/978-3-642-22543-7_47

Chandan BV, Dasari S, Yadav S, Sharma D (2018) Approach to suppress ambipolarity and improve RF and linearity performances on ED-tunnel FET. IET Micro Nano Letters 13(5):684–689. https://doi.org/10.1049/mnl.2017.0814

Upasana NR, Saxena M, Gupta M (2016) Linearity and analog performance realization of energy-efficient TFET-based architectures: an optimization for RFIC design. IETE Tech Rev 33(1):23–28. https://doi.org/10.1080/02564602.2015.1043153

Verma M, Tirkey S, Yadav S, Sharma D, Yadav DS (2017) Performance assessment of a novel vertical dielectrically modulated TFET-based biosensor. IEEE Trans Electron Devices 64(9):3841–3848. https://doi.org/10.1109/TED.2017.2732820

Soni D, Sharma D, Yadav S, Aslam M, Sharma N (2018) Performance improvement of doped TFET by using plasma formation concept. Superlattice Microst 113:97–109. https://doi.org/10.1016/j.spmi.2017.10.012

Chauhan SS (2018) A new design approach to improve DC, analog/RF and linearity metrics of vertical TFET for RFIC design. Superlattice Microst 122:286–295. https://doi.org/10.1016/j.spmi.2018.07.036

Chandan BV, Nigam K, Sharma D, Pandey S (2018) Impact of interface trap charges on dopingless tunnel FET for enhancement of linearity characteristics. Appl Phys A 124(7):503. https://doi.org/10.1007/s00339-018-1923-8

Vanlalawmpuia K, Bhowmick B 2019 Linearity performance analysis due to lateral straggle variation in hetero-stacked TFET. Silicon: 1-7. https://doi.org/10.1007/s12633-019-00189-3

Narwal S, Chauhan SS (2019) Investigation of RF and linearity performance of electrode work-function engineered HDB vertical TFET. Micro Nano Lett 14(1):17–21. https://doi.org/10.1049/mnl.2018.5307

Narang R, Saxena M, Gupta M (2019) Exploring the applicability of well optimized dielectric pocket tunnel transistor for future low power applications. Superlattice Microst 126:8–16. https://doi.org/10.1016/j.spmi.2018.12.005

Kumar S, Singh KS, Nigam K, Tikkiwal VA, Chandan BV (2019) Dual-material dual-oxide double-gate TFET for improvement in DC characteristics, analog/RF and linearity performance. Appl Phys A 125(5):353. https://doi.org/10.1007/s00339-019-2650-5

Paras N, Chauhan SS 2019 Insights into the DC, RF/analog and linearity performance of vertical tunneling based TFET for low-power applications. Microelectronic Eng: 111043. https://doi.org/10.1016/j.mee.2019.111043

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher’s Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Gupta, A.K., Raman, A. & Kumar, N. Performance Tuning and Reliability Analysis of the Electrostatically Configured Nanotube Tunnel FET with Impact of Interface Trap Charges. Silicon 13, 4553–4564 (2021). https://doi.org/10.1007/s12633-020-00777-8

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s12633-020-00777-8