Abstract

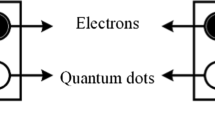

Quantum dot gate FETs (QDGFET) produce one intermediate state between two stable on and off states due to the change in the threshold voltage. A circuit model based on Berkeley Short-channel IGFET Model (BSIM) that accounts for this intermediate state is developed. Different ternary logics such as ternary logic inverter, MAX-MIN functions, multiplier, comparator, etc. can be implemented using QDGFETs. In this work the designs of ternary logic AND and OR gate based on QDGFET is introduced. Increased number of states in three state QDGFETs will increase the number of bit handling capability of this device and will help to handle more bits at a time with less circuit elements.

Similar content being viewed by others

References

Ackermann R (1967) An introduction to many-valued logics. Routledge and Kegan Paul, London

Rescher N (1969) Many-valued logic. McGraw Hill, New York

Lin HC (1994) In: Proceedings of 24th IEEE international symposium multiple–valued logic. pp 188–195

Capasso F, Kiehl RA (1985) J Appl Phys 58:1366–1368

Tsai JH (2004) Solid State Electron 48:81–85

Imtiaz SMS, El-Ghazaly S (1998) IEEE Trans Microw Theory Tech 46:923–931

Raychowdhury A, Roy K (2004) In: Proceedings of international symposium on multiple-valued logic. pp 14–19

Balla PC, Antoniou A (1984) IEEE J Solid-State Circ 19:739–749

Karmakar S, Suarez E et al (2011) J Electron Mater 40:1749–1756

Karmakar S, Suarez E et al (2012) J Electron Mater 41:2663–2670

Karmakar S, Chandy JA et al (2012) J Electron Mater 41:2184–2192

Papadimitrakopoulos F, PhelyBobin T et al (1999) Chem Mater 11:522–525

Phely-Bobin T, Chattopadhyay D et al (2002) Chem Mater 14:1030–1036

Karmakar S, Gogna M et al (2012) Electron Lett 48:1556–1557

Karmakar S, Chandy JA et al (2013) IEEE Transactions on Very Large Scale Integration Systems (TVLSI) 21:793–806

Chandy JA, Jain F (2008) In: Proceedings of IEEE international symposium on multiple-valued logic. pp 186–190

Kleene SC (1938) J Symb Log 3:150–155

Kim YB (2011) Trans Electr Electron Mater 12:75–188

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Karmakar, S. Ternary Logic Gates Using Quantum Dot Gate FETs (QDGFETs). Silicon 6, 169–178 (2014). https://doi.org/10.1007/s12633-013-9175-x

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s12633-013-9175-x