Abstract

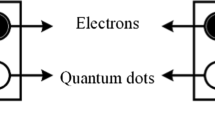

Quantum dot gate FETs (QDGFET) produce one intermediate state between two stable on and off states due to the change in the threshold voltage. A circuit model based on Berkeley Short-channel IGFET Model that accounts for this intermediate state is developed. Different ternary logic inverters such as standard ternary inverter, positive ternary inerter, and negative ternary inverter can be designed using QDGFETs. In this work the application of different ternary logic inverter in image processing are discussed. The comparison of binary logic inverter and ternary logic inverter is also discussed. Comparison with other technology is also presented Increased number of states in three state QDGFETs will increase the image processing capacity of QDGFET based circuits.

Similar content being viewed by others

References

Ackermann, R. (1967). An introduction to many-valued logics. London: Routledge and Kegan Paul, London.

Rescher, N. (1969). Many-valued logic. New York: McGraw Hill.

Lin, H. C. (1994). Resonant tunneling diodes for multi-valued digital applications. Proceedings of 24th IEEE International Symposium on Multiple-Valued Logic (pp. 188–195).

Capasso, F., & Kiehl, R. A. (1985). Resonant tunneling transistor with quantum well base and high-energy injection: A new negative differential resistance device. Journal of Applied Physics, 58, 1366–1368.

Tsai, J. H. (2004). High-performance AlInAs/GaInAs δ-doped HEMT with negative differential resistance switch for logic application. Solid State Electronics, 48, 81–85.

Imtiaz, S. M. S., & El-Ghazaly, S. M. (1998). Performance of MODFET and MESFET: A comparative study including equivalent circuits using combined electromagnetic and solid-state simulator. IEEE Transaction on Microwave Theory and Techniques, 46, 923–931.

Raychowdhury, A., Roy, K. (2004). A novel multiple-valued logic design using ballistic carbon nanotube FETs. Proceedings of International Symposium on Multiple-Valued Logic

Balla, P. C., & Antoniou, A. (1984). Low power dissipation MOS ternary logic family. IEEE Journal of Solid State Circuits, 19, 739–749.

Karmakar, S., Suarez, E., Gogna, M., & Jain, F. (2012). ZnS-ZnMgS-ZnS lattice-matched gate insulator as an alternative for silicon dioxide on silicon in quantum dot gate FETs (QDGFETs). Journal of Electronic Materials, 41, 2663–2670.

Karmakar, S., Gogna, M., Suarez, E., & Jain, F. (2015). Three-state quantum dot gate field effect transistor in silicon-on-insulator. IET Circuits Devices and Systems, 9(2), 111–118.

Karmakar, S., Chandy, J. A., Gogna, M., & Jain, F. C. (2012). Fabrication and circuit modeling of NMOS inverter based on quantum dot gate field-effect transistors. Journal of Electronic Materials, 41, 2184–2192.

Karmakar, S., & Jain, F. (2015). Circuit model of different quantum dot based field effect transistors. Silicon, 7, 15–26.

Karmakar, S., & Jain, F. (2014). Ternary universal logic gates using quantum dot gate field effect transistors. Indian Journal of Physics, 88, 1275–1283.

Papadimitrakopoulos, F., Phely-Bobin, T., & Wisniecki, P. (1999). Self-assembled nanosilicon/siloxane composite films. Chemistry of Materials, 11, 522–525.

Phely-Bobin, T., Chattopadhyay, D., & Papadimitrakopoulos, F. (2002). Characterization of mechanically attrited Si/SiOx nanoparticles and their self-assembled composite films. Chemistry of Materials, 14, 1030–1036.

Karmakar, S., Gogna, M., & Jain, F. C. (2012). Improved device structure of quantum dot gate FET to obtain more stable intermediate state. Electronics Letters, 48, 1556–1557.

Karmakar, S. (2014). Ternary logic gates using quantum dot gate FETs (QDFETs). Silicon, 6, 169–178.

Karmakar, S., Chandy, J. A., & Jain, F. C. (2012). Design of ternary logic combinational circuits based on quantum dot gate FETs. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 21, 793–806.

Karmakar, S., Suresh, A. P, Chandy, J. A., & Jain, F. C. (2009). Design of ADCs and DACs using 3-state quantum dot gate FETs. International Semiconductor Device Research Symposium, Dec. 9–11, 2009, College Park, MD.

Karmakar, S., Chandy, J. A., & Jain, F. C. (2011). Application of 25 nm quantum dot gate FETs to the design of ADC and DAC circuits. International Journal of High Speed Electronics and Systems, 20, 653–668.

Karmakar, S., Chandy, J. A., & Jain, F. C. (2014). Implementation of six bit ADC and DAC using quantum dot gate non-volatile memory. Journal of Signal Processing Systems, 75, 209–216.

Kim, Y. B. (2011). Integrated circuit design based on carbon nanotube field effect transistor. Transactions on Electrical and Electronic Materials, 12, 175–188.

Acknowledgments

This work is an extension of author’s research work in his Ph.D. The author greatly acknowledges the discussions with Dr. John A. Chandy, and Dr. Faquir Jain, Department of Electrical Engineering, University of Connecticut.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Karmakar, S. Application of quantum dot gate FETs (QDGFETs) in ternary logic image inversion. Analog Integr Circ Sig Process 87, 65–72 (2016). https://doi.org/10.1007/s10470-015-0673-1

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-015-0673-1