Abstract

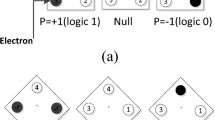

Quantum-dot cellular automata (QCA), a new computing paradigm at nanoscale, may be a prospective alternative to conventional CMOS-based integrated circuits. Modular design methodology in QCA domain has not been widely investigated. In this paper, an efficient module with fault tolerance is proposed, which can be employed to fabricate three-input and five-input majority gates that are the fundamental primitives for designing circuits in QCA. With cells omission in the versatile module, various logic gates will be achieved, such as Nand-Nor-Inverter (NNI) gate and And-Or-Inverter (AOI) gate. Moreover, in order to seek out an efficient full adder, five various QCA full adders are designed and exhaustively compared in terms of area, complexity, latency, reliability and power dissipation and also compared with existing fault-tolerant full adders. Two simulation tools, QCADesigner and QCAPro, are utilized in the waveform simulations for verifying the correctness of proposed circuits and power consumption, respectively. The analysis results reveal that full adder V has significant improvements in contrast to its counterparts with above criteria. To test the practicability of full adder V, multi-bit adders will be designed in single-layer and compared with previous adders in terms of area, complexity and QCA cost, which proves the merits of our work.

Similar content being viewed by others

References

Cho, H., Swartzlander, E.E. Jr: Adder designs and analyses for quantum-dot cellular automata. IEEE Trans. Nanotechnol. 6(3), 374–383 (2007). https://doi.org/10.1109/TNANO.2007.894839

Tougaw, P.D., Lent, C.S.: Logical devices implemented using quantum cellular automata. J. Appl. Phys. 75(3), 1818–1825 (1994). https://doi.org/10.1063/1.356375

Lent, C.S., Tougaw, P.D.: A device architecture for computing with quantum dots. Proc. IEEE 85(4), 541–557 (1997). https://doi.org/10.1109/5.573740

Bahar, R., Mundy, J., Chen, J.: A probabilistic-based design methodology for nanoscale computation. In: Proceedings of the 2003 IEEE/ACM International Conference on Computer-aided Design, San Jose, USA, pp 480–486. IEEE Computer Society (2003)

Bhanja, S., Sarkar, S.: Probabilistic modeling of QCA circuits using bayesian networks. IEEE Trans. Nanotechnol. 5(6), 657–669 (2006). https://doi.org/10.1109/TNANO.2006.883474

Srivastava, S., Bhanja, S.: Hierarchical probabilistic macromodeling for QCA circuits. IEEE Trans. Comput. 56(2), 174–190 (2007). https://doi.org/10.1109/TC.2007.30

Krishnaswamy, S., Viamontes, G.F., Markov, I.L., Hayes, J.P.: Probabilistic transfer matrices in symbolic reliability analysis of logic circuits. ACM Trans. Des. Autom. Electron. Syst. 13(1), 1–8 (2008). https://doi.org/10.1145/1297666.1297674

Huang, J., Momenzadeh, M., Schiano, L., Lombardi, F.: Simulation-based design of modular QCA circuits. In: 2005 5th IEEE Conference on Nanotechnology, July 11, 2005 - July 15, 2005, Nagoya, Japan, pp 721–724. Institute of Electrical and Electronics Engineers Computer Society (2005)

Xia, Y., Qiu, K.: Design and application of universal logic gate based on quantum-dot cellular automata. In: Proceedings of the 2008 11th IEEE International Conference on Communication Technology, ICCT 2008, November 10, 2008 - November 12, 2008, Hangzhou, China, pp 335–338. Institute of Electrical and Electronics Engineers Inc (2008)

Xiao, L., Ying, S., Pei, T.: QCA circuit design based on novel optimal ULG.2. In: 2010 2nd International Conference on Industrial Mechatronics and Automation, ICIMA 2010, May 30, 2010 - May 31, 2010, Wuhan, China 2010. ICIMA, pp 380–384. IEEE Computer Society (2010)

Navi, K., Farazkish, R., Sayedsalehi, S., Rahimi Azghadi, M.: A new quantum-dot cellular automata full-adder. Microelectron. J. 41(12), 820–826 (2010). https://doi.org/10.1016/j.mejo.2010.07.003

Walus, K., Dysart, T.J., Jullien, G.A., Budiman, R.A.: QCADEsigner: a rapid design and simulation tool for quantum-dot cellular automata. IEEE Trans. Nanotechnol. 3 (1), 26–31 (2004). https://doi.org/10.1109/TNANO.2003.820815

Kim, K., Wu, K., Karri, R.: Quantum-dot cellular automata design guideline. IEICE Trans. Fund. Electron. Commun. Comput. Sci. E89-A(6), 1607–1614 (2006). https://doi.org/10.1093/ietfec/e89-a.6.1607

Vankamamidi, V., Ottavi, M., Lombardi, F.: Two-dimensional schemes for clocking/timing of QCA circuits. IEEE Trans. Comput. Aided Des. Integr. Circuits Syst. 27(1), 34–44 (2008). https://doi.org/10.1109/TCAD.2007.907020

Kumar, D., Mitra, D.: Design of a practical fault-tolerant adder in QCA. Microelectron. J. 53, 90–104 (2016). https://doi.org/10.1016/j.mejo.2016.04.004

Liu, W., Lu, L., Oneill, M., Swartzlander, E.E.: A first step toward cost functions for quantum-dot cellular automata designs. IEEE Trans. Nanotechnol. 13(3), 476–487 (2014). https://doi.org/10.1109/TNANO.2014.2306754

Srivastava, S., Sarkar, S., Bhanja, S.: Estimation of upper bound of power dissipation in QCA circuits. IEEE Trans. Nanotechnol. 8(1), 116–127 (2009). https://doi.org/10.1109/TNANO.2008.2005408

Ibrahim, W., Beiu, V., Sulieman, M.H.: On the reliability of majority gates full adders. IEEE Trans. Nanotechnol. 7(1), 56–67 (2008). https://doi.org/10.1109/TNANO.2007.915203

Das, K., De, D.: A novel approach of And-Or-Inverter (AOI) gate design for QCA. In: 4th International Conference on Computers and Devices for Communication, Codec 2009, December 14, 2009 - December 16, 2009, Kolkata, India 2009. Codec. IEEE Computer Society (2009)

Sen, B., Sikdar, B.K.: A study on defect tolerance of tiles implementing universal gate functions. In: Proceedings of the 2007 International Conference on Design and Technology of Integrated Systems in Nanoscale Era, DTIS 2007, September 2, 2007 - September 5, 2007, Rabat, Morocco, pp 13–18. Inst. of Elec. and Elec. Eng. Computer Society (2007)

Das, K., De, D.: Novel approach to design a testable conservative logic gate for QCA implementation. In: 2010 IEEE 2nd International Advance Computing Conference, IACC 2010, February 19, 2010 - February 20, 2010, Patiala, India, pp 82–87. IEEE Computer Society (2010)

Farazkish, R.: A new quantum-dot cellular automata fault-tolerant five-input majority gate. J. Nanoparticle Res. 16(2), 1–7 (2014). https://doi.org/10.1007/s11051-014-2259-8

Ma, X., Huang, J., Metra, C., Lombardi, F.: Reversible gates and testability of one dimensional arrays of molecular QCA. Journal of Electronic Testing: Theory and Applications (JETTA) 24(1-3), 297–311 (2008). https://doi.org/10.1007/s10836-007-5042-2

Ma, X., Huang, J., Metra, C., Lombardi, F.: Detecting multiple faults in one-dimensional arrays of reversible QCA gates. Journal of Electronic Testing: Theory and Applications (JETTA) 25(1 SPEC. ISS.), 39–54 (2009). https://doi.org/10.1007/s10836-008-5078-y

Farazkish, R., Navi, K.: New efficient five-input majority gate for quantum-dot cellular automata. J. Nanoparticle Res. 14(11), 1–6 (2012). https://doi.org/10.1007/s11051-012-1252-3

Akeela, R., Wagh, M.D.: A five-input majority gate in quantum-dot cellular automata. In: Nanotechnology 2011: Electronics, Devices, Fabrication, MEMS, Fluidics and Computational - 2011 NSTI Nanotechnology Conference and Expo, NSTI-Nanotech 2011, June 13, 2011 - June 16, 2011, Boston, MA, United States 2011. Technical Proceedings of the 2011 NSTI Nanotechnology Conference and Expo, NSTI-Nanotech, pp 13–16. Nano Science and Technology Institute (2011)

Cho, H., Swartzlander, E.E. Jr: Adder and multiplier design in quantum-dot cellular automata. IEEE Trans. Comput. 58(6), 721–727 (2009). https://doi.org/10.1109/TC.2009.21

Kianpour, M., Sabbaghi-Nadooshan, R., Navi, K.: A novel design of 8-bit adder/subtractor by quantum-dot cellular automata. J. Comput. Syst. Sci. 80(7), 1404–1414 (2014). https://doi.org/10.1016/j.jcss.2014.04.012

Roohi, A., Khademolhosseini, H., Sayedsalehi, S., Navi, K.: A symmetric quantum-dot cellular automata design for 5-input majority gate. J. Comput. Electron. 13(3), 701–708 (2014). https://doi.org/10.1007/s10825-014-0589-5

Hanninen, I., Takala, J.: Binary adders on quantum-dot cellular automata. J. Signal Process. Syst. 58(1), 87–103 (2010). https://doi.org/10.1007/s11265-008-0284-5

Roohi, A., DeMara, R.F., Khoshavi, N.: Design and evaluation of an ultra-area-efficient fault-tolerant QCA full adder. Microelectron. J. 46(6), 531–542 (2015). https://doi.org/10.1016/j.mejo.2015.03.023

Gladshtein, M.: Design and simulation of novel adder/subtractors on quantum-dot cellular automata: radical departure from boolean logic circuits. Microelectron. J. 44(6), 545–552 (2013). https://doi.org/10.1016/j.mejo.2013.03.013

Gladshtein, M.: Quantum-dot cellular automata serial decimal adder. IEEE Trans. Nanotechnol. 10(6), 1377–1382 (2011). https://doi.org/10.1109/TNANO.2011.2138714

Zhang, Y., Lv, H., Du, H., Huang, C., Liu, S., Xie, G.: Modular design of QCA carry flow adders and multiplier with reduced wire crossing and number of logic gates. Int. J. Circuit Theory Appl. 44(7), 1351–1366 (2016). https://doi.org/10.1002/cta.2163

Farazkish, R.: A new quantum-dot cellular automata fault-tolerant full-adder. J. Comput. Electron. 14(2), 506–514 (2015). https://doi.org/10.1007/s10825-015-0668-2

Sen, B., Rajoria, A., Sikdar, B.K.: Design of efficient full adder in quantum-dot cellular automata. Sci. World J. 2013, 1–10 (2013). https://doi.org/10.1155/2013/250802

Wang, W., Walus, K., Jullien, G.A.: Quantum-dot cellular automata adders. In: Proceedings of the 2003 3rd IEEE Conference on Nanotechnology, IEEE-NANO 2003, August 12, 2003 - August 14, 2003, San Francisco, CA, United States, pp 461–464. IEEE Computer Society (2003)

Hanninen, I., Takala, J.: Robust adders based on quantum-dot cellular automata. In: 2007 IEEE International Conference on Application-specific Systems, Architectures and Processors (ASAP), Canada, 9-11 July 2007, pp 391–396 (2007)

Zhang, R., Walus, K., Wang, W., Jullien, G.A.: Performance comparison of quantum-dot cellular automata adders. In: Proceedings of the IEEE International Symposium on Circuits and Systems 2005, ISCAS 2005, May 23, 2005 - May 26, 2005, Kobe, Japan, pp 2522–2526. Institute of Electrical and Electronics Engineers Inc (2005)

Pudi, V., Sridharan, K.: Low complexity design of ripple carry and Brent-Kung adders in QCA. IEEE Trans. Nanotechnol. 11(1), 105–119 (2012). https://doi.org/10.1109/TNANO.2011.2158006

Angizi, S., Alkaldy, E., Bagherzadeh, N., Navi, K.: Novel robust single layer wire crossing approach for exclusive OR sum of products logic design with quantum-dot cellular automata. J. Low Power Electron. 10(2), 259–271 (2014). https://doi.org/10.1166/jolpe.2014.1320

Farazkish, R., Khodaparast, F.: Design and characterization of a new fault-tolerant full-adder for quantum-dot cellular automata. Microprocess. Microsyst. 39(6), 426–433 (2015). https://doi.org/10.1016/j.micpro.2015.04.004

Acknowledgments

This work is supported by the National Natural Science Foundation of China (No. 61271122).

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Zhang, Y., Xie, G., Sun, M. et al. An Efficient Module for Full Adders in Quantum-dot Cellular Automata. Int J Theor Phys 57, 3005–3025 (2018). https://doi.org/10.1007/s10773-018-3820-5

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10773-018-3820-5