Abstract

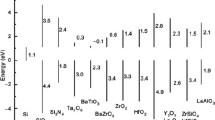

This article discusses recent developments in high dielectric constant gate insulator materials for future ultra-large-scale integration devices below 100 nm. Since conventional gate oxide poses problems as device features are scaled down, it becomes necessary to develop new gate dielectric materials with properties similar to SiO2 and compatible with current complementary metal-oxide semiconductor technology. As the thickness of silicon dioxide approaches less than 1.5 nm, the leakage current becomes higher than 1 A/cm2 and tunnel current increases significantly. Therefore, materials are needed to provide excellent electrical characteristics such as dielectric constant higher than 30, interface-state-density less than 1 × 1011/cm2-eV, tunneling current less than 10 mA/cm2, and negligible hysteresis. Many high dielectric constant materials have been reported that could potentially replace SiO2. These include SiOxNy, Ta2O5, TiO2, Y2O3, CeO2, SrTiO3, Al2O3, La2O3, and silicates of hafnium and zirconium. These materials exhibit the desired high dielectric constants for applications as gate dielectrics in sub-100 nm silicon technology. However, detailed studies need to be performed to evaluate the compatibility of these materials with the rest of the silicon integrated-circuit manufacturing processes.

Similar content being viewed by others

References

D. Muller, “The Electronic Structure at the Atomic Scale of Ultrathin Gate Oxides,” Nature, 399 (1999), p. 785.

The National Technology Roadmap for Semiconductors (San Jose, CA: Semiconductor Industry Association, 1997).

Semiconductor Research Corporation. www.scr.org/about/itrs_update.dgw.

M. Cao et al., “Boron Diffusion and Penetration in Ultra thin Oxide with Poly-si Gate,” IEEE Electron Device Lett., 19 (1998), p. 291.

B.Y. Kim et al., “Impact of Boron Penetration on Gate Oxide Reliability and Device Lifetime in p PolypMOSFET’s” (Paper presented at the IEEE International Electron Devices Meeting (IEDM’97) Washington, D.C., 1997).

E. Ibok et al., “Gate Quality Ultrathin (2.5 nm) PECVD Deposited Oxynitride and Nitride Oxide Dielectrics,” IEEE Electron Device Lett., 20 (9) (1999), p. 442.

Y. Wu, Y.M. Lee, and G. Lucovsky, “1.6 nm Oxide Equivalent Gate Dielectrics Using Nitride/Oxide (N/O) Composites Prepared by RPECVD/Oxidation Process,” IEEE Electron Device Lett., 21 (3) (2000), pp. 116–118; and H. Kwon and H. Hwang, “Electrical Characteristics of Ultrathin Gate Oxide Prepared by Post Oxidation Annealing in ND3,” Appl. Phys. Lett., 76 (2000), pp. 772–774.

Y. Wu and G. Lucovsky, “Ultrathin Nitride Oxide (N/O) Gate Dielectrics for p+ Polysilicon Gated PMOSFET’s Prepared by a Combined Remote Plasma Enhanced CVD/Thermal Oxidation Process,” IEEE Electron Device Lett., 19 (10) (1998), p. 367; and C.C. Chen et al., “Plasma Induced Charging Damage in Ultrathin (3 nm) Gate Oxides,” IEEE Trans. of Electron Dev., 47 (7) (2000), pp. 1355–1360.

M.L. Green et al., “Thermal Routes to Ultrathin Oxynitrides,” Foundamental Aspects of Ultrathin Dielectrics on Si-based Devices, ed. E. Garfunkel, E.P. Gusev, and A.Y. Vul (Dordrecht, Netherlands: Kluwer Academic Publishers, 1998), p. 181.

G.D. Wilk, R.M. Wallace, and J.M. Anthony, “Hafnium and Zirconium Silicates for Advanced Gate Dielectrics,” J. Appl. Phys., 87 (1) (2000), pp. 484–492.

Y.H. Wu et al., “Electrical Characteristics of High Quality La2O3 Gate Dielectric with Equivalent Oxide Thickness of 5 Å,” IEEE Electron Device Lett., 21 (7) (2000), pp. 341–343.

M.S. Joo et al., “Effect of Nitridation Pressure on the Characteristics of Gate Dielectrics Annealed in N2O Ambient,” IEEE Electron Device Lett., 20 (9) (1999), pp. 445–447.

Y. Wu, G. Lucovsky, and Y. Lee, “The Performance and Reliability of PMOSFETs with Ultrathin Silicon Nitride/Oxide Stacked Gate Dielectrics with Nitride Si-SiO2 Interfaces Prepared by Remote Plasma Enhanced CVD and Post Deposition Rapid Thermal Annealing,” IEEE Trans. of Electron Dev., 47 (7) (2000), pp. 1361–1369.

G.D. Wilk, R.M. Wallace, and J.M. Anthony, “Hafnium and Zirconium Silicates for Advanced Gate Dielectrics,” J. Appl. Phys., 87 (1) (2000), pp. 484–492.

Author information

Authors and Affiliations

Additional information

For more information, contact A. Kumar, Center for Microelectronics Research, University of South Florida, 4202 East Fowler Avenue, Tampa, Florida, 33620, (813) 974-3942; fax (813) 974-6310; e-mail akumar1@eng.usf.edu

Rights and permissions

About this article

Cite this article

Sharma, R.K., Kumar, A. & Anthony, J.M. Advances in high-k dielectric gate materials for future ULSI devices. JOM 53, 53–55 (2001). https://doi.org/10.1007/s11837-001-0105-9

Issue Date:

DOI: https://doi.org/10.1007/s11837-001-0105-9