Abstract

A dual-metal gate with a high-k spacer and a graded channel nanotube is proposed and analyzed. It is a promising architecture to combat the prominent lateral band-to-band tunneling (L-BTBT)-based gate-induced drain leakage (GIDL) experienced in gate-all-around structures, and has a superior analog performance. A comparative analysis of dual metal gate (DMG) and single metal gate (SMG) structures shows the higher efficacy of the DMG and high-k spacer structures. The proposed device structure offers peaks for gm, fT, gd, and IDS at 0.065 mS, 980 GHz, 0.11 mS/μm, and 10−3 A, respectively, making them a good choice for analog applications in the terahertz range. The work function tuning of the dual gate is demonstrated, and the use of graded channel and high-k spacers makes the proposed device a reliable candidate for scaling and applications, while being cost-effective and in sync with existing fabrication processes. This work illustrates the benefits of DMG with a high-k spacer over SMG and DMG structures without high-k spacer counterparts. It provides an incentive for further experimental exploration.

Similar content being viewed by others

References

G. Baccarani, M.R. Wordeman, and R.H. Dennard, Generalized Scaling Theory and Its Application to a ¼ Micrometer MOSFET Design. IEEE Trans. Electron Dev. 31, 452 (1984).

S.K. Sharma, B. Raj, and M. Khosla, A Gaussian Approach for Analytical Subthreshold Current Model of Cylindrical Nanowire FET with Quantum Mechanical Effects. Microelectronics 53, 65 (2016).

J.-P. Colinge, C.-W. Lee, A. Afzalian, N.D. Akhavan, R. Yan, I. Ferain, P. Razavi, B. O’Neill, A. Blake, M. White, A.-M. Kelleher, B. McCarthy, and R. Murphy, Nanowire Transistors Without Junctions. Nat. Nanotechnol. 5, 225 (2010).

R.R. Schaller, Technological Innovation in the Semiconductor Industry: A Case Study of the International Technology Roadmap for Semiconductors (ITRS) (2004).

K.J. Kuhn, Considerations for Ultimate CMOS Scaling. IEEE Trans. Electron Dev. 59, 1813 (2012).

A. Sarkar, A.K. Das, S. De, and C.K. Sarkar, Effect of Gate Engineering in Double-Gate MOSFETs for Analog/RF Applications. Microelectron. J. 43, 873 (2012).

D. Nagy, G. Indalecio, A.J. Garcia-Loureiro, M.A. Elmessary, K. Kalna, and N. Seoane, FinFET Versus Gate-All-Around Nanowire FET: Performance, Scaling, and Variability. IEEE J. Electron Dev. Soc. 6, 332 (2018).

S. Sahay, and M.J. Kumar, Nanotube Junctionless FET: Proposal, Design, and Investigation. IEEE Trans. Electron Dev. 64, 1851 (2017).

H.M. Fahad, C.E. Smith, J.P. Rojas, and M.M. Hussain, Silicon Nanotube Field Effect Transistor with Core–Shell Gate Stacks for Enhanced High-Performance Operation and Area Scaling Benefits. Nano Lett. 11, 4393 (2011).

H.M. Fahad, and M.M. Hussain, Are Nanotube Architectures More Advantageous than Nanowire Architectures for Field Effect Transistors? Sci. Rep. 2, 475 (2012).

S. Rewari, V. Nath, S. Haldar, S.S. Deswal, and R.S. Gupta, Gate Induced Drain Leakage Reduction in Cylindrical Dual-Metal Heterodielectric Gate All Around MOSFET. IEEE Trans. Electron Dev. 65, 3 (2017).

S. Rewari, V. Nath, S. Haldar, S.S. Deswal, and R.S. Gupta, Hafnium Oxide Based Cylindrical Junctionless Double Surrounding Gate (CJLDSG) MOSFET for High Speed, High Frequency Digital and Analog Applications. Microsyst. Technol. 25, 1527 (2019).

F. Lagraf, D. Rechem, K. Guergouri, and M. Zaabat, Channel Length Effect on Subthreshold Characteristics of Junctionless Trial Material Cylindrical Surrounding-Gate MOSFETs with High-k Gate Dielectrics. J. Nano Electron. Phys. 11, 02011 (2019).

V. Saha, and Mahapatra, Charge-Plasma Based Process Variation Immune Junctionless Transistor. IEEE Electron Device Lett. 35, 411 (2014).

S. Chakraborty, A. Dasgupta, R. Das, A. Kundu, and C.K. Sarkar, Impact of Asymmetric Dual-k Spacer in the Underlap Regions of Sub 20nm NMOSFET with Gate Stack. Superlattices Microstruct. 98, 448 (2016).

M.J. Kumar, and S. Sahay, Controlling BTBT Induced Parasitic BJT Action in Junctionless FETs Using a Hybrid Channel. IEEE Trans. Electron Dev. 63, 3350 (2016).

A. Rai, D. Vaithiyanathan, and B. Raj, Performance Analysis of Channel and Inner Gate Engineered GAA Nanowire FET. Silicon Chem. 13, 1863 (2021).

A. Rai, D. Vaithiyanathan, and B. Raj, Performance Analysis of Charge Plasma induced Graded Channel Si Nanotube. J. Eng. Res. 9, 146 (2021).

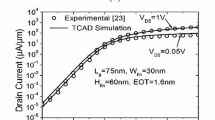

ATLAS 3D Device Simulator. SILVACO International, Santa Clara (2019).

W. Long, H. Ou, J.-M. Kuo, and K.K. Chin, Dual-Material Gate (DMG) Field Effect Transistor. IEEE Trans. Electron Dev. 46, 865 (1999).

A. Garg, Y. Singh, and B. Singh, Dual-Channel Junctionless FETs for Improved Analog/RF Performance. Silicon Chem. 13, 1499 (2021).

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

Conflict of interest

The authors declare that they have no conflict of interest, and this research received no specific Grant from any funding agency.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Rai, A., Vaithiyanathan, D. & Raj, B. Analog Performance Analysis of High-K Spacer Dual Material Gate Graded Channel Nanotube. J. Electron. Mater. 52, 422–428 (2023). https://doi.org/10.1007/s11664-022-10003-3

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11664-022-10003-3