Abstract

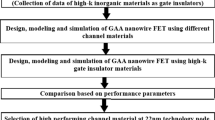

The present paper presents a graded channel NWFET using a doping-less technique with a core gate covering the channel and drain region. The graded channel and inner gate further suppresses the short channel effects and enhances the device performance capabilities. The performance metrics of the aforementioned device are calculated and compared with Charge Plasma and junctionless GAA-NWFET. The results show that our proposed structure exhibits improved Ion, Ioff, subthreshold slope (SS) and drain induced barrier lowering (DIBL). The graded channel has been effectively created by means of the charge plasma technique inorder to decrease the fabrication cumbersomeness. To enhance the channel controllability further, using an inner gate is proposed. Our proposed device aims at making MOSFET more striking to carry on with the scaling trends.

Similar content being viewed by others

References

Nagy D, Indalecio G, Garcia-Loureiro AJ, Elmessary MA, Kalna K, Seoane N (2018) FinFET versus gate-all-around nanowire FET: performance, scaling, and variability. IEEE J Electron Devices Soc 6(1):332–340

Sharma SK, Raj B, Khosla M (2019) Enhanced Photosensivity of Highly Spectrum Selective Cylindrical Gate In1-xGaxAs Nanowire MOSFET Photodetector. Modern Physics letter-B 33(12):1950144

Jain A, Sharma S, Raj B (2018) Analysis of triple metal surrounding gate (TM-SG) III-V nanowire MOSFET for Photosensing application. Opto-electronics Journal, Elsevier 26(2):141–148

Sharma S, BRaj MK (2017) Subthreshold Performance of In1-xGaxAs based Dual Metal with Gate Stack Cylindrical/Surrounding Gate Nanowire MOSFET for Low Power Analog Applications. Journal of Nanoelectronics and Optoelectronics, American Scientific Publishers, USA 12:171–176

Shan C, Wang Y, Bao MT (2016) A charge-plasma-based transistor with induced Graded Channel for enhanced analog performance. IEEE Trans Electron Devices 63(6):2275–2281

Jain A, Sharma S, Raj B (2016) Design and analysis of high sensitivity Photosensor using cylindrical surrounding gate MOSFET for low power sensor applications. Engineering Science and Technology, an International Journal, Elsevier’s 19(4):1864–1870

Sharma S, BRaj MK (2016) A Gaussian Approach for Analytical Subthreshold Current Model of Cylindrical Nanowire FET with Quantum Mechanical Effects. Microelectronics Journal, Elsevier 53:65–72

Sahay S, Kumar MJ (2016) Insight into lateral band-to-band-tunneling in nanowire Junctionless FETs. IEEE Trans Electron Devices 63(10):4138–4142

Hueting RJE, Rajasekharan B, Salm C, Schmitz J (2008) The charge plasma P-N diode. IEEE Electron Device Lett 29(12):1367–1369

Kumar MJ, Nadda K (2012) Bipolar charge-plasma transistor: a novel three terminal device. IEEE Trans Electron Devices 59(4):962–967

Sahu C, Singh J (2014) Charge-plasma based process variation immune junctionless transistor. IEEE Electron Device Lett 35(3):411–413

Kumar MJ, Janardhanan S (2013) Doping-less tunnel field effect transistor: design and investigation. IEEE Trans Electron Devices 60(10):3285–3290

Kranti J-PRA, Chung TM, Flandre D (2004) Laterally asymmetric MOSFETs, channel engineering in fully depleted double gate SOI for high performance analog applications. Solid State Electron 48(6):947–959

Kranti A, Armstrong GA (2007) Design and optimization of FinFETs for ultra-low-voltage analog applications. IEEE Trans Electron Devices 54(12):3308–3316

Singh S, Yadav S, Rahul J, Srivastava A, Raj B (2015) Impact of HfO2 in Graded Channel dual insulator double gate MOSFET. Journal of Computational and Theoretical Nanoscience, American Scientific Publishers 12(6):950–953

Chen Y, Mohamed M, Jo M, Ravaioli U, Xu R (2013) Junctionless MOSFETs with laterally graded-doping channel for analog/RF applications. J Comput Electron 12(4):757–764

Tayal S, Nandi A (2017) Analog/RF performance analysis of inner gate engineered junctionless Si nanotube. Superlattice Microst 111:862–871

Jain AK, Singh J, Kumar MJ (2019) Investigation of the Scalability of Emerging Nanotube Junctionless FETs Using an Intrinsic Pocket. IEEE J. Electron Devices Soc. 7:888–896

Sahay S, Kumar MJ (2017) Nanotube Junctionless FET: proposal, design, and investigation. IEEE Trans Electron Devices 64(4):1851–1856

HH Tran and JW Sleight (2014). “Us8871576,” vol. 2, no. 12

Sharma D, Vishvakarma SK (2015) Analyses of DC and analog/RF performances for short channel quadruple-gate gate-all-around MOSFET. Microelectron J 46(8):731–739

Sahu C, Singh J (2015) Potential benefits and sensitivity analysis of dopingless transistor for low power applications. IEEE Trans Electron Devices 62(3):729–735

RT Doria, RD Trevisoli, and MA Pavanello (2011). “Impact of the Series Resistance in the I-V Characteristics of nMOS Junctionless Nanowire Transistors,” vol. 39, no. 1, pp. 231–238

ATLAS Device Simulator Software (2012). Silvaco, Santa Clara, CA, USA

Kumar S, Raj B (2016) Analysis of ION and Ambipolar Current for Dual-Material Gate-drain Overlapped DG-TFET. Journal of Nanoelectronics and Optoelectronics, American Scientific Publishers, USA 11:323–333

Choi SJ, Il Moon D, Kim S, Duarte JP, Choi YK (2011) Sensitivity of threshold voltage to nanowire width variation in junctionless transistors. IEEE Electron Device Lett 32(2):125–127

Junctionless N, Effect F, Sahay S, Member S, Kumar MJ, Member S (2017) Diameter Dependence of Leakage Current in. IEEE Trans Electron Devices 64(3):1330–1335

Fahad HM, Hussain MM (2012) Are nanotube architectures more advantageous than nanowire architectures for field effect transis-tors? Sci Rep 2:475

Fahad HM, Smith CE, Rojas JP, Hussain MM (2011) Silicon nanotube field effect transistor with core–shell gate stacks for enhanced high-performance operation and area scaling benefits. Nano Lett 11(10):4393–4399

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher’s Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Ashima, Vaithiyanathan, D. & Raj, B. Performance Analysis of Channel and Inner Gate Engineered GAA Nanowire FET. Silicon 13, 1863–1869 (2021). https://doi.org/10.1007/s12633-020-00575-2

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s12633-020-00575-2