Abstract

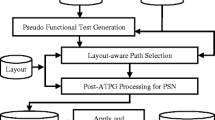

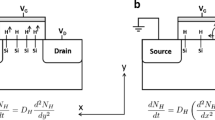

Power-supply noise is one of the major contributing factor for yield loss in sub-micron designs. Excessive switching in test mode causes supply voltage to droop more than in functional mode leading to failures in delay tests that would not occur otherwise under normal operation. Thus, there exists a need to accurately estimate on-chip supply noise early in the design phase to meet power requirements in normal mode and during test to prevent overstimulation during the test cycle and avoid false failures. Simultaneous switching activity (SSA) of several logic components is one of the main sources of power-supply noise (PSN) which results in reduction of supply voltages at the power-supplies of the logic gates. Most existing techniques and tools predict static IR-drop, which accounts for only part of the total voltage drop on the power grid. To our knowledge, inductive drop is not included in current noise analysis for simplification. The power delivery networks in today’s very deep-submicron chips are susceptible to slight variations and cause sudden large current spikes leading to higher Ldi ⁄ dt than resistive drop essentiating the need to account for this drop. Power-supply noise also impacts circuit operation incurring a significant increase in path delays. However, it is infeasible to carry out full-chip SPICE-level simulations on a design to validate the ATPG generated test patterns. Accurate and efficient techniques are required to quantify supply noise and its impact on path delays to ensure reliable operation in both mission mode and during test. We present a scalable current-based dynamic method to estimate both IR and Ldi / dt drop caused by simultaneous switching activity and use the technique to predict the increase in path delay. Our technique uses simulations of individual extracted paths in comparison to time-consuming full-chip simulations and thus it can be integrated with existing ATPG tools. The method uses these path simulations and a convolution-based technique to estimate power-supply noise and path delays. Simulation results for combinational and sequential benchmark circuits are presented demonstrating the effectiveness of our techniques.

Similar content being viewed by others

References

Ahmed N, Tehranipoor M, Jayaram V (2007) Supply voltage noise aware ATPG for Transition delay faults. In Proc 25th IEEE VLSI Test Symposium, pages 179–186

Andersson DA, Nilsson B, Pihl J, Svensson L, Larsson-Edefors P (2009, May 12–15) Supply voltage drop study considering on-chip self inductance of a 32-bit processor’s power grid. Signal Propagation on Interconnects, 2009. SPI’09. IEEE Workshop on, pp 1–4

Chiprout E (2004, Nov 7–11) Fast flip-chip power grid analysis via locality and grid shells. Computer Aided Design, 2004. IEEE/ACM International Conference on ICCAD-2004, pp 485–488

Galivanche R, Kapur R, Rubio A (2007, April 16–20) Testing in the year 2020. Design, Automation & Test in Conference & Exhibition, 2007. DATE ‘07, pp 1–6

Jiang Y-M, Cheng K-T (2001) Vector generation for power supply noise estimation and verification of deep submicron designs. IEEE Trans Very Large Scale Integr (VLSI) Syst 9(2):329–340

Kim HS, Walker DMH (2006) Statistical static timing analysis considering the impact of power supply noise in VLSI circuits. In Proc Seventh Int Workshop Microprocessor Test and Verification MTV ‘06, pages 76–82

Kokrady AA, Ravikumar CP (2003) Static verification of test vectors for IR drop failure. In Proc ICCAD2003 Computer Aided Design Int Conf, pages 760–764

Kozhaya JN, Nassif SR, Najm FN (2002) A multigrid-like technique for power grid analysis. IEEE Trans Comput Aided Des Integr Circ Syst 21(10):1148–1160

Lee J, Narayan S, Kapralos M, Tehranipoor M (2008, March 10–14) Layout-aware, IR-drop tolerant transition fault pattern generation. Design, Automation and Test in Europe, 2008. DATE ‘08, pp 1172–1177

Liu C, Wu Y, Hang Y (2007) Effect of IR-drop on path delay testing using statistical analysis. In Proc 16th Asian Test Symposium ATS ‘07, pages 245–250

Ma J, Lee J, Tehranipoor M (2009, May 3–7) Layout-aware pattern generation for maximizing supply noise effects on critical paths. VLSI Test Symposium, 2009. VTS ‘09. 27th IEEE, pp 221–226

Nourani M, Radhakrishnan A (2005, Nov 8–8) Power-supply noise in SoCs: ATPG, estimation and control. Test Conference, 2005. Proceedings. ITC 2005. IEEE International, pp 10 pp -516

Pant S, Chiprout E (2006) Power grid physics and implications for CAD. In Proc of Design Automation Conf (DAC), pp 199–204

Rad RM, Plusquellic J (2009) A novel fault localization technique based on deconvolution and calibration of power pad transient signals. J Electron Test 25:169–185

Rao SK, Robucci R, Patel C (2013, April 29–May 2) Scalable dynamic technique for accurately predicting power-supply noise and path delay. VLSI Test Symposium (VTS), 2013 I.E. 31st, pp 1,6

Rao SK, Sathyanarayana C, Kallianpur A, Robucci R, Patel C (2012, April 23–25) Estimating Power Supply Noise and its impact on path delay. VLSI Test Symposium (VTS), 2012 I.E. 30th, pp 276–281

Singh A, Plusquellic J, Phatak D, Patel C (2006) Defect simulation methodology for iddt testing. J Electron Test 22:255–272

Wang J, Walker DMH, Majhi A, Kruseman B, Gronthoud G, Villagra LE, van de Wiel P, Eichenberger S (2006) Power supply noise in delay testing. In Proc IEEE Int Test Conf ITC ‘06, pages 1–10

Wang J, Yue Z, Lu X, Qiu W, Shi W, Walker DMH. A vector-based approach for power supply noise analysis in test compaction. In Proc IEEE Int Test Conf ITC 2005

Xu Q, Hu D, Xiang D (2007, Oct 21–26) Pattern-directed circuit virtual partitioning for test power reduction. Test Conference, 2007. ITC 2007. IEEE International, pp 1–10

Zhao S, Roy K, Koh CK (2000) Estimation of Inductive and resistive switching noise on power supply network in deep sub-micron CMOS circuits. In Proc Int Computer Design Conf, pages 65–72

Zhong Y, Wong MDF (2005, Nov 6–10) Fast algorithms for IR drop analysis in large power grid. Computer-Aided Design, 2005. ICCAD-2005. IEEE/ACM International Conference on, pp 351–357

Author information

Authors and Affiliations

Corresponding author

Additional information

Responsible editor: M. Tehranipoor

Rights and permissions

About this article

Cite this article

Kadiyala Rao, S., Robucci, R. & Patel, C. Simulation Based Framework for Accurately Estimating Dynamic Power-Supply Noise and Path Delay. J Electron Test 30, 125–147 (2014). https://doi.org/10.1007/s10836-013-5425-5

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10836-013-5425-5