Abstract

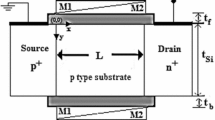

The present paper analyzes the 2-dimensional surface potential model designed using Double Gate Vertical TFET (DGV-TFET). The proposed model using the Matlab tool possesses an inherited trait of TFET, namely the dual modulation effect. The dual modulation effect describes a control over the surface potential of biasing voltages utilized to compute a tunneling depletion width value upon source and drain junctions. Hence, the device tunneling current exploits the potential model to derive the current model. The parabolic approximation methods are utilized to evaluate 2-D Poisson equations for proper boundary conditions. The present paper analyzes surface potential outline dependence upon different device metrics by changing device materials, gate/drain-source potential, gate oxide permittivity, and gate electrode work-function. Resultingly, the channel’s surface potential is derived considering an accurate change in gate and drain biases. Thus, the proposed model efficiency is confirmed by describing results analytically in favour of simulations.

Similar content being viewed by others

References

P. Bergveld, Thirty years of ISFETOLOGY: what happened in the past 30 years and what may happen in the next 30 years. Sens. Actuators B Chem. 88(1), 1–20 (2003). https://doi.org/10.1016/S0925-4005(02)00301-5

K. Boucart, A.M. Ionescu, Double-gate tunnel FET with high gate dielectric. IEEE Trans. Electron Devices 54(7), 1725–1733 (2007). https://doi.org/10.1109/.TED.2007.899389

T.S. Arun Samuel, N.B. Balamurugan, S. Sibitha, R. Saranya, D. Vanisri, Analytical modeling and simulation of dual material gate tunnel field effect transistors. J. Electr. Eng. Technol. 8(6), 1481–1486 (2013). https://doi.org/10.5370/JEET.2013.8.6.1481

G. Wadhwa, B. Raj, Label free detection of biomolecules using charge-plasma-based gate underlap dielectric modulated junctionless TFET. J. Electron. Mater. 47(8), 4883–4893 (2018)

K. Boucart, A.M. Ionescu, Double-gate tunnel FET with high-$\kappa $ gate dielectric. IEEE Trans. Electron Devices 54(7), 1725–1733 (2007). https://doi.org/10.1109/TED.2007.899389

S. Singh, S.K. Vishvakarma, B. Raj, Analytical modeling of split-gate junction-less transistor for a biosensor application. Sens Bio Sens 18, 31–36 (2018). https://doi.org/10.1016/j.sbsr.2018.02.001

S. Badgujjar et al., Design and analysis of dual source vertical tunnel field effect transistor for high performance. Trans. Electr. Electron. Mater. (2019). https://doi.org/10.1007/s42341-019-00154-2

M.J. Kumar, S. Janardhanan, Doping-less tunnel field effect transistor: design and investigation. IEEE Trans. Electron Devices 60, 3285–3290 (2013). https://doi.org/10.1109/TED.2013.2276888

R. Vishnoi, M.J. Kumar, A pseudo-2-D-analytical model of dual material gate all-around nanowire tunneling FET. IEEE Trans. ElectronDevices 61(7), 2264–2270 (2014)

A. Zhan, J. Mei, L. Zhang, H. He, J. He, and M. Chan, Numerical study on dual material gate nanowire tunnel field-effect transistor, in Proceedings of the IEEE International Conference on Electron Devices and Solid State Circuit (EDSSC), 2012, pp. 1–5

H. Lou et al., A junctionless nanowire transistor with a dual-material gate. IEEE Trans. Electron Devices 59(7), 1829–1836 (2012)

S. Kumar, B. Raj, Simulations and modeling of TFET for low power design, in Handbook of Research on Computational Simulation and Modeling in Engineering. ed. by F. Miranda, C. Abreu (IGI Global, Pennsylvania, 2015), pp.650–679. https://doi.org/10.4018/978-1-4666-8823-0.ch021

G. Wadhwa, B. Raj, Surface potential modeling and simulation analysis of dopingless TFET biosensor. SILICON 14, 1–10 (2021)

G. Jain, R.S. Sawhney, R. Kumar, G. Wadhwa, Analytical modeling analysis and simulation study of dual material gate underlap dopingless TFET. Superlattices Microstruct. 153, 106866 (2021)

T.S. Arun Samuel, N.B. Balamurugan, S. Bhuvaneswari, D. Sharmila, K. Padmapriya, Analytical modeling and simulation of single-gate SOI TFET for low-power applications. Int. J. Electron. 101(6), 779–788 (2014). https://doi.org/10.1080/00207217.2013.796544

G. Wadhwa, B. Raj, An analytical modeling of charge plasma based tunnel field effect transistor with impacts of gate underlap region. Superlattices Microstruct. 142, 106512 (2020)

J. Madan, R. Pandey, R. Sharma, R. Chaujar, Impact of metal silicide source electrode on polarity gate induced source in junctionless TFET. Appl. Phys. A 125(9), 1–7 (2019)

C. Wu et al., An analytical surface potential model accounting for the dual-modulation effects in tunnel FETs. IEEE Trans. Electron Devices 61(8), 2690–2696 (2014). https://doi.org/10.1109/TED.2014.2329372

Silvaco, Version 5.15.32.R. (2009). http://www.silvaco.com

J. Madan, M. Dassi, R. Pandey, R. Chaujar, R. Sharma, Numerical analysis of Mg2Si/Si heterojunction DG-TFET for low power/high performance applications: Impact of non-idealities. Superlattices Microstruct. 139, 106397 (2020)

L. Zhang, C. Ma, J. He, X. Lin, M. Chan, Analytical solution of subthreshold channel potential of gate underlap cylindrical gate-all around MOSFET. Solid State Electron. 54(8), 806–808 (2010). https://doi.org/10.1016/j.sse.2010.03.020

S.C. Lin, J.B. Kuo, Modeling the fringing electric field effect on the threshold voltage of FD SOI nMOS devices with the LDD/sidewall oxide spacer structure. IEEE Trans. Electron Devices 50(12), 2559–2564 (2003). https://doi.org/10.1109/TED.2003.816910

M. Gholizadeh, S.E. Hosseini, A 2-D analytical model for double gate tunnel FETs. IEEE Trans. Electron Devices 61(5), 1494–1500 (2014). https://doi.org/10.1109/TED.2014.2313037

R. Vishnoi, M. Kumar, Compact analytical drain current model of gate-all-around nanowire tunneling FET. IEEE Trans. Electron Devices 61(7), 2599–2603 (2014). https://doi.org/10.1109/.TED.2014.2322762

C. Wu, R. Huang, Q. Huang, C. Wang, J. Wang, Y. Wang, An analytical surface potential model accounting for the dual-modulation effects in tunnel FETs. IEEE Trans. Electron Devices 61(8), 2690–2696 (2014). https://doi.org/10.1109/TED.2014.2329372

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

Conflict of interest

The authors confirm that this manuscript has no conflict of interest.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Kumar, H., Verma, A.K., Patle, A. et al. Potential Analysis of Double Gate Vertical TFET Using 2-D Modeling for Low Power Application. Trans. Electr. Electron. Mater. 24, 314–322 (2023). https://doi.org/10.1007/s42341-023-00449-5

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s42341-023-00449-5