Abstract

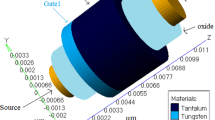

Execution grids of developing electronic devices are being examined to find substitutes for MOSFETs in the quest to minimize power dissipation and ease energy efficiency limitations. The innovative architecture of negative capacitance field effect transistors (NCFETs), which offer advantages from the design, performance, and fabrication perspectives, is presented and examined in this article. This proposed structure in this work is called Modified NCFET. Modification of NCFET includes the Density-Functional-Theory (DFT) based atomic modelling for Ferroelectric material Hafnium Oxide (FEHfO2) with different doping concentrations of silicon (Si). The performance metrics of Modified NCFET are compared with conventional MOSFET designed on the same technology node to draw the effect of Si-doped HfO2. DFT calculations like Projected Density of States (PDOS), and energy band structure are done using the Quantum Atomistix Tool Kit (ATK) simulator which is atomic-scale modelling software, and device modelling is done by the Visual Technology-Computer-Aided-Design (TCAD) simulator. The device performance comparison of Modified NCFET and conventional MOSFET is done by the Visual TCAD in terms of short-channel effects (SCEs), analog/RF matrices, and FET-based inverter parameters (noise margin (NM), voltage transfer characteristics (VTC)). Additionally, the proposed NCFET is contrasted with the various FOMs' IRDS criteria.

Similar content being viewed by others

Data Availability

“The authors mentioned above have all the relevant data associated with this research work and will be dedicated to sharing that they will be asked to do so in the future.”

References

Moore GE (1998) Cramming more components onto integrated circuits. Proc IEEE 86:82–85

Jeon DY, Park SJ, Mouis M, Barraud S, Kim GT, Ghibaudo G (2013) Low-temperature electrical characterization of junctionless transistors. Solid State Electron 80:135–141

Kumar A, Gupta N, Chaujar R (2016) TCAD RF performance investigation of transparent gate recessed channel MOSFET. Microelectron J 49:36–42

Sreenivasulu VB, Narendar V (2022) Design and temperature assessment of junctionless nanosheet FET for nanoscale applications. SILICON 14:3823–3834

Narendar V (2018) Performance enhancement of finfet devices with gate-stack (GS) High-K dielectrics for nanoscale applications. SILICON 10:2419–2429

Awadhiya B, Kondekar PN, Yadav S, Upadhyay P (2020) Insight into threshold voltage and drain-induced barrier lowering in negative capacitance field effect transistor. Trans Electr Electron Mater 22:267–273

Salahuddin S, Datta S (2008) Use of negative capacitance to provide voltage amplification for low power nanoscale devices. Nano Lett 8:405–410

Goswami Y, Ghosh B, Asthana PK (2014) Analog performance of Si junctionless tunnel field effect transistor and its improvisation using III-V semiconductor. RSC Adv 4:10761–10765

Lo SH, Buchanan DA, Taur Y, Wang W (1997) Quantum mechanical modeling of electron tunneling current from the inversion layer of ultra-thin-oxide nMOSFETs. IEEE Electron Device Lett 18:209–211

Pathak Y, Malhotra BD, Chaujar R (2022) Detection of biomolecules in dielectric modulated double metal below ferroelectric layer FET with improved sensitivity. J Mater Sci: Mater Electron 33:13558–13567

Pathak Y, Malhotra BD, Chaujar R (2022) Analog/RF performance and effect of temperature on ferroelectric layer improved FET device with spacer. SILICON 14:12269–12280

Mann R, Chaujar R (2022) TCAD investigation of ferroelectric based substrate MOSFET for digital application. SILICON 14:5075–5084

Bheemana RC, Japa A, Yellampalli SS, Vaddi R (2023) Negative capacitance FET based energy efficient and DPA attack resilient ultra-light weight block cipher design. Microelectron J 133:105711

Kumar B, Sharma M, Chaujar R (2023) Gate electrode work function engineered JAM-GS-GAA FinFET for analog/RF applications: Performance estimation and optimization. Microelectron J 135:105766

Visual TCAD manual “https://www.cogenda.com/article/VisualTCAD”

Mukherjee A, Debnath P, Nirmal D, Chanda M (2023) A new analytical modelling of 10 nm negative capacitance-double gate TFET with improved cross-talk and miller effects in digital circuit applications. Microelectron J 133:105689

Basak A, Sarkar A (2021) Quantum analytical model for lateral dual gate UTBB SOI MOSFET for Analog/RF performance. SILICON 13:3131–3139

Basak A, Sarkar A (2022) Drain current modelling of asymmetric junctionless dual material double gate MOSFET with High K gate stack for analog and RF performance. SILICON 14:75–86

Tu L, Cao R, Wang X, Chen Y, Wu S, Wang F, Wang Z, Shen H, Lin T, Zhou P, Meng X, Hu W, Liu Q, Wang J, Liu M, Chu J (2020) Ultrasensitive negative capacitance phototransistors. Nat Commun 11:4–11

Awadhiya B, Kondekar PN, Yadav S, Upadhyay P (2021) Insight into threshold voltage and drain-induced barrier lowering in negative capacitance field effect transistor. Trans Electr Electron Mater 22:267–273

Pahwa G, Agarwal A, Chauhan YS (2018) Numerical Investigation of Short Channel Effects in Negative Capacitance MFIS and MFMIS Transistors: Subthreshold Behavior. IEEE Trans Electron Devices 65:5130–5136

Pradhan KP, Mohapatra SK, Sahu PK, Behera DK (2014) Impact of high-k gate dielectric on analog and RF performance of nanoscale DG-MOSFET. Microelectron J 45:144–151

Kumar A, Tripathi MM, Chaujar R (2018) Comprehensive analysis of sub-20 nm black phosphorus-based junctionless-recessed channel MOSFET for analog/RF applications. Superlattices Microstruct 116:171–180

Pradhan KP, Mohapatra SK, Sahu PK, Behera DK (2014) Impact of high-k gate dielectric on analog and RF performance of nanoscale DG-MOSFET. Microelectronics J 45:144–151

Jena B, Dash S, Routray SR, Mishra GP (2019) Inner-gate-engineered GAA MOSFET to enhance the electrostatic integrity. NANO 14:1–8

Narendar V, Girdhardas KA (2018) Surface potential modeling of Graded-Channel gate-stack (GCGS) high-K dielectric dual-material double-gate (DMDG) MOSFET and analog/RF performance study. SILICON 10:2865–2875

Baruah K, Baishya S (2023) Numerical assessment of dielectrically-modulated short- double-gate PNPN TFET-based label-free biosensor. Microelectron J 133:105717

Kaharudin KE, Salehuddin F, Zain ASM, Roslan AF (2019) Effect of channel length variation on analog and RF performance of junctionless double gate vertical MOSFET. J Eng Sci Technol 14(4):2410–2430

Pundir YP, Saha R, Pal PK (2020) Effect of gate length on performance of 5nm node N-channel nano-sheet transistors for analog circuits. Semicond Sci Technol 36(1):015010

Sreenivasulu VB, Narendar V (2022) Junctionless gate-all-around nanowire FET with asymmetric spacer for continued scaling. SILICON 14:7461–7471

Jeyanthi JE, Samuel TSA, Arivazhagan L (2022) Optimization of design space parameters in tunnel fet for analog/mixed signal application. SILICON 14:8233–8241

Acknowledgements

“The authors are grateful to the Microelectronics Research Laboratory, Delhi Technological University, for supporting the work.”

Funding

“The authors declare that no funds, grants, or other support were received during the preparation of this manuscript.”

Author information

Authors and Affiliations

Contributions

Rashi Mann: Conceptualization, methodology, software, analysis, data curation, writing-original draft preparation.

Rishu Chaujar: Writing—review and editing at different stages, supervision.

Corresponding author

Ethics declarations

“The authors have seen all the Ethical Standards and will supposed to follow them in the future.”

Consent to Participate & for Publication

“Since the concerned research paper is based on the ‘non-life science journal.’ So, ‘Not Applicable’ here. However, the authors have gone through all journal policies and consented to the authorities for further processing.”

Competing Interests

The authors declare no competing interests.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Mann, R., Chaujar, R. DFT-based Atomic Calculation of Si-doped HfO2 and Effect of its Negative Capacitance on Analog/RF, and VTC Parameters of MOSFET. Silicon 16, 1237–1252 (2024). https://doi.org/10.1007/s12633-023-02734-7

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s12633-023-02734-7