Abstract

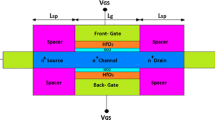

In this paper, we have performed the scaling of asymmetric junctionless (JL) SOI nanowire (NW) FET at 10 nm gate length (LG). To study the device electrical performance various DC metrics like SS, DIBL, ION/IOFF ratio are discussed. Even at 5 nm, the device has good electrical properties with subthreshold swing (SS) = ~64 mV/dec, drain induced barrier lowering (DIBL) = ~45 mV/V, and switching ratio (ION/IOFF) = ~106 shows a higher level of electrostatic integrity. At 5 nm LG with optimized spacer dielectric the device exhibits ~5 orders of improvement in IOFF and the improvement is less than ~2 orders at 20 nm LG. Thus, from the result analysis, the spacer dielectrics are essential at lower LG for better performance. For continued scaling, the HfO2 spacer dielectric ensures high performance with the lowest downfall in ION with 11.24% and the decline is 15.8% and 13.26% with no spacer and Si3N4 respectively. With SiO2, Si3N4, and HfO2 spacers the asymmetric spacer ensures an ION/IOFF of ~106 which is permissible for ITRS low power requirements. Moreover, to study scaling flexibility towards analog/RF applications various parameters like transconductance (gm), transconductance generation factor (TGF), total gate capacitance (Cgg), and cutoff frequency (fT) are also determined. Furthermore, the scaling impact on dynamic power (DP) and static power (SP) consumption are also presented. The findings of the study show that asymmetric JL NW FET is one of the potential candidates for future technology nodes.

Similar content being viewed by others

References

Ernst T, et al. (Dec. 2006) Novel 3D integration process for highly scalable nanobeam stacked-channels GAA (NBG) FinFETs with HfO2/TiN gate stack, IEDM Tech. Dig., San Francisco, CA, USA, p 1–4. https://doi.org/10.1109/IEDM.2006.346955

Barraud S, et al. (2017) Performance and design considerations for gate-all-around stacked-NanoWires FETs, 2017 IEEE International Electron Devices Meeting (IEDM), p. 29.2.1–29.2.4. https://doi.org/10.1109/IEDM.2017.8268473

Yakimets D, Eneman G, Schuddinck P, Huynh Bao T, Garcia Bardon M, Raghavan P, Veloso A, Collaert N, Mercha A, Verkest D, Thean AV-Y, De Meyer K (May 2015) Vertical GAAFETs for the ultimate CMOS scaling. IEEE Trans Electron Devices 62(5):1433–1439. https://doi.org/10.1109/TED.2015.2414924

Wei Lu and Charles M Lieber (2006) Semiconductor nanowires J Phys D Appl Phys 39:R387. Available: http://stacks.iop.org/0022-3727/39/i=21/a=R01

Kola SR, Li Y, Thoti N (2020) Random telegraph noise in gate-all-around silicon nanowire MOSFETs induced by a single charge trap or random interface traps. J Comput Electron 19:253–262. https://doi.org/10.1007/s10825-019-01438-9

Mertens H, et al. (Dec. 2017) Vertically stacked gate-all-around Si nanowire transistors: key process optimizations and ring oscillator demonstration, IEDM Tech. Dig., San Francisco, CA, USA, p. 37.4.1–37.4.4. https://doi.org/10.1109/IEDM.2017.8268511

Bharath SV, Narendar V (2021) Design and Insights into Sub-10 nm Spacer Engineered Junctionless FinFET for Nanoscale Applications. ECS J Solid State Sci Technol 10(1):013008

Sreenivasulu VB, Narendar V (2021) Performance improvement of spacer engineered n-type soi finfet at 3-nm gate length. AEU-Int J Electron Commun 137:153803

Bharath Sreenivasulu V (2021) Vadthiya Narendar, characterization and optimization of junctionless gate-all-around vertically stacked nanowire FETs for sub-5 nm technology nodes. Microelectron J 116:105214. https://doi.org/10.1016/j.mejo.2021.105214

Goel A, Gupta SK, Roy K (2010) Asymmetric drain spacer extension (adse) finfets for low-power and robust srams. IEEE Trans Electron Devices 58(2):296–308

Cheng et al. (2008) Method of forming asymmetric spacers and methods of fabricating semiconductor device using asymmetric spacers, U.S. patent 0 233 691

(2015) International Technology Roadmap for Semiconductors (ITRS): [2015 International Technology Roadmap for Semiconductors (ITRS) - Semiconductor Industry Association]

Loubet N, Hook T, Montanini P, Yeung C-W, Kanakasabapathy S, Guillom M, Yamashita T, Zhang J, Miao X, Wang J, et al. (2017) Stacked nanosheet gate-all-around transistor to enable scaling beyond finfet. In: 2017 Symposium on VLSI Technology, IEEE, p. T230–T231

Rumar R, Kumar A (2020) Hetro-Dielctric (HD) oxide-engineered junctionless double gate all around (DGAA) nanotube field effect transistor (FET). Silicon 13:2177–2184

Madadi D, Orouji AA (2021) Investigation of tied double gate 4H–SiC junctionless FET in 7 nm channel length with a symmetrical dual p+ layer. Phys. E: Low-Dimens. Syst. Nanostructures 126:114450

Navaneetha A, Reddy AK, Deepthi SA et al (2021) Performance evaluation of noise coupling on germanium based TSV filled material for future IC integration technique. Mater Today Proc 45:1494–1497

Pandey CK, Singh A, Chaudhury S (2021) A simulation-based analysis of effect of interface trap charges on dc and analog/HF performances of dielectric pocket SOI-tunnel FET. Microelectron Reliab 122:114166. https://doi.org/10.1016/j.microrel.2021.114166

Pandey CK, Dash D, Chaudhury S (2020) Improvement in analog/RF performance of SOI TFET using dielctric pocket. Int J Electron 107:1844–1860

Saha R (2021) Simulation study on ferroelectric layer thickness dependence RF/analog and linearity parameters in ferroelectric tunnel junction TFET. Microelectron J 113:105081

Gupta N, Kumar A (2020) Assessment of High-k Gate Stack on Sub-10 nm SOI-FinFET for High Performance Analog and RF Applications Perspective. ECS J Solid State Sci Technol 9:123009

Barman R, Baishya K, Srimanta (2019) An insight to the performance of vertical super-thin body (VSTB) FET in presence of interface traps and corresponding noise and RF characteristics. Applied Physics A 125:865

Cherik C, Mohammadi I, Saeed (2021) Germanium-source L-shaped TFET with dual in-line tunneling junction. Applied Physics A 127:525

Yu E, Lee W, Jung J, Cho S (2018) Ultrathin SiGe shell channel p-type FinFET on bulk Si for sub-10-nm technology nodes. IEEE Trans Electron Dev 65:1290–1297

Panigrahy AK, Ghosh T, Vanjari SRK, Singh SG (2019) Surface density gradient engineering precedes enhanced diffusion; drives CMOS in-line process flow compatible cu–cu thermocompression bonding at 75° C. IEEE Trans Device Mater Reliab 19(4):791–795

Sreenivasulu VB, Narendar V (2021) Design and temperature assessment of junctionless nanosheet fet for nanoscale applications. Silicon:1–12. https://doi.org/10.1007/s12633-021-01145-w

Sreenivasulu VB, Narendar V (2021) A comprehensive analysis of Junctionless tri-gate (TG) FinFET towards low-power and high-frequency applications at 5-nm gate length. Silicon

Sreenivasulu VB, Narendar V (2021) Design insights into RF/analog and linearity/distortion of spacer engineered multi-fin SOI FET for terahertz applications. Int J RF Microw Comput Aided Eng 31(9):e22875. https://doi.org/10.1002/mmce.22875

Kumar B, Chaujar R (2021) Numerical Study of JAM-GS-GAA FinFET: A Fin Aspect Ratio Optimization for Upgraded Analog and Intermodulation Distortion Performance. Silicon. https://doi.org/10.1007/s12633-021-01395-8

Madadi D, Orouji AA, Abbasi A (2021) Improvement of nanoscale SOI MOSFET heating effects by vertical Gaussian drain-source doping region. Silicon 13:645–651

Das RR, Maity S, Chowdhury A, Chakraborty A (2021) RF/Analog performance of GaAs Multi-Fin FinFET with stress effect. Microelectron J 117:105267

Kale S (2020) Performance improvement and analysis of PtSi Schottky barrier p-MOSFET based on charge plasma concept for low power applications. Silicon 12:479–485. https://doi.org/10.1007/s12633-019-00161-1

Acknowledgements

The authors thank to the department of Electronics and Communications Engineering, NIT Warangal for providing the TCAD Tools.

Availability of Data and Material

Not applicable.

Funding

No Funding Received.

Author information

Authors and Affiliations

Contributions

V. Bharath Sreenivasulu: Writing- Original draft preparation, Formal Analysis, Investigation, Simulation, Data Curation.

V. Narendar: Supervision, Resources.

Corresponding author

Ethics declarations

The author has no conflicts of interest to declare that are relevant to the content of this article.

Financial Interests

The authors declare they have no financial interests.

Compliance with Ethical Standards

• The contents of this manuscript are not now under consideration for publication elsewhere;

• The contents of this manuscript have not been copyrighted or published previously

• The contents of this manuscript will not be copyrighted, submitted, or published elsewhere, while acceptance by the Journal is under consideration.

Consent to Participate

Not applicable.

Consent for Publication

Not applicable.

Additional information

Publisher’s Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Sreenivasulu, V.B., Narendar, V. Junctionless Gate-all-around Nanowire FET with Asymmetric Spacer for Continued Scaling. Silicon 14, 7461–7471 (2022). https://doi.org/10.1007/s12633-021-01471-z

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s12633-021-01471-z