Abstract

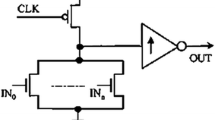

This paper’s objective is to design and analyze the comparator circuit employing domino logic with Variable Threshold Complementary Metal Oxide Semiconductor (VTCMOS) and extra clock gating hardware. VTCMOS is a useful technique for reducing static power consumption, since it uses low supply voltage and small threshold voltage while retaining high speed. Clock gating is employed to reduce dynamic power consumption. A multiplexer is utilized for the sake of clock gating and to maintain the state of a circuit constant. When the circuit is in active mode, the clock signal is transmitted through the domino logic, and when the circuit is in standby mode, the clock signal is bypassed to retain the circuit in the same condition. In comparison to static CMOS logic, the domino logic technique reduces the area while increasing speed. In 90 nm CMOS technology, a two input, three output 1-bit comparator is built. The assessed metrics include static power when no input transition occurs, dynamic power when an input transition occurs, and delay and power delay product (PDP). When comparing traditional domino logic, FDST domino logic, and GCRK domino logic with suggested domino logic, and simulation results are also included.

Access this chapter

Tax calculation will be finalised at checkout

Purchases are for personal use only

Similar content being viewed by others

References

Leblebici Y, Kang SM (1996) CMOS digital integrated circuits, analysis and design. McGraw-Hill, New York

Yeap GK (2012) Practical low power digital VLSI design. Springer

Nandini MR, Mor P, Keller JM (2016) A comparative study of static and dynamic CMOS logic. Int J Curr Eng Technol 6(3):1019–1021

Ding L, Mazumder P (2004) On circuit techniques to improve noise immunity of CMOS dynamic logic. IEEE Trans Very Large Scale Integr (VLSI) Syst 12(9):910–925

Singhal S, Mehra A, Tripathi U (2019) Power reduction in domino logic using clock gating in 16 nm CMOS technology. In: 2019 6th International conference on signal processing and integrated networks (SPIN). IEEE, pp 274–277

Garg S, Gupta TK (2018) Low power domino logic circuits in deep-submicron technology using CMOS. Eng Sci Technol Int J 21(4):625–638

Bansal D, Nagar BC, Singh BP, Kumar A (2020) Improved domino logic circuits and its application in wide fan-in OR gates. Micro Nano Syst 12(1):58–67

Rangari AV, Gaidhani YA (2016) Design of comparator using domino logic and CMOS logic. In: 2016 Online international conference on green engineering and technologies (IC-GET). IEEE, pp 1–6

Singhal S, Mehra A (2021) Gated clock and revised keeper (GCRK) domino logic design in 16 nm CMOS technology. IETE J Res 1–8

Huang CH, Wang JS (2003) High-performance and power-efficient CMOS comparators. IEEE J Solid-State Circuits 38(2):254–262

Author information

Authors and Affiliations

Corresponding author

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2024 The Author(s), under exclusive license to Springer Nature Singapore Pte Ltd.

About this paper

Cite this paper

Payyavula, R., Reddy, D.G.S. (2024). Power Optimized Domino Logic Design of a Comparator with Variable Threshold CMOS and Clock Gating. In: Gabbouj, M., Pandey, S.S., Garg, H.K., Hazra, R. (eds) Emerging Electronics and Automation. E2A 2022. Lecture Notes in Electrical Engineering, vol 1088. Springer, Singapore. https://doi.org/10.1007/978-981-99-6855-8_35

Download citation

DOI: https://doi.org/10.1007/978-981-99-6855-8_35

Published:

Publisher Name: Springer, Singapore

Print ISBN: 978-981-99-6854-1

Online ISBN: 978-981-99-6855-8

eBook Packages: Intelligent Technologies and RoboticsIntelligent Technologies and Robotics (R0)