Abstract

In cryptography, there is no simple methodology to obtain a True Random Number Generator (TRNG) that meets statistical requirements such as unpredictability, uniform distribution (bias) and independence (correlation) for random numbers. The statistical weakness occurring especially as a result of physical randomness and tried to be overcome by post-processing techniques is an important deficiency of TRNGs. In this study, the use of a novel lightweight post-processing technique based on chaotic substitution box (s-box) is proposed that can successfully solve this problem of TRNGs. The proposed post-processing is applied in real time to the ring oscillator-based TRNG in two different scenarios on the Altera Cyclone IV GX Field-Programmable Gate Array chip. Bias, correlation, entropy, Chi-square, Berlekamp–Massey and National Institute of Standards and Technology Special Publication 800–22 test techniques are used for statistical verification of real-time results. In addition, for the proposed method, the area–energy consumption parameters of TRNG are examined and a detailed literature (performance) comparison has been made. The acquired results indicate that the proposed method can overcome the statistical weakness problem of TRNGs by providing better trade-off than the methods in the literature. In addition, it has been observed that the performance of TRNG is high due to the advantages of the method such as simplicity, low area–energy requirement and high output bit rate. Performance and statistical analysis results confirm the cryptographic suitability of the proposed method and that TRNG can be used successfully in lightweight architecture and applications.

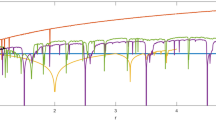

source of TRNG

Similar content being viewed by others

References

L. Gong, J. Zhang, H. Liu, L. Sang, Y. Wang, True random number generators using electrical noise. IEEE Access 7, 125796–125805 (2019)

Ç. Koç, About Cryptographic Engineering (Springer, Boston, MA, 2009)

A.M. Gari̇pcan, E. Erdem, Design, FPGA implementation and statistical analysis of a high-speed and low-area TRNG based on an AES S-box post-processing technique. ISA Transactions (2021)

V. Fischer, A closer look at security in random number generators design. Lecture Notes in Computer Science, pp. 167–182, 2012 (2012). Doi: https://doi.org/10.1007/978-3-642-29912-4_13

D. Rushchen, M. Schrey, J. Freese, I. Heisterklaus, Generation of true random numbers based on radioactive decay. In Proceedings of the International Student Scientific Conference Poster—21/2017. Prague (Czech Republic), pp. 1–4 (2017)

B. Jun, P. Kocher, The Intel random number generator. Cryptograph Research Inc., White Paper, vol. 27, pp. 1–8 (1999)

B. Sunar, W.J. Martin, D.R. Stinson, A provably secure true random number generator with built-in tolerance to active attacks. IEEE Trans. Comput. 56, 109–119 (2007)

K. Wold, C.H. Tan, Analysis and enhancement of random number generator in FPGA based on oscillator rings. Int. J. Reconfigurable Comput. 2009, 385–390 (2009)

D. Lambić, A. Janković, M. Ahmad, Security analysis of the efficient chaos pseudo-random number generator applied to video encryption. J. Electron. Test. 34(6), 709–715 (2018)

İ. Koyuncu, M. Tuna, İ. Pehlivan, C.B. Fidan, M. Alçın, Design, FPGA implementation and statistical analysis of chaos-ring based dual entropy core true random number generator. Analog Integrated Circuits and Signal Processing, pp. 1–12 (2019)

M. Tuna, A. Karthikeyan, K. Rajagopal, M. Alcin, İ Koyuncu, Hyperjerk multiscroll oscillators with megastability: analysis, FPGA implementation and a novel ANN-ring-based true random number generator. AEU-Int. J. Electron. Commun. 112, 152941 (2019)

M. Ahmad, M.N. Doja, M.M.S. Beg, Security analysis and enhancements of an image cryptosystem based on hyperchaotic system. J. King Saud Univ.-Comput. Inf. Sci. 33(1), 77–85 (2021)

H. Hata, S. Ichikawa, FPGA implementation of metastability-based true random number generator. IEICE Trans. Inf. Syst. 95(2), 426–436 (2013)

P.S. Meka, R. Sivaraman, A. Rengarajan, S. Rajagopalan, Metastability Influenced PUF for cryptographic key generation: a FPGA Approach. In 2020 International conference on computer communication and informatics (pp. 1–6) (2020)

M. Stipčević, Ç.K. Koç, True random number generators, in Open Problems in Mathematics and Computational Science. (Springer, Cham, 2014), pp. 275–315

E. Avaroğlu, T. Tuncer, A.B. Özer, B. Ergen, M. Türk, A novel chaos-based post-processing for TRNG. Nonlinear Dyn. 81(1–2), 189–199 (2015)

F. Özkaynak, Cryptographically secure random number generator with chaotic additional input. Nonlinear Dyn. 78(3), 2015–2020 (2014)

S. Toprak, A. Akbulut, M.A. Aydın, A.H. Zaim, LWE: An energy-efficient lightweight encryption algorithm for medical sensors and IoT devices. Electrica 20(1), 71–81 (2020)

K. McKay, L. Bassham, M. Sönmez Turan, N. Mouha, Report on lightweight cryptography. Draft NIST Internal or Interagency Report (NISTIR) 8114, Tech. Rep., National Institute of Standards and Technology, August 2016 (2016)

V. Rožić, I. Verbauwhede, Hardware-efficient post-processing architectures for true random number generators. IEEE Trans. Circuits Syst. II Express Briefs 66(7), 1242–1246 (2018)

K. Marton, A. Suciu, I. Ignat, Randomness in digital cryptography: a survey. Romanian J. Inf. Sci. Technol. 13(3), 219–240 (2018)

R.B. Davies, Exclusive OR (XOR) and hardware random number generators. March 07, 2021, Available at http://www.robertnz.net/pdsf/xor2.pdf

B. Karakaya, A. Gülten, M. Frasca, A true random bit generator based on a memristive chaotic circuit: analysis, design and FPGA implementation. Chaos Solitons Fractals 119, 143–149 (2019)

M. Dichtl, Bad and good ways of post-processing biased physical random numbers. In Fast Software Encryption workshop—FSE, 4593: 127–152 (2007)

A.M. Garipcan, E. Erdem, Hardware implementation of chaotic zigzag map based bitwise dynamical PRNG on FPGA. Informacije MIDEM 50(4), 243–254 (2021)

S. Nikolic, M. Veinovic, Advancement of true random number generators based on sound cards through utilization of a new post-processing method. Wireless Pers. Commun. 91(2), 603–622 (2016)

J. Von Neumann, various techniques used in connection with random digits. National Bureau Stand. Appl. Math. Series 12, 36–38 (1951)

R. Zhang, S. Chen, C. Wan, H. Shinohara, High-throughput Von Neumann post-processing for random number generator. In 2018 International Symposium on VLSI Design, Automation and Test (VLSI-DAT) IEEE, pp. 1–4 (2018)

V. Rožić, B. Yang, W. Dehaene, & I. Verbauwhede, Iterating von Neumann's post-processing under hardware constraints. In 2016 IEEE international symposium on hardware oriented security and trust (HOST), pp. 37–42 (2016)

A. Degada, H. Thapliyal, An integrated TRNG-PUF architecture based on photovoltaic solar cells. IEEE Consumer Electr. Magazine (2020). https://doi.org/10.1109/MCE.2020.3019762

D. Schellekens, B. Preneel, I. Verbauwhede, FPGA vendor agnostic true random number generator. In: Proc. 16th Int. Conf. Field Programmable Logic and Applications—FPL, pp. 1–6 (2006)

J.D. Golic, New methods for digital generation and postprocessing of random data. IEEE Trans. Comput. 55(10), 1217–1229 (2006)

R. Sivaraman, S. Rajagopalan, A. Sridevi, J.B.B. Rayappan, M.P.V. Annamalai, A. Rengarajan, Metastability-induced TRNG architecture on FPGA. Iranian J. Sci. Technol. Trans. Electr. Eng. 44(1), 47–57 (2020)

M. Dichtl, How to predict the output of a hardware random number generator, in International Workshop on Cryptographic Hardware and Embedded Systems. (Springer, Berlin, Heidelberg, 2003), pp. 181–188

V. Rožić, I. Verbauwhede, Hardware-efficient post-processing architectures for true random number generators. IEEE Trans. Circuits Syst. II Express Briefs 66(7), 1242–1246 (2018)

S. Łoza, & Ł. Matuszewski, A true random number generator using ring oscillators and SHA-256 as post-processing. In 2014 International Conference on Signals and Electronic Systems (ICSES) IEEE, pp. 1–4 (2014)

S. Yakut, T. Tuncer, A.B. Ozer, Secure and efficient hybrid random number generator based on sponge constructions for cryptographic applications. Elektronika ir Elektrotechnika 25(4), 40–46 (2019)

K. Márton, L. Pârvu, A. Suciu, The Impact of Post-processing Functions on Random Number Sequences. In 2018 17th RoEduNet Conference: Networking in Education and Research (RoEduNet) IEE pp. 1–6 (2018)

V.B. Suresh, W.P. Burleson, Entropy and energy bounds for metastability based TRNG with lightweight post-processing. IEEE Trans. Circuits Syst. I Regul. Pap. 62(7), 1785–1793 (2015)

V. Fischer, F. Bernard, & N. Bochard, Modern random number generator design–Case study on a secured PLL-based TRNG, it-Information Technology, cilt 61(1), ss. 3–13 (2019)

A.M. Garipcan, E. Erdem, A TRNG using chaotic entropy pool as a post-processing technique: analysis, design and FPGA implementation. Analog Integr. Circ. Sig. Process 103(3), 1–20 (2020)

J.S. Teh, W. Teng, A. Samsudin, J. Chen, A post-processing method for true random number generators based on hyperchaos with applications in audio-based generators. Front. Comp. Sci. 14(6), 1–11 (2020)

J.J.M. Chan, P. Thulasiraman, G. Thomas, R. Thulasiram, Ensuring quality of random numbers from TRNG design and evaluation of post-processing using genetic algorithm. J. Comput. Commun. 4(4), 73–92 (2016)

J. Cartagena, H. Gomez, & E. Roa, A fully-synthesized TRNG with lightweight cellular-automata based post-processing stage in 130nm CMOS. In 2016 IEEE Nordic Circuits and Systems Conference (NORCAS) (pp. 1–5). IEEE (2016)

V. Fischer, M. Deutschmann, S. Lattacher, G. Battum, Report on Selected TRNG and PUF Principles. HECTOR Project Technichal Report D2.1, Université Jean Monnet (UJM) (2016)

F. Özkaynak, Construction of robust substitution boxes based on chaotic systems. Neural Comput. Appl. 31(8), 3317–3326 (2019)

M.P.S. dos Santos, J.A.F. Ferreira, Novel intelligent real-time position tracking system using FPGA and fuzzy logic. ISA Trans. 53(2), 402–414 (2014)

A. Rukhin, J. Soto, J. Nechvatal, M. Smid, D. Banks, A statistical test suite for random and pseudorandom number generators for statistical applications. NIST Special Publication in Computer Security (2001)

A.J. Menezes, P.C. Oorschot, S.A. Vanstone, Handbook of Applied Cryptography (CRC Press, Boca Raton, FL, USA, 1996)

P.W. Kohlbrenner, The design and analysis of a true random number generator in a field programmable gate array. Doctoral dissertation, George Mason University (GMU) (2003)

A.M. Garipcan, E. Erdem, Implementation and performance analysis of true random number generator on FPGA environment by using non-periodic chaotic signals obtained from chaotic maps. Arab. J. Sci. Eng. 44(11), 9427–9441 (2019)

M. Ahmad, , Farooq, O. (2011). Chaos based PN sequence generator for cryptographic applications. In 2011 International Conference on Multimedia, Signal Processing and Communication Technologies (pp. 83–86). IEEE

T.L. Liao, P.Y. Wan, J.J. Yan, Design and synchronization of chaos-based true random number generators and its FPGA implementation. IEEE Access (2022)

A.M. Garipcan, E. Erdem, Implementation of a digital TRNG using jitter based multiple entropy source on FPGA. Informacije MIDEM 49(2), 79–90 (2019)

S. Rethinam, S. Rajagopalan, S. Janakiraman, S. Arumugham, R. Amirtharaian, Jitters through dual clocks: an effective Entropy Source for True Random Number Generation. In 2018 International Conference on Computer Communication and Informatics (ICCCI), pp. 1–5 (2018)

J.-L. Danger, S. Guilleya, P. Hoogvorsta, High speed true random number generator based on open loop structures in FPGAs. Microelectron. J. 40(11), 1650–1656 (2009)

I. Koyuncu, A.T. Ozcerit, The design and realiza¬tion of a new high speed FPGA-based chaotic true random number generator. Comput. Electr. Eng. 58, 203–214 (2017)

M. Alcin, I. Koyuncu, M. Tuna, M. Varan, I. Pehlivan, A novel high speed artificial neural network–based chaotic true random number generator on field programmable gate array. Int. J. Circuit Theory Appl. 47(3), 365–378 (2019)

G.D.P. Stanchieri, A. De Marcellis, E. Palange, M. Faccio, A true random number generator architecture based on a reduced number of FPGA primitives. AEU-Int. J. Electr. Commun. 105, 15–23 (2019)

A. Cherkaoui, V. Fischer, L. Fesquet, A. Aubert, A very high speed true random number generator with entropy assessment. In International Conference on Cryptographic Hardware and Embedded Systems, pp. 179–196 (2013)

H. Hata, S. Ichikawa, FPGA implementation of metastability-based true random number generator. IEICE Trans. Inf. Syst. 95(2), 426–436 (2012)

P.Z. Wieczorek, An FPGA implementation of the resolve time-based true random number generator with quality control. IEEE Trans. Circuits Syst. I Regul. Pap. 61(12), 3450–3459 (2014)

P.Z. Wieczorek, K. Gołofit, Dual-metastability time-competitive true random number generator. IEEE Trans. Circuits Syst. I Regul. Pap. 61(1), 134–145 (2013)

N.N. Anandakumar, S.K. Sanadhya, M.S. Hashmi, FPGA-based true random number generation using programmable delays in oscillator-rings. IEEE Trans. Circuits Syst. II: Express Briefs 67(3), 570–574 (2019)

R. Sivaraman, S. Rajagopalan, R. Amirtharajan, FPGA based generic RO TRNG architecture for image confusion. Multimedia Tools Appl., pp.1–28 (2020)

Yang X., Cheung R.C.C., A complementary architecture for highspeed true random number generator. In 2014 International Conference on Field-Programmable Technology (FPT), pp. 248–251, IEEE (2014)

X. Wu, S. Li, A new digital true random number generator based on delay chain feedback loop. In 2017 IEEE International Symposium on Circuits and Systems (ISCAS), pp. 1–4 (2017)

Y. Yang, S. Jia, Y. Wang, A reliable true random number generator based on novel chaotic ring oscillator. In 2017 IEEE International Symposium on Circuits and Systems (ISCAS), pp. 1–4, IEEE (2017)

S. Tao, Y. Yu, E. Dubrova, FPGA based true random number generators using non-linear feedback ring oscillators. In 2018 16th IEEE International New Circuits and Systems Conference (NEWCAS) IEEE, pp. 213–216 (2018)

X. Wang, H. Liang, Y. Wang, L. Yao, Y. Guo, M. Yi, Y. Lu, High-throughput portable true random number generator based on jitter-latch structure. IEEE Trans. Circuits Syst. I: Regular Papers (2020)

K. Demir, S. Ergun, Random number generators based on irregular sampling and fibonacci–galois ring oscillators. IEEE Trans. Circuits Syst. II Express Briefs 66(10), 1718–1722 (2019)

A.M. Garipcan, E. Erdem, DESSB-TRNG: a novel true random number generator using data encryption standard substitution box as post-processing. Digital Signal Process. 123, 103455 (2022)

Acknowledgements

Authors are deeply grateful to the editor(s) for smooth and fast handling of the manuscript. The authors would also like to sincerely thank the anonymous reviewer(s) for their valuable contributions to improve the quality of this paper.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Garipcan, A.M., Erdem, E. A gigabit TRNG with novel lightweight post-processing method for cryptographic applications. Eur. Phys. J. Plus 137, 493 (2022). https://doi.org/10.1140/epjp/s13360-022-02679-7

Received:

Accepted:

Published:

DOI: https://doi.org/10.1140/epjp/s13360-022-02679-7