Abstract

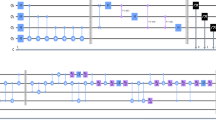

This paper presents a new simple and straightforward method for designing Completely Testable Embedded (CTE) parity trees, and Self-Testing Embedded (STE) two-rail checkers. In the design of CTE parity trees the two inputs XOR gate has been used as the building block. In the case of STE two-rail checkers with n input pairs the building block is the two-rail checker with 2 input pairs. During normal, fault free, operation each XOR gate receives all possible input vectors, while each two-rail checker with 2 input pairs receives all possible code input vectors. The great advantage of the proposed method is that it is the only one that gives in a simple and straightforward way an optimal CTE/STE tree realization with respect to the hardware (number of blocks) and the speed (number of block levels). Designing the two input two-rail checker as proposed by Lo in IEEE J. of Solid-State Circuits, 1993, we get optimal STE two-rail checkers taking into account realistic faults.

Similar content being viewed by others

References

G.P. Aksenova, “Necessary and Sufficient Conditions for the Synthesis of Completely Testable Modulo 2 Convolution Circuits,” Autom. I Telemek., No. 9, pp. 126–135, Sept. 1979.

J. Khakbaz and F.J. McCluskey, “Self-Testing Embedded Checkers,” Center for Reliable Comp., Stanford Univ., Stanford, CA, CFC Tech., Feb.–Dec. 1983.

F.J. McCluskey, “Design Techniques for Testable Embedded Error Checkers,” IEEE Comp. Mag., pp. 84–88, July 1990.

J. Khakbaz, “Self-Testing Embedded Parity Trees,” Dig. of FTCS-12, pp. 109–116, June 1982.

J. Khakbaz and F.J. McCluskey, “Self-Testing Embedded Code Checkers,” Dig. Spring 1983 COMPCON, San Francisco, CA, Feb.–March 1983, pp. 452–457.

J. Khakbaz and F.J. McCluskey, “Self-Testing Embedded Parity Checkers,” IEEE Tran. on Computers, Vol. C-33, No. 8, pp. 753–756, Aug. 1984.

D.K. Pradhan, Fault-Tolerant Computer System Design, NJ Prentice-Hall, 1996.

E. Fujiwara and K. Matsuoka, “A Self-Checking Generalized Prediction Checkers and Its Use for Built-In Testing,” IEEE Trans. Comput., Vol. C-36, pp. 86–93, Jan. 1987.

S. Kundu and S.M. Reddy, “Embedded Totally Self-Checking Checkers: A Practical Design,” IEEE Design & Test of Comp., pp. 5–12, Aug. 1990.

S. Tarnick, “Embedded Parity and Two-Rail TSC Checkers with Error-Memorizing Capability,” 1st Online Testing Workshop, Nice, France, July 1995, pp. 221–225.

C. Metra, M. Favalli, and B. Ricco, “Embedded Two-Rail Checkers with On-Line Testing Ability,” 14th IEEE VLSI Test Symposium, pp. 145–150, April–May, 1996.

S. Kundu, E.S. Sogomonyan, M. Goessel, and S. Tarnick, “ Self-Checking Comparator with One Periodic Output,” IEEE Trans. on Comp., Vol. 45, No. 3, pp. 379–380, March 1996.

A.M. Usas, “A Totally Self-Checking Checker Design for the Detection of Errors in Periodic Signals,” IEEE Trans. Comput., Vol. C-24, No. 5, pp. 483–488, May 1975.

H.T. Nagle et al., “Design for Testability and Built-Self Test: A Review,” IEEE Trans. Industrial Electronics, Vol. 36, No. 2, pp. 129–140, May 1989.

D. Nikolos, “Design of Self-Testing Embedded Parity Checkers Using Two-input XOR Gates,” Proc. of XII Int. Conf. Fault-Tolerant Systems and Diagnostics, Praha, Czechoslovakia, Sept. 1989, pp. 158–162.

M. Nicolaidis, “Fault Secure Property Versus Strongly code Disjoint Checkers,” IEEE Trans. on CAD, Vol. 13, No. 5, pp. 651–658, May 1994.

W.C. Carter and P.F. Schneider, “Design of Dynamically Checked Computers,” Proc. 4th Cong. IFIP, Edinburgh, Scotland, Aug. 1968, Vol. 2, pp. 878–883.

D.A. Anderson, “Design of Self-Checking Networks Using Coding Techniques,” Coord. Sci. Lab., Univ. Illinois, Urbana, IL, Tech. Rep. R-527, 1971.

F. Ozguner, “Design of Totally Self-Checking Embedded Two Rail Code Checkers,” Electronics Lett., Vol. 27, No. 4, pp. 382– 384, Feb. 1991.

D.C. Bossen, D.L. Opstako, and A.M. Patel, “Optimum Test Patterns for Parity Networks,” Proc. AFIPS 1970 Fall Joint Comput. Conf., Houston, TX, Nov. 1970, Vol. 37, pp. 63– 68.

D. Nikolos, “Optimal Self-Testing Embedded Two-Rail Checkers,” CTI, Technical Report No. 96.5.15, 1996.

S.L. Wang and A. Avizienis, “The Design of Totally Self-Checking Circuits Using Programmable Logic Arrays,” Proc. FTCS-9, June 1979, pp. 173–180.

Y. Tamir and C.H. Sequin, “Design and Application of Self-Testing Comparators Implemented with MOS PLA's,” IEEE Trans. Comput., Vol. C-33, pp. 493–506, June 1984.

D. Nikolos “Design of Totally Self-Checking Comparators for Classes of n k-bit Vectors,” Proc. of VIII Int. Conference on Fault-Tolerant Systems and Diagnostics, Katowice, Poland, Sept. 1985, pp. 203–208.

Y. Min and J. Li, “Strongly Fault Secure PLAs and TSC Checkers,” IEEE Trans. Comp., pp. 863–867, July 1988.

J.C. Lo, “A Novel Area-Time Efficient Static CMOS Totally Self-Checking Comparator,” IEEE Journal of Solid-State Circuits, Vol. 28, No. 2, pp. 165–168, Feb. 1993.

Author information

Authors and Affiliations

Rights and permissions

About this article

Cite this article

Nikolos, D. Self-Testing Embedded Two-Rail Checkers. Journal of Electronic Testing 12, 69–79 (1998). https://doi.org/10.1023/A:1008281822966

Issue Date:

DOI: https://doi.org/10.1023/A:1008281822966