Abstract

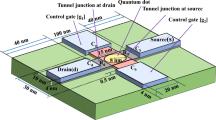

Temperature, doping concentration, and gate work function all have a significant impact on performance of transistor during miniaturization. The design and in-depth investigation of a 10 nm gate length n-channel tri-gate junction less Fin Field Effect Transistor with respect to variation of temperature, doping level, and gate material work function through extensive simulation by incorporating quantum transport model constitute the innovative aspects of the current work. TCAD is used to model the intended device under various AC and DC biasing scenarios. The DC study results at temperature of 300 K, gate work function of 5.2 eV and doping concentration of 1019 cm− 3 demonstrate subthreshold swing of 80 mV/dec, high ON state current (ION) to OFF state current (IOFF) ratio 1.7 × 1011 and low DIBL of 12.8 mV/V. Based on these performance parameters, the devices demonstrate potential use for low power switching operations at lower dimensions.

Similar content being viewed by others

References

G. Deepti, S. Balraj, K.T. Pramod, Subthreshold modeling of Tri-gate Junctionless transistors with Variable Channel edges and substrate Bias effects. IEEE Trans. Electron. Devices. 65(5), 1663–1671 (2018)

C.W. Lee, I. Ferain, A. Kranti, N. Dehdashti Akhavan, P. Razavi, R. Yan, R. Yu, B. O’Neill, A. Blake, M. White, A.M. Kelleher, B. McCarthy, S. Gheorghe, R. Murphy, J.P. Colinge, Short-channel junctionless nanowire transistors, International Conference of Solid State Devices Mater (SSDM), Tokyo, Japan, pp. 1044–1045, 2010

J.P. Colinge, Nanowire transistors without junctions. Nat. Nanotechnol. 5(3), 225–229 (2010)

S. Tayal, A. Nandi, Analog/RF performance analysis of channel engineered high-K gate-stack based Junctionless Trigate-FinFET. Superlattices Microstruct. 112, 287–295 (2017)

A. Breed, K.P. Roenker, Dual-gate (FinFET) and tri-Gate MOSFETs: simulation and design, International Semiconductor Device Research Symposium, pp. 150–151, 2003

D. Nagy, G. Indalecio, A.J. GarcíA-Loureiro, M.A. Elmessary, K. Kalna, N. Seoane, FinFET Versus Gate-All-around Nanowire FET: performance, scaling, and variability. IEEE J. Electron. Devices Soc. 6, 332–340 (2018)

J. Patel et al., Design optimization Using Symmetric/Asymmetric Spacer for 14 nm multi-Fin Tri-gate Fin-FET for Mid-Band 5G Applications, 35th International Conference on VLSI Design, pp. 292–296, 2022

V.B. Sreenivasulu, V. Narendar, A Comprehensive Analysis of Junctionless Tri-Gate (TG) FinFET towards Low-Power and High-Frequency Applications at 5-nm Gate Length, Silicon, vol. 14, pp. 2009–2021, 2022

A. Es-Sakhi, M. Chowdhury, Analysis of device capacitance and subthreshold behaviour of tri-gate SOI FinFET. Microelectron. J. 62, 30–37 (2017)

R. Das, R. Goswami, S. Baishya, Tri-gate heterojunction SOI Ge-FinFETs, Superlattices and Microstructures, vol. 91, pp. 51–61, 2016

S. Gupta, A. Nandi, Effect of air spacer on analog performance of underlap trigate FinFET. Superlattices Microstruct. 109, 693–701 (2017)

B.S. Doyle, S. Datta, M. Doczy, S. Hareland, B. Jin, J. Kavalieros, T. Linton, A. Murthy, R. Rios, R. Chau, High performance fully-depleted Tri-gate CMOS transistors. IEEE Electron Device Lett. 24(4), 263–265 (2003)

P. Vijaya, R. Lorenzo, Improvement of Ion, Electric Field and Transconductance of TriGate FinFET by 5nm Technology, Silicon, 14, pp. 7889–7900, 2022

Q. Memon, S. Rehman, M.A. Bashir, N.M. Memon, M.A. Haq, S. Alharby, A. Alhussen, A.U. Rehman, An efficient technique to simulate the AC/DC parameters of Trigate FinFETs. IEEE Access. 12, 14238–14247 (2024)

S.C. Sun, J.D. Plummer, Electron mobility in inversion and accumulation layers on thermally oxidized silicon surfaces, in IEEE Transactions on Electron Devices, vol. 27, no. 8, pp. 1497–1508, Aug. 1980, https://doi.org/10.1109/T-ED.1980.20063

R. Rios, A. Cappellani, M. Armstrong, A. Budrevich, H. Gomez, R. Pai, N. Rahhal-orabi, Kuhn comparison of junctionless and conventional trigate transistors with Lg down to 26 nm. IEEE Electron Device Lett. 32(9), 1170–1172 (2011)

E. Datta, A. Chattopadhyay, A. Mallik, Relative study of analog performance, linearity, and harmonic distortion between Junctionless and conventional SOI FinFET at elevated temperatures. J. Electron. Mater. 49, 3309–3316 (2020)

R. Yuvaraj, A. Karuppannan, A.K. Panigrahy, R. Swain, Design and analysis of Gate Stack Silicon-on-insulator Nanosheet FET for Low Power Applications. Silicon. 15, 1739–1746 (2022)

G. Ghibaudo, M. Aouad, M. Casse, S. Martinie, T. Poiroux, F. Balestra, On the modelling of temperature dependence of subthreshold swing in MOSFETs down to cryogenic temperature. Solid State Electron. 170, 0038–1101 (2020). https://doi.org/10.1016/j.sse.2020.107820

R. Saha, B. Bhowmick, S. Baishya, Temperature effect on RF/analog and linearity parameters in DMG FinFET. Appl. Phys. A 124, 642 (2018). https://doi.org/10.1007/s00339-018-2068-5

S.K. Mohapatra, K.P. Pradhan, P.K. Sahu, Temperature dependence inflection point in Ultra-thin Si directly on insulator (SDOI) MOSFETs: an influence to key performance metrics. Superlattices Microstruct. 78, 134–143 (2015). https://doi.org/10.1016/j.spmi.2014.11.037

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher’s Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Panda, S., Parida, R.S., Dora, G.C. et al. Effect of Temperature, Doping and Gate Material Engineering on Tri-Gate SOI nFinFET Performance Through TCAD Simulation. Trans. Electr. Electron. Mater. (2024). https://doi.org/10.1007/s42341-024-00543-2

Received:

Revised:

Accepted:

Published:

DOI: https://doi.org/10.1007/s42341-024-00543-2