Highlights

-

The review provides a comprehensive summary of performance limits of the single two-dimensional transition metal dichalcogenide (2D-TMD) transistor.

-

The review details the two logical expressions of the single 2D-TMD logic transistor, including current and voltage.

-

The review demonstrates the two calculating methods for dynamic energy consumption of 2D synaptic devices.

Abstract

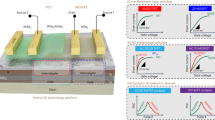

Two-dimensional (2D) transition metal dichalcogenides (TMDs) allow for atomic-scale manipulation, challenging the conventional limitations of semiconductor materials. This capability may overcome the short-channel effect, sparking significant advancements in electronic devices that utilize 2D TMDs. Exploring the dimension and performance limits of transistors based on 2D TMDs has gained substantial importance. This review provides a comprehensive investigation into these limits of the single 2D-TMD transistor. It delves into the impacts of miniaturization, including the reduction of channel length, gate length, source/drain contact length, and dielectric thickness on transistor operation and performance. In addition, this review provides a detailed analysis of performance parameters such as source/drain contact resistance, subthreshold swing, hysteresis loop, carrier mobility, on/off ratio, and the development of p-type and single logic transistors. This review details the two logical expressions of the single 2D-TMD logic transistor, including current and voltage. It also emphasizes the role of 2D TMD-based transistors as memory devices, focusing on enhancing memory operation speed, endurance, data retention, and extinction ratio, as well as reducing energy consumption in memory devices functioning as artificial synapses. This review demonstrates the two calculating methods for dynamic energy consumption of 2D synaptic devices. This review not only summarizes the current state of the art in this field but also highlights potential future research directions and applications. It underscores the anticipated challenges, opportunities, and potential solutions in navigating the dimension and performance boundaries of 2D transistors.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

Transistor technology has been instrumental in driving the progress of contemporary electronics. From the invention of the first point-contact transistor in 1947 to the evolution of silicon-based MOSFETs, this technology has consistently evolved to meet the escalating demand for more compact, speedier, and energy-efficient devices. In the past decade, a novel class of materials, known as two-dimensional (2D) transition metal dichalcogenides (TMDs), has emerged as a promising candidate for future-generation transistors [1,2,3,4,5]. The evolution and significance of transistors based on 2D TMDs have become intriguing topics in recent years, owing to their unique properties and potential applications across various disciplines [6]. TMDs, encompassing molybdenum disulfide (MoS2), molybdenum telluride (MoTe2), and tungsten diselenide (WSe2), possess a layered structure, paving the way for atomic scale transistor development, a considerable advancement from traditional semiconductor materials [7, 8]. Furthermore, the non-zero bandgap of TMDs make them particularly suited for applications in the semiconductor industry, where device miniaturization and performance enhancement are paramount. 2D monolayer TMDs also possess a direct bandgap, which is beneficial for optoelectronic applications [9]. Their mechanical flexibility and chemical stability open avenues for flexible and wearable electronics [10,11,12,13]. The thin nature of 2D TMDs permits the creation of van der Waals heterostructures by stacking varying 2D materials, thus enabling the design of devices with tailor-made properties [14,15,16]. Nevertheless, realizing the potential of 2D TMDs in transistor technology still exists challenges. Issues such as contact resistance, variability, and material quality must be addressed to fully capitalize on their benefits [17, 18].

TMDs, with their unique properties and the possibility of manipulating dimensions at the atomic scale, unlock novel opportunities for fabricating ultrascaled, high-performance devices. While the journey of 2D TMDs-based transistors is just beginning, their potential to drive the next revolution in electronics is undeniable. The exploration of these materials holds significance not only for the evolution of transistor technology, but also for the wider field of nanotechnology.

1.1 The Limitations of Traditional Semiconductor Materials and the Potential of 2D TMDs to Address These

Traditional semiconductor materials, most notably silicon (Si), have been the bedrock of contemporary electronics. However, as the industry strives for device performance enhancement and size reduction, several inherent limitations of these materials have surfaced [19] (Fig. 1). A significant challenge is the short-channel effect, which arises when the channel length of the transistor is diminished. As this length decreases, the control over current flow is compromised, leading to increased leakage current, power dissipation, and diminished reliability. Another constraint is Si's indirect bandgap, which hinders its application in optoelectronic devices. The indirect bandgap makes efficient light emission challenging, hindering the development of Si-based light-emitting diodes or lasers. Furthermore, Si's mechanical rigidity limits its applicability in flexible electronics. The burgeoning demand for wearable and flexible devices necessitates the introduction of new materials that can endure mechanical strain [20].

The limitations of traditional semiconductor materials and the merits of 2D TMDs for high performance electronic device. The diagram of flexible 2D FETs. Reproduced with permission. Reference [10] Copyright 2022, Springer Nature

2D TMDs offer promising solutions to these constraints (Fig. 1). The emergence of 2D materials has spurred a revolution in nanoelectronics over the past decade. These materials hold tremendous potential for the advancement of next-generation semiconductor devices [21]. Due to their atomic thickness, 2D TMDs provide superior control over the channel, potentially mitigating the short-channel effects and facilitating further device miniaturization [1, 8]. Unlike Si, many 2D monolayer TMDs, such as MoS2 and WSe2, possess a direct bandgap, making them suitable for optoelectronic applications [9]. Moreover, 2D TMDs exhibit exceptional mechanical flexibility, rendering them promising candidates for the upcoming generation of flexible and wearable electronics [10,11,12, 22]. The capability of 2D TMDs to endure mechanical deformation without losing their electronic properties gives them a significant advantage over traditional semiconductors. Additionally, machine learning-based predictive models have been employed to predict 2D materials' properties, including magnetic ordering, bandgap properties, and point defect designs. This allows for the screening and determination of optimal synthesis mechanisms for such materials [23].

As a result, 2D TMDs offer a promising path to circumvent the limitations of traditional semiconductor materials. Their unique properties and the possibility to manipulate dimensions at an atomic scale offer new opportunities for the development of the next generation of ultra-scaled high-performance devices. Despite these promising characteristics, the implementation of 2D TMDs in transistors comes with its own set of challenges, including material synthesis, device fabrication, and the control of electrical properties [18, 24]. However, ongoing research and technological advancements are progressively pushing the boundaries, paving the way for the realization of 2D TMD-based transistors.

1.2 The Relevance of Dimension and Performance Constraints in the Context of Technological Progress

The significance of dimension and performance constraints in the context of technological progress is a crucial area of research in the electronics and optoelectronics field. The relentless push for technological advancement in the electronics industry has been guided by Moore's Law [25]. This principle has driven the miniaturization of transistors, a vital factor in developing faster, more powerful, and more energy-efficient devices. As the size of transistors nears the atomic scale, dimension and performance constraints have increasingly emerged as significant challenges [26]. The miniaturization process is beginning to confront physical limitations such as quantum effects, increased leakage current, power dissipation, and reduced reliability due to short-channel effects.

The dimension constraint refers to the physical limits of device miniaturization, such as channel length, gate length, source/drain contact length, and dielectric thickness (Fig. 2), which influence their performance. The continuous reduction of transistor dimensions has reached a point where further shrinkage could disrupt the device's structural integrity and operational functionality. For example, reducing the channel length can enhance the speed of the transistor, but may also increase leakage current, leading to higher power consumption. Similarly, reducing the gate length can improve the transistor’s switching speed but may increase the risk of short-channel effects, which can degrade the device’s performance. The performance constraint involves maintaining or enhancing the device's operational efficiency, speed, and power consumption as its size is reduced. This is a major challenge as traditional semiconductor materials like silicon struggle to maintain their performance when scaled down to a few nanometers [19]. Performance constraints such as source/drain contact resistance, subthreshold swing, hysteresis loop, carrier mobility, and on/off ratio also significantly impact the overall performance of the transistor (Fig. 2). For example, reducing the source/drain contact resistance can enhance the transistor's current drive capability, while reducing the subthreshold swing can improve the transistor’s energy efficiency.

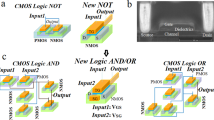

Demonstration of dimension and performance limits in 2D TMD transistors. Channel length diagram. Reproduced with permission. Reference [27] Copyright 2021, Springer Nature. Gate length diagram. Reproduced with permission. Reference [28] Copyright 2022, Springer Nature. Contact length diagram. Reproduced with permission. Reference [29] Copyright 2023, Springer Nature. Dielectric thickness diagram. Reproduced with permission. Reference [30] Copyright 2022, Springer Nature. Contact resistance diagram. Reproduced with permission. Reference [31] Copyright 2023, Springer Nature. Subthreshold swing diagram. Reproduced with permission. Reference [32] Copyright 2021, Springer Nature. Hysteresis loop diagram. Reproduced with permission. Reference [33] Copyright 2023, American Chemical Society. Carrier mobility diagram. Reproduced with permission. Reference [34] Copyright 2023, American Chemical Society. On/Off ratio diagram. Reproduced with permission. Reference [35] Copyright 2023, Springer Nature. P-type transistor diagram. Reproduced with permission. Reference [36] Copyright 2022, Wiley–VCH Verlag. Single-logic transistor diagram. Reproduced with permission. Reference [37] Copyright 2021, Springer Nature. Memory device diagram. Reproduced with permission. Reference [38] Copyright 2021, Springer Nature

In terms of technological progress, overcoming these dimension and performance constraints is essential for developing next-generation electronic devices. For example, 2D TMD-based transistors demonstrate great potential in overcoming these constraints due to their unique properties such as tunable bandgap and high carrier mobility [1]. Their atomic-scale thickness allows for excellent electrostatic control, which could alleviate short-channel effects and enable further device miniaturization [8]. Furthermore, the direct bandgap and high on/off current ratio properties of 2D monolayer TMDs offer promising performance characteristics that could enhance device function [9]. However, there are still many challenges to be addressed, such as high contact resistance and the presence of traps in the 2D TMDs, which can degrade the device’s performance. Therefore, further research is needed to fully understand and overcome these challenges [18]. In conclusion, addressing these dimension and performance constraints is a critical area of study that can pave the way for next-generation electronic devices development and is essential to sustain the technological progress that society has become accustomed to. The exploration of novel materials like 2D TMDs is an integral part of this journey, marking a significant shift in the landscape of semiconductor technology [24].

1.3 Outline of the Review’s Scope, Objectives, and Structure

This review aims to offer a comprehensive overview of the present state of research and development within the field of 2D TMD-based transistors. The aim is to delve into the implications of 2D TMDs on transistor dimensionality and performance, providing a profound understanding of these topics and contributing to the ongoing discourse around the future of semiconductor technology. The scope of the review encompasses a thorough examination of the dimensional limits of transistors based on 2D TMDs, including channel length miniaturization, gate length reduction, source/drain contact length minimization, and dielectric thickness reduction. This review will also explore the performance limits of these transistors, focusing on aspects such as the reduction of source/drain contact resistance, subthreshold swing reduction, hysteresis loop reduction, carrier mobility enhancement, on/off ratio enhancement, and the realization of p-type and single logic transistors, and memory devices. As part of the exploration of the dimension and performance limits of transistors utilizing 2D TMDs, strategies in traditional semiconductor transistors and those in 2D transistors will be compared to highlight the advantages of 2D TMDs.

The structure of the review will be methodological and systematic, divided into six main sections. The introduction provides a brief overview of the evolution and significance of transistors based on 2D TMDs and outlines the scope, objectives, and structure of the review. Subsequent sections delve into understanding 2D TMDs, exploring the dimensional and performance limits of transistors based on 2D TMDs, the role and significance of p-type and single-logic transistors, and the specific challenges and opportunities associated with using 2D TMDs for memory devices. The review concludes with a summary of the key points discussed and an outlook on future prospects and potential directions in the field of 2D transistors. The objective of this review is to help readers gain a comprehensive understanding of the current state of research in the field of 2D TMD-based transistors, the challenges and opportunities associated with their dimensional and performance limits, and the potential impact of overcoming these limits on future technological advancements.

2 Two-Dimensional TMDs and Their Implications for Dimensionality of Electronic Devices

2D TMDs have caught the attention of researchers due to their unique layered structure, which carries significant implications for dimensionality. The layered structure of 2D TMDs allows for potential manipulation of dimensions at the atomic scale, facilitating the fabrication of devices with dimensions unreachable with traditional semiconductors [39].

2.1 Unique Layered Structure of 2D TMDs and Its Implications for Dimensionality

As shown in Fig. 3, unlike traditional bulk semiconductors (Fig. 3a), 2D TMDs consist of a single layer of transition metal atoms (Fig. 3b), such as molybdenum or tungsten, sandwiched between two layers of chalcogen atoms, typically sulfur, selenium, or tellurium [40]. The layered structure of 2D TMDs is characterized by weak interlayer bonding and strong intralayer bonding, which allows for exfoliating single atomic layers [39] or stacking them together in different configurations [41]. This property is pivotal as it enables the manipulation of these materials at the nanoscale, catering to various applications. The interlayer spacing of TMDs is approximately 6.5 Å, and their stacking order is indicated by the stacking index c [41]. This tunable interlayer coupling is unique to 2D materials and provides immense opportunities to engineer the electronic properties of devices [14]. The thickness of TMDs determines their band structure, which further underscores the layered structure's importance. Unlike graphene with a zero-gap band structure, 2D TMDs present a tunable bandgap, making them more suitable for specific applications.

The unique electrical properties of 2D TMDs result from their reduced dimensionality, which significantly differs from their 3D counterparts. For instance, TMDs can transform from an indirect bandgap to a direct bandgap when reduced down to monolayers [39]. Their direct bandgap, absent in bulk TMDs and silicon, enables efficient light emission and absorption, making them ideal for applications in optoelectronics [9]. Moreover, the thinness of 2D TMDs allows for excellent electrostatic control, crucial for mitigating short-channel effects in field-effect transistors [8]. The 2D nature of TMDs has implications for mechanical flexibility. The van der Waals forces between layers enable them to slide over each other without breaking, making 2D TMDs remarkably flexible and robust. These characteristic paves the way for flexible and wearable electronics [10, 11]. However, the 2D nature of TMDs also presents challenges, such as increased sensitivity to environmental conditions and difficulties in fabrication and integration into devices [18].

As a result, the unique layered structure of 2D TMDs showcases the profound impact of dimensionality on material properties, offering a rich platform for exploring new physics and developing next-generation electronic and optoelectronic devices [42]. Nonetheless, further research is needed to fully exploit these materials' potential and overcome the challenges associated with their manipulation at the atomic scale.

2.2 Layered Structure Allowing for Potential Manipulation of Dimensions at Atomic Scale

Control over thickness has significant implications for the electronic properties of 2D TMDs, as it allows for tuning the bandgap and other vital electronic parameters [9]. The weak van der Waals forces in 2D TMDs also enable flexibility in stacking these materials. Different layers can be arranged in various sequences and orientations to form van der Waals heterostructures [41]. These heterostructures provide a new degree of freedom in designing electronic and optoelectronic devices, as they allow for the combination of materials with different electronic properties in a single device [15]. Additionally, the weak interlayer forces enable mechanical exfoliation or layer transfer techniques, allowing the construction of complex heterostructures and superlattices with atomic precision [43]. This capacity to engineer and manipulate the dimensions of 2D TMDs at the atomic scale introduces new possibilities for fabricating desired nanoscale devices [1].

Furthermore, atomic-scale structural modification of 2D TMDs can be achieved through various strategies like direct introduction during synthesis, post-treatment, chemical potential control, lattice plane control, molecular assembly, and anisotropic etching [44]. These modifications can lead to changes in the atomic-scale structures of materials, including edge structures, atomic defects [45], grain boundaries [46]. These modifications can result in changes in the electrical properties of 2D materials, essential for nanoscale devices [44].

However, manipulating dimensions at the atomic scale still presents significant challenges, such as the need for precise control over material synthesis and device fabrication processes [18]. Furthermore, the as-obtained 2D materials during fabrication and post-treatment may lead to possible unexpected phase transitions or reductions in their crystallinity, degrading the performance of 2D devices [44].

Currently, there are two mainstream methods for fabricating monolayer TMDs such as micromechanical exfoliation (Fig. 4a) and chemical vapor deposition methods [47,48,49,50] (Fig. 4b). The layered structure of 2D TMDs enables potential manipulation of dimensions at the atomic scale, opening up exciting possibilities for engineering atomic quantum defects and developing next-generation electronic and optoelectronic devices. Nonetheless, further research is needed to overcome the challenges associated with atomic-scale structural modification and to fully exploit these materials' potential.

3 Dimensional Limits of Transistors

The dimensional parameters of transistors including channel length, gate length, source/drain contact length, and dielectric thickness, which play important role in the electrical characteristics of transistors. The definition of these dimensional parameters in transistors with different structures is presented in Fig. 5.

3.1 Significance of Channel in Transistor Miniaturization

The channel length, defined as the distance between the source and drain of a transistor, significantly impacts the device's performance characteristics. Miniaturizing the channel length is a critical aspect of transistor scaling, which fuels the continuous advancement of semiconductor technology [25]. Reducing the channel length enhances the transistor's switching speed by shortening the distance that carriers must travel. This leads to faster operation and improved device performance [52, 53]. Moreover, miniaturization allows for a higher density of transistors on a chip area, leading to increased computational power and functionality [25]. As channel lengths approach the nanometer scale, several challenges arise due to traditional Si CMOSFETs reaching the miniaturization limit of sub-5 nm technology nodes according to Moore’s Law [1]. Threshold voltage roll-off, drain-induced barrier lowering, and short-channel effects can degrade device performance and increase power consumption [54]. These effects result from the diminishing control of the gate over the channel as the gate length decreases, leading to leakage currents and higher power dissipation [55, 56].

2D TMDs present promising solutions to these challenges. Their atomically thin nature allows for effective gate control even at extremely short channel lengths, mitigating short-channel effects and enabling further miniaturization [1, 39]. The direct bandgap of monolayer TMDs could potentially enable ultra-low power digital and analog circuits [10]. The atomic thickness of 2D TMDs also leads to a reduced scattering rate for carriers, potentially enhancing device performance [57]. The band structure of TMDs, which can transition from an indirect to a direct bandgap in monolayer form, could be beneficial for electronic and optoelectronic applications [58].

Channel length's role in transistor miniaturization is not just about reducing physical size. By manipulating channel length and using novel materials like 2D TMDs, researchers can control transistors' electronic properties, potentially resulting in devices with improved performance, lower power consumption, and greater functionality [36]. The miniaturization of the channel length is a key factor driving transistor scaling and enhancing device performance, 2D TMDs offer promising solutions for further scaling down the channel length for the next generation of nanoscale electronic devices [8, 24]. However, challenges persist in the miniaturization of 2D TMD transistors, including issues related to material synthesis, device fabrication, contact resistance, and environmental stability [59, 60]. Continued research and innovation are required to overcome these challenges and further realize transistor miniaturization using 2D TMDs.

As part of the exploration of the dimension and performance limits of transistors utilizing 2D TMDs, strategies for scaling down the channel length in traditional semiconductor transistors and those in 2D transistors will be compared to highlight the advantages of 2D TMDs.

3.1.1 Channel Length Scaling-Down in Traditional Semiconductor Transistors

In the quest to enhance performance and efficiency, the semiconductor industry has pursued relentless transistor channel length scaling. Recent advancements and methodologies have facilitated this miniaturization, pushing technological boundaries and fueling innovation. A notable advancement is the development of the Fin Field-Effect Transistor (FinFET) design. This design has been instrumental in facilitating transistor scaling into the sub-10 nm regime. Unlike planar transistors, FinFETs boast a three-dimensional structure with a thin "fin" of silicon extending into the device, which provides superior gate control and helps reduce short-channel effects [61]. Further, the employment of advanced lithography techniques, like extreme ultraviolet (EUV) lithography, has allowed for precise patterning of smaller features, thus enabling further miniaturization of the channel length [62].

3.1.2 Channel Length Scaling-Down in Two-dimensional Transistors

Recent advancements in 2D TMDs have opened new avenues for transistor miniaturization (Fig. 6). The atomically thin nature of these materials could potentially mitigate short-channel effects, offering superior gate control even at nanometer channel lengths [1, 21, 63]. Notably, the emergence of monolayer TMD materials like MoS2, WS2, and WSe2 has shown promise in achieving transistors with channel lengths nearing the atomic scale [8], which has been confirmed by theory simulation [64]. Various fabrication methodologies are being studied to effectively scale down 2D TMD transistors.

Scaling down the channel length of transistors. a 2D vertical-channel transistors. Reproduced with permission. Reference [65] Copyright 2020, Wiley. b Vertical transistor with a sub-1-nm channel. Reproduced with permission. Reference [27] Copyright 2021, Springer Nature. c Sub-2 nm vertical-channel transistors. Reproduced with permission. Reference [66] Copyright 2023, American Chemical Society. d Monolayer WSe2 sloping-channel transistors. Reproduced with permission. Reference [67] Copyright 2023, American Chemical Society. e 2D fin field-effect transistors. Reproduced with permission. Reference [35] Copyright 2023, Springer Nature. f 2D devices with ultraflat sub-10 nm gap electrodes. Reproduced with permission. Reference [68] Copyright 2021, American Chemical Society. g Channel lengths of above 2D transistors

A significant breakthrough in this field is the creation of vertical transistors based on 2D materials [27, 65, 66, 69,70,71] (Fig. 6a–c). The first study, conducted by Liting Liu et al. [72], confirmed a MoS2 channel between source and drain electrodes in a vertical direction, termed as vertical field-effect transistors. This vertical-transistor configuration exhibits a minimized Fermi-level pinning effect and direct tunneling current. The group successfully fabricated sub-3-nm p-type and n-type vertical transistors using WSe2 and WS2. Moreover, multi-vertical-transistors can be vertically stacked, laying the foundation for high-density integrated circuits [73]. These vertical transistors’ on/off ratios are limited by a strong source-drain tunneling current in the off state. The van der Waals metal-contact method can be employed for suppressing the off-state tunneling current [66]. Additionally, 2D materials can also be transferred onto the source/drain electrode for sloping-short-channel transistors [67] (Fig. 6d).

The continuous advancement of silicon-based process nodes has the guiding significance for the size reduction and performance improvement of two-dimensional material-based transistors. The concept of FinFET in traditional silicon-based transistors has now been successfully implemented in two-dimensional material transistors. Another major breakthrough is the construction of 2D fin field-effect transistors, integrating single-crystal high-k gate oxide Bi2SeO5 and semiconductor Bi2O2Se epitaxially. These transistors demonstrate high electron mobility (μ) of 270 cm2 V−1 s−1, ultralow IOFF of 1 pA μm−1, high ION of 830 μA μm−1, high on/off current ratios (ION/IOFF) of 108 at a 400-nm channel length, providing at a new avenue for extending Moore’s law [35] (Fig. 6e). Figure 6g shows the quantitative comparation of channel lengths. Moreover, the fin-width of Bi2O2Se fin field-effect transistor can be shrunk down to 1.2 nm [35, 74]. Mao-Lin Chen et al. have constructed monolayer MoS2 fin field-effect transistor with sub-1 nm fin-width limit [75]. These results indicate that the channel width of 2D transistors can be shrunk down to approximately 1 nm. Currently, only Bi2O2Se and MoS2 have been employed for constructing FinFET structures in terms of fabrication. In Bi2O2Se FinFET, the vertical 2D Bi2O2Se channel was synthesized in homemade CVD systems [35]. While, in MoS2 FinFET, the vertical MoS2 channel was fabricated through many steps: Si on insulator substrate, 300 nm step, HfO2 coating, side wall etching, TMD growth, S–D patterning, Plane removing, Si wet etching, HfO2 supported ML-Fin, Top gate patterning [75]. Hence, we think Bi2O2Se-FinFET process is a viable FinFET process strategy due to its simpler process fabrication.

Statistical results have shown that 2D double-gate Transistors with 30-nm channel length exhibit high performance, further confirming the potential of 2D TMDs in transistor channel length scaling [76]. MoS2 transistors with a 3 nm channel length have been realized by the electromigration of metal interconnection, displaying on/off ratios up to 2 × 105 and field-effect mobility up to 33.5 cm2 V−1 s−1 [77]. Ultraflat gap electrodes have been employed to downscale 2D channels to sub-10 nm [68, 77, 78] (Fig. 6f). Despite these advances, scaling down transistors based on 2D TMDs poses challenges. As the channel length reduces, quantum mechanical effects like tunneling start to dominate, leading to increased leakage currents [79]. Additionally, achieving low contact resistance and high carrier mobility in scaled devices is a significant challenge due to the Schottky barrier at the metal–semiconductor interface [80, 81].

In general, we think 2D vertical-channel transistors are more compatible and feasible for large-scale production.

Recent advancements in 2D transistor design have driven the miniaturization of the channel length, challenges posed by quantum effects, variability, heat dissipation, fabrication costs, and contact resistance need to be addressed to sustain this trend and realize the potential of smaller, more efficient electronic devices [18]. To tackle these issues, research is exploring novel contact schemes, such as the use of phase-engineered TMDs or the integration of high work function metals [82]. It should be noted that the channel width can also be scaled down to one atomic layer [75]. Additionally, the impact of environmental factors like ambient humidity on 2D TMD devices is an area of ongoing study.

3.2 Reduction of the Gate Length

In a transistor, gate length—the distance over which an electric field controls current flow between the source and drain contacts—is crucial to its operation and overall device performance [83]. The gate length significantly influences the transistor's switching speed, power consumption, and drive current [54]. Shortening the gate length reduces the channel region traversed by carriers during operation, leading to quicker switching times. This enhances the transistor's operating speed, potentially improving the performance of the entire integrated circuit [84]. However, a shorter gate length can result in higher drive current due to the intensified electric fields in the channel. This increased current can lead to higher power consumption, presenting power management challenges in densely packed integrated circuits [85]. Despite these challenges, gate length reduction enables higher transistor density on chips, providing more computational power per unit area. This has propelled the extraordinary growth in processing power observed in the semiconductor industry, as exemplified by Moore's Law [25].

Nevertheless, shrinking the gate length into the nanometer regime brings several challenges. Quantum mechanical effects such as tunneling can become significant, increasing leakage currents and power dissipation [79]. When the gate length of silicon transistor decreases below 40 nm, adverse impacts such as drain-induced barrier lowering (DIBL) and self-heating effect (SHE) become more pronounced [86]. SHE can elevate device temperature, affecting reliability and lifespan, while DIBL can cause a significant shift in threshold voltage, increasing the device's off-state leakage current [54, 56].

The role of gate length becomes especially prominent in transistors based on 2D TMDs. 2D TMDs have demonstrated superior performance over traditional semiconductors like silicon in mitigating short-channel effects due to their thin bodies and large bandgaps [8]. The atomic thickness of 2D TMDs allows effective gate control even at extremely short gate lengths [39]. This permits aggressive device dimension scaling down to ~ nm level while maintaining effective electrostatic control over the channel, potentially leading to high-speed operation and low power consumption [87, 88].

Gate length also influences the contact resistance in 2D TMD transistors. As gate length decreases, the contact area reduces, potentially increasing contact resistance and lowering drive current [81]. Techniques such as contact engineering and the utilization of high-work-function metals have been proposed to address this issue [1].

Reducing a transistor’s gate length can significantly enhance performance and increase transistor density, it also introduces challenges related to quantum mechanical effects, power consumption, and device variability. Future research and innovation in transistor design and fabrication processes are necessary to overcome these challenges and continue the trend of transistor miniaturization. Ongoing advancements in 2D TMDs and further exploration of the interplay between gate length and device performance will contribute to the development of the next generation of miniaturized transistors.

As part of the exploration of the dimension and performance limits of transistors utilizing 2D TMDs, strategies for scaling down the gate length in traditional semiconductor transistors and those in 2D transistors will be compared to highlight the advantages of 2D TMDs.

3.2.1 Gate Length Reduction in Traditional Semiconductor Transistors

The reduction of gate length in transistors has been a key driver in advancing semiconductor technology. Various innovative techniques, each with its own advantages and challenges, have been adopted to achieve this. One significant technique is the transition from planar to three-dimensional transistor structures, including FinFET and Gate-All-Around (GAA) designs [56, 89]. These structures provide superior gate control and enable further gate length reduction without a significant increase in leakage current. The use of high-k dielectric materials in gate stacks is another innovative approach enabling gate length reduction. These materials offer higher gate capacitance, enhancing gate control at reduced gate lengths, minimizing leakage current, and improving device performance [90].

However, these methods present specific challenges. For example, fabricating 3D transistor structures is complex and necessitates advanced, technically challenging lithography techniques, such as EUV lithography. This can be costly. Additionally, using high-k dielectric materials can introduce interface traps and degrade carrier mobility, requiring further research and technological advancements to overcome these issues.

3.2.2 Gate Length Reduction in 2D Transistors

In transistors based on 2D TMDs, gate length reduction has been a focal point for researchers aiming to push the boundaries of device miniaturization [8, 91]. Various innovative techniques have been explored (Fig. 7), each with their unique benefits and challenges. One significant advancement was the development of MoS2 transistors with a mere 1-nm gate length, employing a single-walled carbon nanotube [92] (Fig. 7a). The study demonstrated that MoS2 outperforms Si at sub-5-nm channel-length scaling limits. In another study, the single-walled carbon nanotube was used as the gate electrode in homojunction-channel (MoTe2) transistors, further confirming the potential for 1-nm gate length in 2D transistors [93] (Fig. 7b). The use of vertical MoS2 transistor structures, where the gate length is sub-1-nm, is another significant technique [28] (Fig. 7c). In this work, Fan Wu et al. showed side-wall MoS2 transistors with a single graphene layer edge as the gate electrode, achieving a physical gate length of sub-1 nm. These devices demonstrated subthreshold swing values down to 117 mV dec−1 and on/off ratios up to 1.02 × 105, paving the way for continued transistor scaling in line with Moore’s law [28]. Dynamically doped transistors offer another innovative approach [94]. The 2021 study introduced the concept of a doping gate length (LDG), which is longer than traditional gate length (L) but does not necessitate a larger contact gate pitch (CGP) footprint. This technique can reduce gate length without increasing the overall transistor size, meeting the 2031 International Roadmap for Devices and Systems (IRDS) dimensional objectives for the so-called 1-nm-technology node and beyond [94]. Furthermore, the ab initio quantum-transport methods have successfully simulated sub-5 nm gate-length monolayer MoS2 transistors [95].

Scaling down the gate length of transistors. a MoS2 transistors with 1-nm gate lengths. Reproduced with permission. Reference [92] Copyright 2016, American Association for the Advancement of Science. b 1 T′/2H MoTe2 FET with a CNT gate. Reproduced with permission. Reference [93] Copyright 2019, Springer Nature. c Vertical MoS2 transistors with 0.34 nm monolayer graphene edge gate. Reproduced with permission. Reference [28] Copyright 2022, Springer Nature. d MoS2 Transistor with 10-nm Si fin gate length. Reproduced with permission. Reference [96] Copyright 2019, Institute of Electrical and Electronics Engineers Inc. e Gate lengths of above 2D transistors

In another study, Yu Pan et al. investigated MoS2 transistors with a 10-nm gate length, using a Si Fin structure as the gate electrode [96, 97] (Fig. 7d). This novel design achieved an on/off ratio of over 106, showing promise for future scaled 2-D material transistors. Figure 7e shows the quantitative comparation of gate lengths.

Nonetheless, these techniques present challenges. Gate length reduction to the nanometer scale can lead to increased leakage current, a significant challenge for device performance and energy efficiency. Moreover, the fabrication processes for creating such small structures are complex and require high precision, which can be challenging to achieve and scale for mass production. Advancements in material science and device engineering are expected to pave the way for further miniaturization of these devices [60, 98].

3.3 Minimization of the Source/Drain Contact Length

The contact length, the distance at which the source and drain regions establish contact with the channel, profoundly influences a transistor's resistance, capacitance, and consequently, its speed and power consumption [83]. This parameter is particularly significant in transistors based on 2D TMDs, where it directly impacts performance and energy efficiency [99].

In transistor operation, carriers traverse between the channel and contact metals across an effective pass length, known as the transfer length. According to the current crowding model, carriers preferentially enter the semiconductor via the periphery of metal–semiconductor contact regions, rendering the transfer length considerably smaller than the contact length [100]. Thus, the theory proposes that the contact length can continuously scale to the transfer length, providing a theoretical basis for contact length minimization. From an energy efficiency perspective, reducing the contact length decreases the voltage drop across the source and drain regions, thereby lowering power consumption during transistor operation [101]. Additionally, a smaller contact length can decrease gate capacitance, potentially resulting in a lower threshold voltage and reduced power consumption [8]. This is particularly relevant in modern integrated circuits, where power consumption and dissipation are pivotal considerations.

However, reducing the contact length also diminishes the contact area, potentially increasing contact resistance. Elevated contact resistance can reduce the drive current, potentially impairing device performance, including switching speed [54]. The contact length also impacts short-channel effects [56]. A diminished contact length can augment short-channel effects, such as drain-induced barrier lowering (DIBL) and velocity saturation, adversely affecting device performance. Nevertheless, inherent properties of 2D TMDs, like their thin body and large bandgap, can help counteract these effects [102, 103]. Despite the benefits, minimizing the source/drain contact length presents challenges. As contact length decreases, maintaining effective electrical contact between the source/drain regions and the channel grows increasingly difficult [104, 105]. Increased contact resistance can negate the benefits of reduced series resistance and may induce variability in device performance. Furthermore, as the contact length shrinks to nanometer scales, the fabrication process becomes more intricate. Advanced lithography and self-aligned techniques are often necessary, introducing additional cost and complexity.

Contact length in 2D TMD transistors significantly influences device energy efficiency and performance. However, the net impact is a complex interplay of various factors, including contact resistance, parasitic capacitance, gate capacitance, and short-channel effects. Therefore, careful optimization of the contact length is crucial to maximize the performance and energy efficiency of these devices.

As part of the exploration of the dimension and performance limits of transistors utilizing 2D TMDs, strategies for scaling down the contact length in traditional semiconductor transistors and those in 2D transistors will be compared to highlight the advantages of 2D TMDs.

3.3.1 Source/Drain Minimization in Traditional Semiconductor Transistors

The minimization of source/drain contact length constitutes a key aspect of the MOSFET scaling trend. Various techniques and technological advancements have been utilized to reduce contact length, each bearing its own efficacy and challenges. The implementation of Raised Source/Drain (RSD) structures has emerged as an effective strategy [106]. RSDs decrease contact length by forming additional silicon layers atop the source and drain regions, thereby reducing the series resistance and enhancing transistor performance. The introduction of Self-Aligned Contact (SAC) techniques constitutes another significant development [107]. SAC processes align contacts directly over the transistor's active regions, enhancing precision while reducing contact length. The use of silicide, a silicon-metal compound, has also proven instrumental in diminishing contact length [108]. Silicide reduces contact resistance between the metal contact and the silicon of the source/drain regions, facilitating further contact length reduction.

Despite their benefits, these methods each pose unique challenges. The fabrication of RSD structures necessitates precise epitaxial growth techniques, which are technically demanding and costly. SAC techniques, despite facilitating excellent alignment, require intricate lithography and etching processes. The use of silicide can introduce issues such as agglomeration and junction spiking, potentially degrading transistor performance. Moreover, as contact lengths continue to shrink, maintaining reliable, low-resistance contacts becomes increasingly challenging. Continued research and innovation are required to sustain the trend of contact length reduction, fostering more efficient and compact transistors.

3.3.2 Source/Drain Minimization in 2D Transistors

The reduction of contact length in 2D TMD transistors is a vital aspect of device miniaturization. Several methods have been proposed and implemented (Fig. 8), each with its unique efficacy and challenges. Advanced lithography techniques, such as EUV lithography and electron-beam lithography, are primary methods for reducing contact length [31, 109, 110] (Fig. 8a). These techniques afford precise control over the patterning process, enabling the fabrication of devices with nanoscale contact lengths. However, they tend to incur high equipment costs and complex processing steps, which can hinder mass production. The use of metallic edge contacts has proven effective. Edge-contact technique has been employed for PtSe2 and MoS2 transistors [111,112,113] (Fig. 8b, c, e). These edge-contact transistors exhibit contact performance comparable to top/bottom contact configurations but with a significantly reduced footprint. Similar metallic edge contacts have also been shown in graphene-nanoribbon [114] and graphene transistors [115]. However, this fabrication process involves complex steps. Phase engineering also can be used for edge contacts in 2D TMD transistors [116] (Fig. 8f). Another innovative technique involves the use of one-dimensional single-walled carbon nanotube electrodes as the source/drain electrodes of 2D transistors [29] (Fig. 8d). Figure 8g shows the quantitative comparation of contact lengths. This allows the contact length to scale into the sub-2 nm region, providing a novel approach for future nanoelectronics miniaturization. Semimetal graphene-nanoribbons have also been used for the source/drain electrodes of 2D transistors, exhibiting excellent device performance [117]. However, these techniques necessitate precise alignment processes, escalating the fabrication difficulty [118].

Scaling down the contact length of transistors. a Ultrascaled contacts for monolayer MoS2 FET. Reproduced with permission. Reference [109] Copyright 2023, American Chemical Society. b PtSe2 FET with PtTe2 edge contacts. Reproduced with permission. Reference [111] Copyright 2022, Elsevier. c MoS2 transistors using in situ edge contacts. Reproduced with permission. Reference [112] Copyright 2019, American Chemical Society. d MoS2 FET with single-walled-carbon-nanotube contacts. Reproduced with permission. Reference [29] Copyright 2023, Springer Nature. e MoS2 FET with one-dimensional edge contacts. Reproduced with permission. Reference [113] Copyright 2019, American Chemical Society. f MoTe2 FET with phase-transition contacts. Reproduced with permission. Reference [116] Copyright 2020, Wiley–VCH Verlag. g Contact lengths of above 2D transistors

In general, we think phase-transition-contact transistors are more compatible and feasible for large-scale production.

Various methods have been developed for source/drain contact length reduction in 2D TMD transistors, each carrying unique challenges that need to be addressed. Ongoing advancements in material science and device engineering are anticipated to facilitate further reductions in source/drain contact length.

3.4 Reduction of the Dielectric Thickness

The dielectric thickness, often associated with gate oxide thickness in a MOSFET, significantly influences transistor operation. It directly affects the transistor's performance, power consumption, and leakage current [119], particularly relevant in the context of transistors based on 2D TMDs [120].

In a FET, the dielectric material separates the gate electrode from the conductive channel, typically a 2D TMD material like MoS2. The thickness of this dielectric layer, often termed gate oxide thickness, directly impacts the electrostatic control of the gate over the channel [121]. A decrease in dielectric thickness enhances gate control, improving transistor performance parameters such as on-current and subthreshold swing. Hence, dielectric thickness reduction remains a key aspect of transistor scaling. However, a decrease in dielectric thickness also leads to an increase in leakage current, presenting a significant challenge in transistor scaling. Two primary mechanisms of leakage current in a MOSFET are gate oxide leakage [122] and subthreshold leakage [123]. Gate oxide leakage occurs when electrons tunnel through the thin dielectric layer, a phenomenon known as direct tunneling. As the dielectric thickness decreases, direct tunneling probability increases, resulting in a higher gate leakage current. Apart from power wastage, leakage current can induce issues such as heating, noise, and even device failure [124]. Subthreshold leakage, in contrast, arises from the finite off-state current in the transistor when it should be in the ‘off’ state. This leakage is exacerbated by dielectric thickness reduction because it leads to a decrease in the transistor's threshold voltage.

Several strategies have been proposed to balance dielectric thickness and leakage current in 2D TMD transistors. These include the use of high-k dielectrics, offering high permittivity while minimizing leakage current [36, 87], and the implementation of passivation techniques to reduce trap densities and surface roughness [125]. Moreover, innovative device architectures, such as double-gate or gate-all-around structures, can enhance gate control while maintaining a relatively thick dielectric layer [126, 127].

The dielectric thickness is a crucial parameter in 2D TMD transistor operation, affecting both the transistor's performance and leakage current. Despite the challenges, ongoing research is exploring new materials and device architectures to optimize this critical parameter [18], continuing the trend of transistor scaling. Reducing the dielectric thickness has been a principal strategy for enhancing the performance of MOSFETs.

3.4.1 Reduction of the Dielectric Thickness in Traditional Semiconductor Transistors

Several strategies have been employed to Traditional Semiconductor Transistors, each with its respective effectiveness and challenges. An early strategy entailed thinning the silicon dioxide (SiO2) layer used as the gate dielectric [56]. While this approach succeeded in improving device performance by enhancing gate control over the channel region, quantum mechanical tunneling-induced leakage currents significantly increased as the SiO2 layer was reduced to near-atomic scales [119]. To mitigate this issue, high-k dielectric materials were introduced as alternatives to SiO2 [90]. High-k materials, such as Hafnium Oxide (HfO2), possess a higher dielectric constant (k), which allows for a physically thicker layer offering the same capacitive properties as a thinner SiO2 layer, thereby reducing leakage current. However, these materials present challenges such as increased gate leakage due to defects and traps within the high-k material, and threshold voltage instability [128]. Another strategy involves the utilization of multi-gate transistor architectures, like FinFETs [107]. These structures use a three-dimensional "fin" shaped channel region, surrounded by the gate on multiple sides, allowing superior gate control over the channel even with a thicker dielectric layer, thereby reducing leakage current. However, FinFET structures are more complex to fabricate and integrate into existing manufacturing processes. While strategies such as the use of high-k materials and multi-gate architectures have proved effective in achieving dielectric thickness reduction, they introduce new challenges. Further research and innovation are required to address these challenges and perpetuate the trend of transistor scaling.

3.4.2 Reduction of the Dielectric Thickness in 2D Transistors

In 2D TMD transistors, reducing dielectric thickness is also a strategic approach to enhance the electrostatic control of the gate over the channel, thereby improving transistor performance. Below, we analyze some strategies for dielectric thickness reduction (Fig. 9), their effectiveness, and associated challenges. One is the application of high-k dielectrics. High-k dielectric materials, such as Hf(Zr)1+xO2, Sb2O3, SrTiO3, Bi2SiO5, LaOCl, Sr2Nb3O10, fluoride film offer high permittivity, allowing for thinner effective oxide thickness while maintaining relatively low leakage current [30, 129,130,131,132,133,134,135,136,137,138,139,140,141,142,143,144,145] (Fig. 9a–h). Figure 9i, j show the quantitative comparation of dielectric thicknesses and constants, respectively. These materials, having been successfully integrated into 2D TMD transistors, result in improved subthreshold swing and on-current. However, it is difficult to acquire clean interface between the high-k dielectric and the TMD channel [121, 146]. Passivation technique is another approach to reduce dielectric thickness. Surface passivation techniques, including chemical and physical approaches, can reduce trap densities and surface roughness in 2D TMD materials [147,148,149], thereby reducing the leakage current and enabling the use of thinner dielectrics. However, these techniques often demand high-temperature processes potentially damaging the 2D TMD layers. Another approach is to use novel device architectures. For instance, double-gate or gate-all-around structures can provide improved gate control with a relatively thick dielectric layer [35, 126]. These architectures can reduce the electric field at the gate oxide/TMD interface, thereby reducing leakage current. However, the fabrication of these structures is more complex and can increase the overall device cost. The utilization of 2D materials as dielectrics also can effectively reduce dielectric thickness. 2D Hexagonal Boron Nitride (h-BN) has been proposed as a dielectric material for 2D TMD transistors [150]. These materials can be scaled down to a few atomic layers, allowing for ultra-thin dielectrics with low leakage current. However, integrating 2D h-BN as dielectrics presents challenges such as material synthesis, device fabrication, and interface quality.

Scaling down the dielectric thickness of transistors. a Laser-writable high-k dielectric for van der Waals nanoelectronics. Reproduced with permission. Reference [129] Copyright 2019, American Association for the Advancement of Science. b The hybrid HfO2/Sb2O3 dielectrics integrated on 2D MoS2. Reproduced with permission. Reference [130] Copyright 2023, Springer Nature. c Bi2O2Se transistor with Bi2SeO5 dielectric nanosheets. Reproduced with permission. Reference [131] Copyright 2023, Springer Nature. d Back-gate MoS2 four-probe FETs device. Reproduced with permission. Reference [132] Copyright 2023, Springer Nature. e MoS2 back-gated FET with SrTiO3 dielectric material. Reproduced with permission. Reference [30] Copyright 2022, Springer Nature. f MoS2 FET with hybrid PTCDA/HfO2 gate stack. Reproduced with permission. Reference [133] Copyright 2019, Springer Nature. g Bi2O2Se transistor with Bi2SeO5 dielectric nanosheets. Reproduced with permission. Reference [134] Copyright 2022, Springer Nature. h WSe2 FET using 2D-BN dielectric interface. Reproduced with permission. Reference [150] Copyright 2019, Springer Nature. i Dielectric thickness of above 2D transistors. j Dielectric constants of above 2D transistors

In general, we think dielectric materials such as Sb2O3, Bi2SeO5, SrTiO3, and HfO2, hold the promise for scalable production. The corresponding high-k dielectric transistors are more compatible and feasible for large-scale production.

Strategies for dielectric thickness reduction in 2D TMD transistors involve a trade-off between improved transistor performance and increased leakage current. Despite these challenges, ongoing research continues to explore new materials, techniques, and architectures that can optimize dielectric thickness while maintaining low leakage current.

4 Performance of 2D TMDs Transistors

In the realm of semiconductor technology, the relentless push towards miniaturization coupled with the quest for higher performance and energy efficiency has led to the exploration of two-dimensional (2D) materials for transistors. These materials, often only a few atoms thick, promise a revolutionary step beyond the limitations of traditional silicon-based devices. However, to fully harness the potential of 2D transistors, several key electrical characteristics must be optimized. These include reducing source/drain contact resistance, minimizing subthreshold swing, decreasing hysteresis loop, enhancing carrier mobility, and improving the on/off current ratio. Optimizing these electrical characteristics in 2D transistors is not just about pushing the frontiers of miniaturization; it is about achieving greater computational power, energy efficiency, and reliability in the electronics that permeate every aspect of modern life, from smartphones to supercomputers. The continued advancement in 2D transistor technology promises to be a cornerstone in the evolution of next-generation electronics.

4.1 Reduction of Source/Drain Contact Resistance

The source/drain (S/D) contact resistance in a transistor significantly affects overall device performance and power consumption, especially in transistors based on 2D TMDs [151]. The contact resistance largely determines the effective mobility of charge carriers, regulating the current flow rate through the transistor, and thereby impacting the overall device performance [152]. Elevated S/D contact resistance can considerably degrade transistor performance by reducing the device's current drive capability [153]. The contact resistance forms a barrier that hinders carrier flow from the source to the channel and from the channel to the drain, thereby limiting the transistor's switching speed and affecting the overall device performance [56]. This issue is especially problematic for high-frequency applications that demand fast switching times for efficient operation [151]. Furthermore, high S/D contact resistance can augment power consumption. In a transistor, power is consumed not only during the switching operation but also when a current flows through the device due to encountered resistance. Consequently, high contact resistance can lead to increased power dissipation, reducing energy efficiency and potentially causing thermal management problems in high-performance electronic systems. This issue is of particular concern in the current era of electronic devices where energy efficiency is paramount. For 2D TMD-based transistors, the thin nature of these 2D materials suggests that the contact region has a larger impact on overall device performance compared to bulkier three-dimensional materials [81, 154,155,156,157,158].

Therefore, to enhance the performance of these transistors, it is essential to reduce the contact resistance between the source/drain and the 2D TMD material. This reduction can be achieved through various methods, such as implementing novel contact materials [31, 159], interface engineering [152, 160], contact engineering techniques [80, 161, 162], self-aligned contact processes [151], or by modifying the 2D TMD material itself [163, 164]. However, these strategies can introduce additional challenges, including increased fabrication complexity, potential degradation of the 2D TMD material, and potential incompatibility with existing semiconductor fabrication processes [157]. The contact engineering techniques are typically employed to reduce contact resistance. Yet, in the context of 2D TMDs, the ultrathin nature of these materials presents unique challenges for contact engineering. Traditional methods used in silicon-based electronics, such as selective ion implantation, are not applicable due to the ultrathin body of monolayer and few-layer TMDs [165]. Furthermore, the variation in electron affinity, band gap, and band alignments among different TMDs complicates the contact engineering process [157]. Thus, additional research is needed to develop effective strategies for reducing contact resistance that do not compromise the intrinsic properties of the 2D TMD material and that are compatible with existing processes [166].

4.1.1 Current Strategies in Resistance Reduction in Traditional Semiconductor Transistors

FETs are the bedrock of contemporary semiconductor devices. Their performance is profoundly influenced by the source/drain contact resistance. The current strategies employed to reduce this contact resistance are multifarious, each with distinct levels of efficacy and unique challenges.

A prevalent strategy involves utilizing metal silicide contacts such as nickel silicide or titanium silicide. These materials form a low-resistance ohmic contact with silicon, thereby enhancing device performance [167]. However, the formation of these silicides necessitates high-temperature annealing, potentially leading to unwanted diffusion or junction leakage [19]. Another approach involves heavily doping the source/drain regions to diminish the Schottky barrier height, thereby reducing contact resistance. Nevertheless, heavy doping can result in increased leakage current, consequently degrading transistor performance [168].

Two strategies exist for reducing source/drain contact resistance in Si FETs, each carries its own set of challenges. Therefore, current research continues to probe novel materials and innovative fabrication techniques to further optimize the performance of Si FETs [169].

4.1.2 Current Strategies in Resistance Reduction in 2D Transistors

The reduction of source/drain (S/D) contact resistance is a pivotal aspect in 2D transistor design and fabrication, significantly influencing overall device performance [21, 170]. Various strategies have been devised to address this challenge (Fig. 10), each presenting unique benefits and drawbacks.

Contact resistance reduction of 2D transistors involves four strategies such as novel contact materials, doping engineering, interface engineering, and phase-change engineering. a The quantum limit in MoS2 FET. Reproduced with permission. Reference [31] Copyright 2023, Springer Nature. b MoS2 FET with semimetal (Bi) contacts. Reproduced with permission. Reference [156] Copyright 2021, Springer Nature. c Double-gate InSe FET. Reproduced with permission. Reference [171] Copyright 2023, Springer Nature. d WSe2 FET with degenerately p-doped WSe2 (Nb0.005W0.995Se2) contacts. Reproduced with permission. Reference [172] Copyright 2016, American Chemical Society. e ZrTe2-contacted MoS2 transistor. Reproduced with permission. Reference [160] Copyright 2023, American Chemical Society. f Ideal spacer doping layer for 2D devices. Reproduced with permission. Reference [164] Copyright 2023, American Chemical Society. g MoTe2 device with a 1 T'/2H phase homojunction. Reproduced with permission. Reference [173] Copyright 2015, American Association for the Advancement of Science. h 2D MoGe2N4 FET with Mxene contacts. Reproduced with permission. Reference [174] Copyright 2023, Royal Society of Chemistry. i WSe2 FET with VSe2 contact. Reproduced with permission. Reference [152] Copyright 2023, Springer Nature. j Contact resistance of above 2D transistors

One approach involves using novel contact materials. Antimony (Sb) or Bismuth (Bi) or Yttrium (Y) have been employed to reduce contact resistance in n-type transistors [31, 156] (Fig. 10a, b). Sb-MoS2 contact can approach the quantum limit due to hybridization of M–S energy bands at the Fermi energy [31]. Bi-MoS2 contact is ohmic contact, owing to the suppression of metal-induced gap states [156]. Y-InSe contact realize the ohmic contact, benefiting from that Y doping converts semiconducting InSe into semimetallic Y-InSe [171] (Fig. 10c). While these materials can effectively decrease contact resistance, they can introduce complications including potential reactions with semiconductor materials, stability issues, and integration challenges [175]. Interface engineering is another promising strategy. This approach entails creating an ultra-thin interfacial layer between the metal and the semiconductor to ensure ohmic contact, aiding in reducing contact resistance [152, 160, 171,172,173, 176,177,178,179,180] (Fig. 10d, e, g, i). However, maintaining precise control of the interfacial layer properties, such as thickness, uniformity, and chemical composition, can be technically challenging. The implementation of self-aligned contact processes is a third approach. Here, the S/D regions are formed after defining the gate stack, thereby allowing the contacts to be closely aligned with the gate, reducing parasitic resistance [151]. However, this technique demands a high level of process control and can introduce complexity into the fabrication process. Doping strategies have also been used to reduce contact resistance. For instance, implanting dopants into the S/D regions can augment the carrier concentration, thereby reducing the contact resistance [163, 164, 181, 182] (Fig. 10f). However, this approach can induce defects and degrade the intrinsic properties of the semiconductor material. Contact engineering techniques, such as edge contact formation [82], local pressurization contact [161], van der Waals clean interface contacts [154, 159, 183,184,185,186,187,188,189,190,191], phase engineering [192,193,194,195], and superplastic deformation [162], have been effective in reducing contact resistance. Figure 10j shows the quantitative comparation of contact resistance. These strategies involve creating contacts at the edge of the 2D TMD, instead of the top surface, which has been shown to reduce contact resistance due to the higher density of states at the edges of these materials. However, while promising, contact engineering techniques can increase fabrication complexity and may not be feasible for all device architectures.

In general, we think novel-contact-material transistors are more compatible and feasible for large-scale production.

Several strategies for reducing contact resistance in 2D TMD transistors are effective, each carries its own set of challenges. Additional research is needed to develop, optimize, and overcome the challenges associated with these strategies, ensuring compatibility with existing fabrication processes without compromising the inherent advantages of 2D TMDs [166, 174] (Fig. 10h). Recently, machine learning has been employed to screen low-contact electrode for 2D semiconductor [196], indicating its prospect in resistance reduction in 2D transistors.

4.2 Reduction of Subthreshold Swing

The subthreshold swing (SS) is a critical parameter in transistor operation, quantifying the required change in gate voltage to achieve an order of magnitude change in the drain current within the subthreshold region. Essentially, the SS characterizes the transistor's "off" state efficiency [123]. Notably, SS impacts power efficiency. Despite a transistor being in its "off" state, a small amount of leakage current persists. The magnitude of this leakage current is contingent upon the SS. A larger SS correlates with more leakage current, thereby escalating static power consumption [197]. This becomes particularly detrimental in low-power applications, like mobile devices and wearable technology, where power efficiency is paramount [198]. Hence, a lower SS enhances the transistor's switching efficiency between the "on" and "off" states, subsequently reducing power consumption.

Reducing the SS can amplify both the speed and power efficiency of a transistor. However, due to thermal constraints, the SS of conventional MOSFETs cannot fall below a certain threshold (approximately 60 mV decade−1 at room temperature) [199]. To surpass this limit, innovative transistor designs and technologies are under exploration. For instance, Tunnel Field-Effect Transistors (TFETs) can achieve an SS beneath the thermal limit by utilizing band-to-band tunneling [200]. Nonetheless, TFETs encounter challenges, including diminished on-currents and complexities in fabricating high-quality tunneling junctions [201].

An alternative approach involves Negative Capacitance Field-Effect Transistors (NCFETs), which use ferroelectric materials in the gate stack to provide internal voltage amplification and diminish the SS [202]. However, the practical implementation of NCFETs confronts obstacles such as ferroelectric material integration and reliability [203].

2D monolayer TMDs, such as MoS2, WS2, and WSe2, possess distinctive properties like a direct bandgap and high carrier mobility, positioning them as promising candidates for next-generation electronic devices. Regarding transistors based on 2D TMDs, the SS assumes considerable significance due to these materials' atomic thickness. Unlike bulk semiconductors, 2D TMDs can potentially attain an ideal SS close to the thermal limit of 60 mV dec−1 at room temperature, thanks to their ultra-thin body that ensures robust gate control and an efficient suppression of the off-state current [39]. A low SS is advantageous for realizing high-precision, low-power digital circuits. It is especially important in low-power applications, where a substantial part of the power is consumed while the transistor is in the subthreshold region [204]. Therefore, the potential of 2D TMDs to achieve a low SS is a crucial benefit in the pursuit of power-efficient electronics.

Several strategies have recently been proposed to address these issues, including negative-capacitance FETs [205], tunneling FETs [206], impact ionization FETs [207], resistive gate FETs [208], and Dirac-source FET [209]. However, achieving a low SS in 2D TMD transistor devices is fraught with challenges. Material defects, interface traps, and contact resistance can all degrade the SS. These issues can be exacerbated by the inherent sensitivity of these atomically thin materials to their environment [18].

The role of SS in transistor performance is crucial, particularly regarding power efficiency. Transistors based on 2D TMDs show promise in achieving low SS values, potentially leading to more power-efficient devices. However, further research is needed to overcome the challenges associated with these materials. Therefore, meticulous optimization of the device structure and material quality is mandatory to harness the potential benefits of 2D TMDs in achieving low SS and high-power efficiency.

4.2.1 Current Strategies in Subthreshold Swing Reduction in Traditional Semiconductor Transistors

Subthreshold swing (SS) reduction has emerged as a pertinent research focus in transistor technology, with various promising strategies under exploration. Tunnel Field-Effect Transistors (TFETs) represent a compelling approach. They exploit band-to-band tunneling to activate the transistor, achieving an SS lower than the thermal limit of 60 mV decade−1 at room temperature [79]. However, TFETs often exhibit low on-currents, and fabricating high-quality tunneling junctions remains a formidable task [201]. Negative Capacitance Field-Effect Transistors (NCFETs) offer another promising avenue. By incorporating ferroelectric material into the gate stack, NCFETs achieve internal voltage amplification, thereby reducing the SS [202]. Nonetheless, integrating ferroelectric materials into transistor structure poses challenges, and reliability concerns linked to these materials persist [203]. Nanoelectromechanical FETs (NEM-FETs) present a potential method for lowering SS beneath the thermal limit [210]. Upon applying the threshold voltage to the transistor's gate electrode, an abrupt mechanical movement brings the electrode close to the gate dielectric layer. This movement induces rapid carrier increase in the channel, facilitating swift off-to-on transition, resulting in a significantly low SS. However, fabricating a suspended gate in a MOSFET proves challenging, necessitating advanced techniques and increasing process variability.

Various strategies for SS reduction and consequent transistor performance improvement exist, each presents unique challenges. Continuous research and innovation are imperative for refining these strategies and devising novel approaches.

4.2.2 Current Strategies in Subthreshold Swing Reduction in 2D Transistors

SS reduction, capable of enhancing transistor efficiency, is also a focal point in the realm of 2D TMD transistors. Various strategies, each with distinct benefits and drawbacks, have been developed to address this challenge (Fig. 11).

Subthreshold swing reduction of 2D transistors involves negative capacitance effect, resistive gate effect, tunnel effect, Dirac-source effect, and impact ionization effect. a MoS2 NC-FET. Reproduced with permission. Reference [211] Copyright 2020, Wiley-Blackwell. b CIPS/MoS2 vdW NC-FET. Reproduced with permission. Reference [212] Copyright 2019, Springer Nature. c MoS2 NC-FET. Reproduced with permission. Reference [213] Copyright 2018, Springer Nature. d MoS2/h-BN/graphene/CIPS vdW FeFET. Reproduced with permission. Reference [32] Copyright 2021, Springer Nature. e Atomic threshold switching MoS2 FET. Reproduced with permission. Reference [214] Copyright 2021, Wiley–VCH Verlag. f MoS2 TFET. Reproduced with permission. Reference [215] Copyright 2015, Springer Nature. g MoS2/Graphene Dirac-source FET. Reproduced with permission. Reference [209] Copyright 2021, American Chemical Society. h Nanoscale vertical impact-ionization transistor. Reproduced with permission. Reference [207] Copyright 2020, American Chemical Society. i Subthreshold swings of above 2D transistors

One prevalent strategy involves the creation of NC-FETs [32, 143, 205, 211,212,213, 216,217,218] (Fig. 11a–d). These 2D NCFETs incorporate a ferroelectric material in the gate stack, consequently achieving internal voltage amplification and record low SS, breaking the thermal limit of 60 mV decade−1. However, the practical implementation of NCFETs with 2D TMDs is still nascent, and acquiring high-quality ferroelectric materials presents difficulties [219]. Further research is required to overcome stability and reliability-related challenges. TFETs offer another viable method for achieving low SS [206, 215, 220] (Fig. 11f). These devices leverage band-to-band tunneling for transistor activation, facilitating an SS lower than the thermal limit at room temperature. However, the fabrication of high-quality tunneling junctions in 2D T-FETs necessitates precise alignment of various 2D materials, complicating the process and limiting practical applications. Impact Ionization FETs (II-FETs) represent another strategy [207, 221] (Fig. 11h). 2D II-FETs employ high-quality 2D heterostructures. Due to the internal gain mechanism in sub-mean-free-path channels, the ballistic impact-ionization process facilitates carrier multiplication, inducing a record low SS during transistor switching. However, fabricating such heterostructures requires precise control over material quality and alignment, limiting potential applications. The novel configuration of Resistive Gate FETs (RG-FETs) has shown promise for achieving extremely low SS [208, 214, 222, 223] (Fig. 11e). 2D RG-FETs combine a memristor and a transistor, with the memristor connected to the transistor's gate electrode. When the threshold voltage is applied to the memristor, it connects the up and down electrodes, transferring the threshold voltage to the transistor's gate. This movement induces a rapid increase in channel carriers, facilitating swift transistor switching and achieving a record low SS. However, integrating a 2D memristor and transistor is complex, thus complicating device fabrication. The memristor connects transistor's drain electrode also can realize low SS transistor [224]. The Dirac-Source FET (DS-FET) configuration provides another measure for SS reduction [209] (Fig. 11g). In this configuration, the source electrode is fabricated from graphene instead of conventional noble metal materials. As graphene possesses a Dirac cone energy band, it induces a sharp change in channel-carrier density during transistor switching, resulting in an SS lower than 60 mV decade−1. However, DS-FETs require a precise alignment process, which adds complexity to the device fabrication. Figure 11i shows the quantitative comparation of subthreshold swings. Another way to reduce SS is the Cold-Source FETs, where a “cold” metal is used to replace a conventional metal in a FET contact. Unlike conventional metals, “cold” metals have an energy gap around the Fermi level and function like p- or n-type doped semiconductors. As a result, electrons in this energy region can be effectively filtered out, leading to switching at less than 60 mV decade−1 [225,226,227,228,229]. Van der Waals heterojunction field-effect transistors (vdWJFETs) also show promise for SS reduction [230]. However, these FETs involve a complex fabrication process.

In general, we think NC transistors are more compatible and feasible for large-scale production.

Overall, while several strategies exist for reducing SS in 2D TMD transistors, each presents its unique set of challenges. Further research is required to optimize these strategies and develop new approaches that can overcome these limitations, thereby fully realizing the potential of 2D TMDs in power-efficient electronic devices.

4.3 Reduction of Hysteresis Loop

The hysteresis effect is a phenomenon whereby a transistor's output is contingent not only upon its immediate input, but also its historical input. Ideally, output characteristics should trace identical paths during the input voltage's rising and falling phases, thereby eliminating hysteresis. However, practical devices often exhibit hysteresis due to factors such as charge trapping and thermal effects. This effect manifests in the transfer characteristics of transistor operation as a loop when the gate voltage undergoes a bidirectional sweep. The hysteresis loop is integral to defining the stability and reliability of the device. It becomes a critical parameter in applications like memory devices, where the transistor's sustained state is consequential [231].