Abstract

Logic gates are fundamental components of integrated circuits, and integration strategies involving multiple logic gates and advanced materials have been developed to meet the development requirements of high-density integrated circuits. However, these strategies are still far from being widely applicable owing to their incompatibility with the modern silicon-based foundry lines. Here, we propose a silicon-foundry-line-based multi-gate one-transistor design to simplify the conventional multi-transistor logic gates into one-transistor gates, thus reducing the circuit footprint by at least 40%. More importantly, the proposed configuration could simultaneously provide the multi-functionalities of logic gates, memory, and artificial synapses. In particular, our design could mimic the artificial synapses in three dimensions while simultaneously being implemented by standard silicon-on-insulator process technology. The foundry-line-compatible one-transistor design has great potential for immediate and widespread applications in next-generation multifunctional electronics.

Similar content being viewed by others

Introduction

The miniaturization of integrated circuits and the relentless increase of device densities, which is described by the Moore’s law, have made it critical to constantly render breakthroughs in designs to overcome any associated manufacturing challenges1,2,3,4,5,6,7. The era of big data requires advanced strategies for achieving a higher density of circuits devices while entailing less sophisticated fabrication techniques2,8,9. To fulfill this goal, advanced designs and materials are constantly being proposed for logic gates and memory devices, which are the fundamental functional units of integrated circuits1,6,7,10.

Up to date, several designs, materials, and methods have been proposed for miniaturizing logic gates, such as two-dimensional material facilitated designs, quantum logic gates, biocircuits and nanotube gates11,12,13,14,15,16,17,18,19. Such designs have been effective for updating circuits, but they are still far from being applied on a large industrial scale. For instance, quantum logic gates can be scaled down with the existing silicon technologies; however, extremely low temperatures are needed as their working conditions20. Biocircuits are sensitive to working conditions such as high temperatures and incompatible with existing well-developed foundry lines18,19. Zhu et al. used multiple transistor designs to improve the accuracy and reliability of temperature sensors9. However, compared to the structure proposed in this study, their device is considerably more complex. Choi et al. used a multi-gate structure to achieve a versatile control of transistors2, whereas fin field-effect transistors (FinFETs) were employed in other studies8. However, using the transistor side-gate design does not reduce the device footprint in the circuits, and none of the existing multi-gate designs aimed to reduce the transistor number for circuit simplification. In recent works, we proposed advanced designs to reduce the number of transistors used in a circuit, thereby effectively solving the downsizing problem in modern electronics3,21,22. Our previous works reported the simulation result3, and the bottom-gate structure of indium gallium zinc oxide transistor was mainly implemented in the lab with limited functions21,22. Here, the proposed design is a top gate structure with process-in-memory function, which is compatible with and implemented by the Si-foundry lines processing, thus promising immediate and practical applications.

Memory design is another rapidly progressing frontier in modern electronics with pioneering proposals, such as magnetic random-access memories (MRAMs), phase-change memories, ferroelectric RAMs, and resistive switching memristors22,23,24,25,26,27,28,29. However, the existing devices require dedicated materials and the fabrication costs are often much higher than the standard Si processes. The simplest structure, i.e., the two-terminal memristor, has reliability issues, while the others are difficult to scale down owing to their complex structures or processing, and the underdeveloped trials in most cases are not immediately implementable29. Despite their performance limitations, dynamic random-access memories (DRAMs) and flash memories based on the Si technology are still primarily used in consumer electronics23,24,25,26,27,28,29. However, a DRAM requires more than one transistor, which limits the space utilization and scaling of integrated systems. To increase the density of circuit devices, developing advanced designs with decreased footprints is the most pressing task for advancing electronics including portable devices such as flexible sensors and artificial intelligence (AI).

The conventional von Neumann structures involve logic gates for data processing and memory devices for data storage in separated units, which leads to low efficiency and high energy consumption. In contrast, process-in-memory devices could process and store data in a single element, and recently they have been widely and intensively investigated. Such emerging devices could be used as artificial synaptic devices for hardware-based neuromorphic computing, which is inspired by the brain at the hardware level30,31. However, the process-in-memory devices mainly have two or three terminals, which limits the mimicking controllability of the artificial synaptic behaviors to only two dimensions (2D). The devices with more terminals, which are more similar to the real synapses with multiple channels, are required for realizing more effective control of artificial synaptic behaviors in three dimensions (3D).

This work proposes a one-transistor process-in-memory device strategy with a multi-functional multi-gate one-transistor (MGT) design of multiple electrodes, which can implement logic gate functionalities that normally require two to six transistors. The proposed design can be implemented using Si-based foundry lines and significantly reduce the circuit footprint while retaining the device reliability, high yield, and uniformity. Furthermore, the MGT design can implement memory without the need for any additional conducting layer and realize 3D control to effectively mimic the artificial synaptic behaviors. The proposed design has the potential to be an alternative to logic gates and RAM, providing a practical solution for incorporating high-density devices in standard Si circuits and advanced flexible electronics for AI applications.

Results

Logic gate implementation

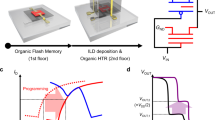

For digital circuits, information levels are expressed by state 1 (level high) and state 0 (level low), which are defined by voltage signals ≥0.7 V and <0.7 V, respectively. The three-dimensional architectures of the one-transistor design are shown in Fig. 1 and compared to the complementary metal-oxide-semiconductor (CMOS) counterparts. As shown in Fig. 1a, the one-transistor logic NOT gate is one transistor fewer than the CMOS one. The main difference is that the additional channel electrode is designed to act as the output. A scanning electron microscope (SEM) image of the cross-section of the Si-based one-transistor design is shown in Fig. 1b. For conventional FinFETs, multiple manufacturing processes are required to fabricate the gates with complex structures. In addition, the roughness of the FinFET gate edges and the shape of the fins exert significant influence on the device performance12. In contrast, the devices proposed in this study are easier to manufacture, and the proposed design could also be adapted into the FinFET or even more advanced technology nodes to enable versatile functionalities.

a Logic NOT gates comparing the conventional CMOS design (left) and the one-transistor design (right; TG: top gate). b Cross-section SEM view of the device fabricated using the Si-based SOI 130 nm technology node (scale bar: 500 nm). c One-transistor logic AND/OR gate in comparison to the six-transistor logic gates. The first input, Input1, is the voltage on the top gate, VGS, and the voltage on the side gate (SG), VSG, is the second input, Input2. The voltage on the drain electrode is VDS, and the channel current is IDS. The additional electrode connected directly to the channel represents the output of the logic gates and is the control gate of the memory. The voltage measured from the output is denoted as Output, and the voltage applied on the control gate is VCG22.

As shown in Fig. 1c, the one-transistor logic OR and logic AND gates can also be implemented with five transistors fewer than the typical CMOS counterparts. The processing steps of the top-gate structure are the same as the typical Si-based transistor, except an additional channel electrode is added to the channel. This design, with the additional electrodes connected to the channel, can be employed to implement not only logic gates but also memory and artificial synaptic behaviors, as will be discussed in later sections. The additional electrode(s) acts as both the output of the logic gates and the control gate to store charges in the memory. When the device performs as an artificial synapse, this additional electrode can control and program synaptic behavior as a standard gate.

We demonstrate that various logic gate functions that normally require 2 to 6 transistors can be implemented using only 1 transistor with an additional electrode as the output added to the channel9. For instance, for the function of logic NAND gate, Output will be 1 when either Input1 (input voltage on the top gate) or Input2 (input voltage on the side gate) is in state 0 (level low), and Output will be 0 when and only when both Input1 and Input2 are in state 1 (level high). The function of logic NAND is implemented in this one-transistor design as shown in Table 1, in which the top gate serves as Input1, the side gate acts as Input2, and the additional electrode delivers the Output signal. According to the masks, this design footprint is proved to be reduced by over 60% of the conventional 6-transistor logic NAND gate footprint implemented by the same technology node (detailed analysis of circuits footprint can be found in Supplementary Fig. 1). In this paper, the technology node is SOI 130 nm, in which the lower working voltage is ~1.2 V and the higher working voltage is 3 V. The vertically stacked layers are Si/dielectric/top gate, respectively, from the bottom to the top. A recent publication claimed that they simplified two transistors into a single transistor15. However, the logic NAND proposed in that publication needs two transistors, whereas the logic NAND in this study demands only one transistor. Here, our one-transistor design with additional electrodes can simplify the 2-to-6-transistor logic gates into a single-transistor system (Fig. 1). In the proposed structure, the additional channel electrodes can be one or more depending on the desired application. The logic NOT gate only needs the top gate as the input. When the side gate or a bottom gate is added as an additional input, two or more input logic gates can be implemented. The area reduction at this device level in comparison with the conventional device or CMOS circuit technology that performs the same logic NOT gate function is ~73%.

When side-gate is not used, according to the measurement and experimental results shown in Fig. 2a, Output could be in state 1 when Input1 is in state 0 initially. Then, Output decreases when Input1 increases, and ultimately, Output could be in state 0 when Input1 is in state 1. This is a function like logic NOT. Hence, without changing the foundry line, the proposed Si-based design can employ a single transistor to achieve the typical logic gate functionalities that previously required multiple, i.e., two to six or even more, transistors. Again, this reduces the logic gate footprint by about 70% (logic NOT gate) or more (other logic gates) according to the lithography masks.

Please kindly note that the simulation results are used to describe the mechanisms qualitatively and the two input gates functions and effects are considered to be the same to those of the one input gate. a Measured input gate voltage vs. output voltage. VDS = 0.9 V. b Mechanism comparison of logic NOT for both the MGT structure and the conventional CMOS (complementary Metal Oxide Semiconductor transistors) structure. c–f Simulation results of voltage distribution in the one-transistor design. c, e The input gate voltages turn the channel off, and the gate-to-drain voltage enables the high voltage region on the drain edge to extend from the drain to the output for logic NOT and logic NAND, respectively. d, f The input gate voltage turns the channel on so that the output voltage is drawn down by the source voltage, for logic NOT and logic NAND, respectively.

The mechanism of the logic NOT gate implementation on the one-transistor structure is as follows. In Fig. 2b, the conventional logic NOT gate requires a PMOS transistor to lift up the output to be state 1 and another NMOS transistor to pull down the output to be state 0; while the one-transistor logic NOT gate only needs the partial channel to perform the lift-up and pull-down functions. The transistor generally operates in the voltage region not much higher than the subthreshold voltage region with low currents and voltages. Hence, the main advantage of the CMOS logic NOT gate, i.e., low static-state power consumption, can be ensured in principle through careful design and control. The power consumption advantage of the one-transistor logic NOT over the one-resistor and one-transistor logic NOT is as follows. If the gate voltage is not applied, the gate-to-drain voltage does not exist, and the drain-to-output channel should not be turned on. In this case, the output could not connect to the drain voltage and be lifted up to state 1, unlike in the one-resistor and one-transistor logic NOT, where the one resistor is always conductive to lift up the output. Therefore, the low VDS and VGS here also ensure a low static power consumption.

Simulations were performed to investigate the mechanism behind the implementation of logic NOT using the proposed configuration. When the top gate voltage, i.e., Input1, is 0 V, a saturated region can be observed along the drain edge (Fig. 2c) because of the gate-to-drain voltage. Such a saturation region could enable the high Output state owing to the output linkage to the high drain voltage. On the other hand, when Input1 is set to 1 V, the gate voltage can turn on the channel and the drain voltage is shared by the channel instead of being limited in the drain-to-output channel (Fig. 2d). As a result, a low voltage state is read as Output. This facilitates the implementation of the logic NOT gate.

For the logic NAND function, as shown in Fig. 2e, when both inputs are 0, the channel is off, but the drain-to-output is on so that Output is 1; when one of the inputs, Input1 or Input2, is 1 and the other is 0, the inputs could not turn on the whole channel; when both of the inputs, Input1 or Input2 are 1 and they turn on the whole channel, shown in Fig. 2f, the drain voltage is shared by the whole channel instead of being limited in the drain-to-output channel. The Output voltage is drawn down to 0 by the source voltage of 0 V. These electrical characteristics fulfill the requirement of the logic NAND.

The one-transistor structure can also execute logic AND and logic OR based on a different mechanism. When the output electrode is designed far enough away from the electric field on the drain edge, the output is not connected to the drain when the inputs are low initially. When the input(s) is high enough, the channel is turned on like a resistor and the output voltage shares VDS distributed along the channel, which is proportional to the output-to-source resistance and the drain current. When the inputs are high enough to increase the drain current over the threshold, the output is no longer lower than 0.7 V and turns to state 1. Based on this design, the logic AND and OR functions can be realized using different operating voltages. The detailed data of AND/OR can be found in Supplementary Fig. 2. When the drain voltage is lower, logic AND is obtained since both inputs need to be high to make the output in state 1. When the drain voltage is higher, the drain current is higher so that logic OR could be obtained in the same design since either of the inputs could be high enough to tune the output to be 1.

Memory implementation

As a versatile feature of the one-transistor design, memory function can also be implemented in the same device. As described in Fig. 3, compared to the existing memory designs, including memristors, magnetic RAMs, phase-change RAMs, and ferroelectric RAMs21,22,23,24,25,26,27,28,29, the proposed one-transistor memory device structure does not involve any capacitors, resistors, or advanced materials. Besides the much simpler structure, the MGT design possesses superior properties of shorter reading and writing time (both ~5 ns), as shown in Supplementary Fig. 3. In addition, in terms of manufacture, the proposed device is scalable and compatible with a wide range of Si-based applications.

DRAM needs one capacitor and one transistor, FeRAM, MRAM, and PRAM need dedicated materials such as ferroelectrics to introduce the capacitor effect, which deviates from the silicon foundry processing and challenges the mass production. Our design involves only one transistor with no additional materials and compatibility with the Si foundry lines.

A typical memory action is the shift of the transfer curve with the threshold voltage27. As shown in Fig. 4a, the drain current IDsat at VDS = 1.5 V and VGS = 2 V is initially 205.06 μA. After writing, IDsat increases by 36.21 μA, while it decreases by 18.54 μA after erasing. The one-transistor memory also exhibited a retention time longer than 15 s, which could be much longer than the standard retention time of DRAM of ~64 ms (Fig. 4b). The retention time could be varied from about 15 ns to over 1500 s by adjusting the programming conditions such as the voltage amplitude and programming time. The adjustable and relatively long retention time suggests the potential of the one-transistor design to be an alternative to the present memory devices. In comparison, DRAM has a much larger footprint containing one transistor and one capacitor27. Besides, the one-transistor design here does not require additional materials such as ferroelectric materials and is compatible with the foundry line processing. As another key parameter, the current on/off ratio (i.e., state 1: state 0) exceeds 3, which is sufficiently high to define the on/off states. The memory functions of the design suggest usage as the unit cell in an artificial neural network. It is worth noting that the kinds of logic in the artificial neural network generally have current as the output, which is analog circuits with matrix multiplying and adding functions. They cannot perform the functions of digital circuits including providing the I/O signal and require resistors or extra circuits to acquire the voltage output. The logic we proposed here has the voltage as the output directly, thereby proving applications beyond the capabilities of the logic in an artificial neural network. While the design here has the memory and artificial synaptic behaviors so that it could be used as the logic unit cell in the artificial neural network, it could also be used as the logic gates in digital circuits, including oscillators, clocks, triggers, and so on. More studies should be performed to further improve the characteristics of the devices such as reducing the current by adjusting the voltages or increasing the channel width.

a Transfer characteristics of the device before and after programming. b Retention data of the memory states. The programming time is 5 ms, which is limited by the measurement setup and can be further reduced. c The operation mechanism diagram of the one-transistor design for the reading process. d The operation mechanism diagram of the one-transistor design for programming process.

The mechanism of the memory operation is based on the effect of the channel/additional channel electrode junction on charge storage, as illustrated in Fig. 4c, d. When the control gate voltage is not applied, there is no voltage applied on the junction between the channel and the control gate, and the junction is in equilibrium. In this case, the Fermi level in the junction depletion region is flat, as shown in the energy band diagram in Fig. 4c. When the transistor is turned on and VGS is higher than VCG, the voltage difference between VCG and VGS leads to charge injection in the junction between the channel and the control gate. Consequently, the Fermi level in the junction depletion region becomes bend, resulting in the charges trapping in the junction (Fig. 4d). Finally, when VCG is released, the junction moves to another balance, and the energy band bending disappears, which terminates the charge injection stops and the decreased channel current accomplishes the erasing action.

Implementation of artificial synapses

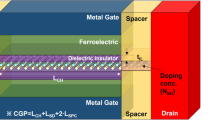

Typical artificial synaptic behaviors, such as an artificial synaptic transmission behavior excitatory postsynaptic current (EPSC), can also be implemented using the Si-based one-transistor design proposed in this work30,31. In a synaptic transmission event, stimulation from the presynaptic membrane induces a change in the electrical signal of the postsynaptic membrane, which is called EPSC or inhibitory postsynaptic current30,31. The design here is different from previously reported ones (Fig. 5). In particular, conventional designs require additional layers, different procedures, or different materials incompatible with the Si-based foundry lines32,33,34,35,36,37,38,39,40. Figure 5a shows a previously reported structure based on a transistor with top and bottom gates, which requires two dielectrics33. Figure 5b has an additional layer compared to a standard transistor34,35,36. Figure 5c shows a bottom-gate structure, which is not compatible with the top-gate Si-based foundry line processing37,38,39,40. Figure 5d shows a side-gate structure, which has a large footprint, not favored by the scaling-down requirement2. Finally, Fig. 5e shows the design proposed in this work, which is a top-gate structure compatible with Si-based foundry lines. The one-transistor design here contains fewer material layers than those shown in Fig. 5a, b and a smaller footprint than that shown in Fig. 5d. It is also different from the bottom-gate structure shown in Fig. 5c, in terms of compatibility with the Si foundry line process. Moreover, an additional control gate can be employed to control and program the artificial synaptic transmission behaviors. This improves the controllability of the device when compared to the previous structures with typical gates.

a–d Previously published artificial synaptic transistor structures22, including a transistor with bottom gate and top gate, b transistor with additional channel materials or layers, c transistor with the bottom gate, and d transistor with multiple side gates and a large footprint. e Structure of the proposed one-transistor artificial synaptic device, which does not contain any additional dielectric, conducting layer or side gate. f Effect of control gate voltage VCG on the artificial synaptic transmission behavior. g Weight modulations of the artificial synaptic structures with PPF and potentiation (the curves in blue, red, and black are the top gate voltage, the control gate voltage, and IDS, respectively).

The voltages controlling the channel current directly determines the shape and amplitude of the EPSC (Fig. 5f). When the voltage changes, the peak value of the EPSC is evidently adjusted. The dependence of EPSC on the channel voltages suggests that the electrode voltages which control the channel current of the updated design can be used to program the synaptic behaviors of the artificial synapses. The working mechanism is as follows. Neurons and synapses are two basic computational units in the brain, whose plasticity transmissions depend on the existence of charges such as ions. The plasticity transmission of the neurons and synapses depends on the existence of ions diffusion inside the neuron initiated with the opening of voltage-gated calcium ion channels, through the synaptic gap and inside the post-synaptic cell. The proposed one-transistor structure here has the channel-control gate junction and channel components, and the mechanism of channel conducting also depends on the charge transport and is similar to the functions of neurons and synapses. Hence, the charging and discharging of the channel-control gate junction can mimic the transmission of synapse and neuron signals31,32,34. In our previous published work on the standard bottom-gate transistors for the artificial synaptic devices, we have proposed that the terminal voltages such as gate voltages and drain voltages could qualitatively adjust the artificial synaptic behaviors for a standard transistor41. This multi-terminal-design-induced VCG effect, in addition to the effect of the typical gate (bottom gate, top gate, or side gate) voltages, could impact the artificial synaptic behaviors31,42. The multi-terminal structure improves the controllability of the device when compared to the previous structures with only typical gates (bottom gate, top gate, or side gate). Moreover, while conventional electronic device designs generally have only two- or three-terminal to mimic artificial synapses in 2D, the design here has multiple-terminal (with one or more channel electrodes) to achieve the functions in 3D-terminals design and 3D control31,32. As shown in Fig. 5g, additional synaptic weight modulation such as potentiation could be achieved by the combinations of the top gate and control gate voltage42,43. The base for the drain current increases after the pulse stimulations, which suggests a potentiation. The typical synapse behaviors such as paired-pulse facilitation (PPF) could be observed as shown in Supplementary Fig. 442,43. The stimulated current signal peak increases after the pulse stimulation, which corresponds to PPF. This means the artificial synapse ability of this design could be adjusted and enhanced more effectively with reduced overall space of circuits. The one-transistor artificial synapse with 3D terminals and 3D control has the potential to be adapted with 3D circuits for the development of next-generation neuromorphic devices.

Conclusion

In summary, a Si-based one-transistor design with an additional electrode at the channel was proposed to solve the difficult issue of scaling down modern circuits for miniaturization and faster mass data processing (a smaller circuit implies shorter distances for charge-carrier transport). A single transistor was used to implement logic gates that previously used two to six transistors and memories that previously used multiple devices. This design could provide the combined functionality of logic gates, memory, and artificial synapses. The multi-terminal design other than the conventional two- or three-terminal devices could realize the control of the artificial synapses mimic in 3D with SOI process. The one-transistor design could be implemented using Si foundry lines without requiring additional processing steps or materials, suggesting that it is a promising candidate for immediate and widespread applications. It should be emphasized that Si is not the only semiconductor material that can be used here; the process outlined here can be used with other semiconductor materials, advanced processing, and substrate elements. The performance of single transistors can be further improved using other materials. This work is expected to be of interest to the downsizing/miniaturization of modern circuits and flexible electronics.

Methods

Device fabrication

The proposed design was fabricated using a foundry-standard silicon-on-insulator (SOI) 130-nm technology, with a channel length of 130–650 nm. The active region (ACT) was defined initially by implantation on a 200-mm-diameter wafer from SOITEC; the N-well region was implanted afterward. Then, the dielectrics of the devices were deposited, followed by the deposition of the polysilicon gate sections. The thickness of the top Si film was about 100 nm, gate oxide about 6.8 nm, and buried oxide about 145 nm. Next, n+ doping in the range of 1018–1020 cm−3 was performed to form the drain and source implantation regions. Subsequently, the salicide block region was fabricated; thereafter, the poly and ACT contacts were created. Finally, metal layers and vias were formed, and the packaging of our samples employed a 24-pin bonding technology. The designs require no extra mask numbers or steps than a standard process. The additional electrode region is formed during the processes. Circuits based on such device designs could be further investigated for logic circuits and memory array applications, etc.

Electrical characterizations

All electrical characterizations of the one-transistor device were performed using a Keithley 4200 source measurement (Keithley Corporation, USA) in a dark chamber under atmospheric pressure and room temperature. The memory programming time was 5 ms, which is limited by the measurement setup. Multiple measurements were performed on different samples to confirm the reliability of the device functions. All the data were directly exported from the measurement units without any modification.

Simulation

Simulations of the proposed one-transistor system were performed according to the principles of semiconductor theory using COMSOL (Fig. 2c, d, and Supplementary Fig. 5). The simulations were repeated ten times with different input voltages by entering the semiconductor module. For demonstration, the overall material used was a silicon substrate with a length of 3 μm and a height of 0.7 μm; it was n-doped to a concentration of 1017 cm−3. The material properties of silicon were derived from the material library in COMSOL. The thin insulator gate had a height of 0.7 μm and a length of 0.7–2.3 μm. The source and drain regions had heights of 0.7 μm and lengths of 0–0.5 μm and 2.5–3 μm, respectively, and they were selected for n+ doping with a concentration of 1020 cm−3. The Shockley–Read–Hall model was used for simulating trap-assisted recombination. Finally, the grid was divided, and different parameters were selected for calculations in the “study” mode to obtain the results.

Data availability

Data that support the findings within this work are available from the corresponding author upon reasonable request.

References

Chauhan, Y. S. et al. FinFET Modeling for IC Simulation and Design Using the BSIM-CMG Standard (Academic Press, 2015).

Choi, W. Y. et al. Side-gate design optimization of 50 nm MOSFETs with electrically induced source/drain. Jpn. J. Appl. Phys. 41, 2345–2347 (2002).

Dai, M. & Dai, N. Logic circuit function realization by one transistor. Nano Lett. 12, 5954–5956 (2012).

Huang, Q. The International Technology Roadmap for Semiconductors, ITRS. China lntegr. Circuit 9, 25–45 (2014).

Lee, H. S. et al. Coupling two-dimensional MoTe2 and InGaZnO thin-film materials for hybrid PN junction and CMOS inverters. ACS Appl. Mater. Interfaces 9, 15592–15598 (2017).

Ma, T. P. Making silicon nitride film a viable gate dielectric. IEEE Trans. Electron Devices 45, 680–690 (1998).

Taur, Y. & Ning, T. H. Fundamentals of Modern VLSI Devices (Cambridge University Press, 2002).

Colinge, J.-P. FinFETs and Other Multi-Gate Transistors (Springer, 2008).

Zhu, C. et al. Stretchable temperature-sensing circuits with strain suppression based on carbon nanotube transistors. Nat. Electron. 1, 183–190 (2018).

Choi, Y.-K. et al. Ultra-thin body SOI MOSFET for deep-sub-tenth micron era. Int. Electron Devices Meeting 21, 245–255 (1999).

Heo, J. S. et al. Thread-like CMOS logic circuits enabled by reel-processed single-walled carbon nanotube transistors via selective doping. Adv. Mater. 29, 1701822 (2017).

Tang, J. et al. Flexible CMOS integrated circuits based on carbon nanotubes with sub-10 ns stage delays. Nat. Electron. 1, 191–196 (2018).

Gao, G. et al. Tunable tribotronic dual-gate logic devices based on 2D MoS2 and black phosphorus. Adv. Mater. 30, 1705088 (2108).

Gao, Y. et al. Multifunctional mixed-dimensional MoS2-CuO junction field-effect transistor for logic operation and phototransistor. Adv. Electron. Mater. 5, 1800976 (2019).

Liu, C. et al. Small footprint transistor architecture for photoswitching logic and in situ memory. Nat. Nanotechnol. 14, 662–667 (2019).

Ofek, N. et al. Extending the lifetime of a quantum bit with error correction in superconducting circuits. Nature 536, 441–445 (2016).

Weidt, S. et al. Trapped-ion quantum logic with global radiation fields. Phys. Rev. Lett. 117, 220501 (2016).

Genot, A. J. et al. High-resolution mapping of bifurcations in nonlinear biochemical circuits. Nat. Chem. 8, 760–767 (2016).

Siuti, P. et al. Synthetic circuits integrating logic and memory in living cells. Nat. Biotechnol. 31, 448–452 (2013).

Schäfer, V. M. et al. Fast quantum logic gates with trapped-ion qubits. Nature 555, 75–78 (2018).

Dai, C. et al. Ultrathin flexible InGaZnO transistor for implementing multiple functions with a very small circuit footprint. Nano Res. 14, 232 (2021).

Qi, S. et al. Bottom-gate approach for all basic logic gates implementation by a single-type IGZO-based MOS transistor with reduced footprint. Adv. Sci. 7, 1901224 (2020).

Dai, M. et al. A memory structure with different control gates. Adv. Electron. Mater. 4, 1800186 (2018).

Fortunato, E. et al. Oxide semiconductor thin-film transistors: a review of recent advances. Adv. Mater. 24, 2945–2986 (2012).

Fuller, E. J. et al. Parallel programming of an ionic floating-gate memory array for scalable neuromorphic computing. Science 364, 570–574 (2019).

Linares-Barranco, B. Memristors fire away. Nat. Electron. 1, 100–101 (2018).

Liu, C. et al. A semi-floating gate memory based on van der Waals heterostructures for quasi-non-volatile applications. Nat. Nanotechnol. 13, 404–410 (2018).

Cao, Q. et al. Nonvolatile multistates memories for high-density data storage. ACS Appl. Mater. Interfaces 12, 42449–42471 (2020).

Martins, R. et al. Selective floating gate non-volatile paper memory transistor. Phys. Stat. Sol. (RRL) 3, 308–310 (2009).

Meena, J. S. et al. Overview of emerging nonvolatile memory technologies. Nanoscale Res. Lett. 9, 526 (2014).

Roy, K. et al. Towards spike-based machine intelligence with neuromorphic computing. Nature 575, 607–617 (2019).

Sun, F. et al. Flexible artificial sensory systems based on neuromorphic devices. ACS Nano https://doi.org/10.1021/acsnano.0c10049 (2021).

Beom, K. et al. Single- and double-gate synaptic transistor with TaOx gate insulator and IGZO channel layer. Nanotechnology 30, 025203 (2019).

Zhang, S. et al. Selective release of different neurotransmitters emulated by a p-i-n junction synaptic transistor for environment-responsive action control. Adv. Mater. 33, 2007350 (2021).

Ren, Y. & Wu, M. 0D/1D organic ferroelectrics/multiferroics for ultrahigh density integration: helical hydrogen-bonded chains, multi-mode switching, and proton synaptic transistors. J. Chem. Phys. 154, 044705 (2021).

Li, Q. et al. Flexible organic field-effect transistor arrays for wearable neuromorphic device applications. Nanoscale 12, 23150–23158 (2020).

Yang, Y. et al. Exploration of the proton conduction behavior in natural neutral polysaccharides for biodegradable organic synaptic transistors. J. Mater. Chem. C 8, 16542–16550 (2020).

Yang, Q. et al. High-performance organic synaptic transistors with an ultrathin active layer for neuromorphic computing. ACS Appl. Mater. Interfaces 13, 8672–8681 (2021).

Wan, H. et al. Flexible carbon nanotube synaptic transistor for neurological electronic skin applications. ACS Nano 14, 10402–10412 (2020).

Ou, Q. et al. Degradable photonic synaptic transistors based on natural biomaterials and carbon nanotubes. Small 17, 2007241 (2021).

Dai, M. et al. Realization of tunable artificial synapse and memory based on amorphous oxide semiconductor transistor. Sci. Rep. 7, 10997 (2017).

Yu, J.-M. et al. All-solid-state ion synaptic transistor for wafer-scale integration with electrolyte of a nanoscale thickness. Adv. Func.Mater. 7, 2010971 (2021).

Seo, S. et al. Artificial van der Waals hybrid synapse and its application to acoustic pattern recognition. Nat. Comm. 11, 3936 (2020).

Acknowledgements

We are grateful for the support of Shanghai Industrial µTechnology Research Institute for facilitating the SOI process technology node fabrication and all members of the RA sections in HHGrace Semiconductor Manufacturing Corporation for providing the SEM figure. We also thank Professor T. P. Ma (Yale University), Wenwei Yang, Bain Yu, Yi Tian, Yi Shan, Yuejun Zhang, and Haibin Yu (Ningbo University) for their valuable feedback and helpful discussions. This work was supported by the National Natural Science Foundation of China (Grant No. U20A20209), Zhejiang Provincial Natural Science Foundation for Distinguished Young Scholar (Grant No. LR17F040007), Ningbo Natural Science Foundation of China (Grant No. 61574147), the Instrument Developing Project of the Chinese Academy of Sciences (Grant No. YJKYYQ20180021), and Research Foundation of Strategic Priority Research Program of Chinese Academy of Sciences (XDA18030100). Professor Tom Wu acknowledges the UNSW SHARP Project (RG163043). Mr. Shaocheng Qi helped with the experimental results.

Author information

Authors and Affiliations

Contributions

M.D. proposed the one-transistor design and examined the device performance. Y.D. and T.W. helped supervise the experiments. All authors M.D., Z.S., C.-H.L., Y.D., T.W., and J.C. commented on the work and contributed to writing the paper.

Corresponding authors

Ethics declarations

Competing interests

The authors declare no competing interests.

Peer review

Peer review information

Communications Materials thanks Tukaram Dattatray Dongale and the other, anonymous, reviewer(s) for their contribution to the peer review of this work. Primary Handling Editor: Aldo Isidori.

Additional information

Publisher’s note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Supplementary information

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made. The images or other third party material in this article are included in the article’s Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Dai, M., Song, Z., Lin, CH. et al. Multi-functional multi-gate one-transistor process-in-memory electronics with foundry processing and footprint reduction. Commun Mater 3, 41 (2022). https://doi.org/10.1038/s43246-022-00261-3

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s43246-022-00261-3

- Springer Nature Limited

This article is cited by

-

Inorganic Halide Perovskite Quantum Dots: A Versatile Nanomaterial Platform for Electronic Applications

Nano-Micro Letters (2023)