Abstract

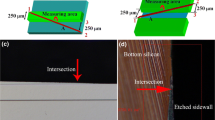

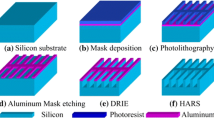

Although trench gate and super-junction technology have micro-trench problems when applied to the SiC process due to the material characteristics. In this paper, area effects are analyzed from the test element group with various patterns and optical proximity correction (OPC) methods are proposed and analyzed to reduce micro-trenches in the SiC trench etching process. First, the loading effects were analyzed from pattern samples with various trench widths (Wt). From experiments, the area must limited under a proper size for a uniform etching profile and reduced micro-trenches because a wider area accelerates the etch rate. Second, the area effects were more severely unbalanced at corner patterns because the corner pattern necessarily has an in-corner and out-corner that have different etching areas to each other. We can balance areas using OPC patterns to overcome this. Experiments with OPC represented improved micro-trench profile from when comparing differences of trench depth (Δdt) at out corner and in corner. As a result, the area effects can be used to improve the trench profile with optimized etching process conditions. Therefore, the trench gate and super-junction pillar of the SiC power MOSFET can have an improved uniform profile without micro-trenches using proper design and OPC.

Similar content being viewed by others

References

T. Nakamura, Y. Nakano, M. Aketa, R. Nakamura, S. Mitani, H. Sakairi, and Y. Yokotsuji, Proceeding of IEEE International Electron Devices Meeting, pp. 26.5.1-26.5.3, IEEE, Washington, DC, USA (2011).

L. Yu, Ph.D. Simulation, Modeling and Characterization of SiC Devices, pp. 7–23, The State University of New Jersey, New Brunswick, USA (2010).

D. Ruixue, Y. Yintang, and H. Ru, Journal of Semiconductors, 30, 016001 (2009).

H. Oda, P. Wood, H. Ogiya, S. Miyoshi, and O. Tsuji, Proc. CS MANTECH, pp. 125–128, CS MANTECH, Scottsdale, Arizona, USA (2015).

D. Jung, S. G. Cho, T. Moon, and H. Sohn, Electron. Mater. Lett. 12, 17 (2016).

K. H. Jun, B. J. Kim, and J. S. Kim, Electron. Mater. Lett. 11, 871 (2015).

Z. Cao, Q. Huang, C. Zhao, and Q. Zhang, Electron. Mater. Lett. 12, 742 (2016).

J. Karttunen, J. Kiihamäkia, and S. Franssilab, Proc. SPIE, SPIE, 4174, 90 (2000).

K. Paul Muller, K. Roithner, and H.-J. Timme, Microelectron. Eng. 27, 457 (1995).

C. J. Mogab, J. Electrochem. Soc. 124, 1262 (1977).

E. S. G. Shaqfeh and C. W. Jurgensen, J. Appl. Phys. 66, 4664 (1989).

K. P. Giapis, G. R. Scheller, R. A. Gottscho, W. S. Hobson, and Y. H. Lee, Appl. Phys. Lett. 57, 983 (1990).

W. Pilz, J. Janes, K. P. Muller, and J. Pelka, Proc. SPIE: Advanced Techniques for Integrated Circuit Processing, 1392, 84 (1991).

J. W. Coburn and H. F. Winters, Appl. Phys. Lett. 55, 2730 (1989).

J. Pelletier, J. Phys. D: Appl. Phys. 20, 858 (1987).

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Kyoung, S., Jung, ES. & Sung, M.Y. Investigation of the layout and optical proximity correction effects to control the trench etching process on 4H-SiC. Electron. Mater. Lett. 13, 368–372 (2017). https://doi.org/10.1007/s13391-017-1721-z

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s13391-017-1721-z