Abstract

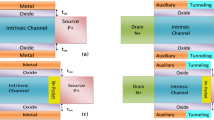

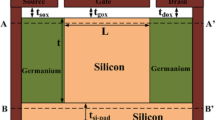

In this manuscript, a novel physically doped single gate F-shaped tunnel FET is simulated and optimized. The designed configuration is well optimized and analyzed for different source thickness, source length, drain length with different lateral tunneling lengths between the source edge and gate dielectric. Also, we optimized some stand-points like threshold voltage, ION to IOFF current ratio, ambipolar conduction range, sub-threshold swing and various capacitance to rectify the analog/RF performance of single gate F-shaped TFET. Regarding this, we concurrently optimize the lateral tunneling length between source and gate with optimization of source thickness. The variation in lateral tunneling length, the potential and strength of electric field at fixed Vgs voltage is varied which leads to effective change in the ON-current, average sub-threshold swing, and turn ON-voltage. Another side, as well as the source thickness vary, the electric field variation takes place near the edge of source, which leads to variation in the ON-current and ON-voltage. The performance parameters of single gate F-TFET is compared with single gate L-TFET, which is the incentive of this submitted work. The optimized single gate F-TFET have 0.30 V turn ON-voltage with 7.4 mV/decade average sub-threshold swing and high Ion/Ioff ratio approx 1013. Besides, a significant reduction in parasitic capacitance is beneficial to enhanced RF performance with better controllability on channel.

Similar content being viewed by others

Data Availability

The data and material concerned to the manuscript may be made available on request.

References

Avci UE, Morris DH, Young IA (2015) Tunnel field-effect transistors prospects and challenges. IEEE J Electron Devices Soc 3(3):88–95

Ionescu AM, Riel H (2011) Tunnel field-effect transistors as energy-efficient electronic switches. Nature 479(7373):329–337

Boucart K, Ionescu AM (2007) Double-gate tunnel fet with high-k gate dielectric. IEEE Trans Electron Devices 54(7):1725–1733

Toh E-H, Wang GH, Chan L, Samudra G, Yeo Y-C, physics Device (2007) guiding principles for the design of double-gate tunneling field effect transistor with silicon-germanium source heterojunction. Appl Phys Lett 91(24):243505

Raad BR, Sharma D, Kondekar P, Nigam K, Yadav DS (2016) Drain work function engineered doping-less charge plasma tfet for ambipolar suppression and rf performance improvement: a proposal, design, and investigation. IEEE Trans Electron Devices 63(10):3950–3957

Mallik A, Chattopadhyay A, Guin S, Karmakar A (2013) Impact of a spacer–drain overlap on the characteristics of a silicon tunnel field-effect transistor based on vertical tunneling. IEEE Trans Electron Devices 3(60):935–943

Yadav DS, Sharma D, Raad BR, Bajaj V (2016) Dual workfunction hetero gate dielectric tunnel field-effect transistor performance analysis. In: 2016 International conference on advanced communication control and computing technologies (ICACCCT),. IEEE, pp 26–29

Villalon A, Le Carval G, Martinie S, Le Royer C, Jaud M-A, Cristoloveanu S (2014) Further insights in tfet operation. IEEE Trans Electron Devices 61(8):2893–2898

Garg S, Saurabh S (2020) Exploiting within-channel tunneling in a nanoscale tunnel field-effect transistor. IEEE Open J Nanotechnol 1:100–108

Abdi DB, Kumar MJ (2014) In-built n+ pocket pnpn tunnel field-effect transistor. IEEE Electron Device Letters 35(12):1170–1172

Tirkey S, Raad BR, Gedam A, Sharma D (2018) Junction-less charge plasma tfet with dual drain work functionality for suppressing ambipolar nature and improving radio-frequency performance. Micro Nano Lett 13(1):18–23

Cao W, Yao C, Jiao G, Huang D, Yu H, Li M-F (2011) Improvement in reliability of tunneling field-effect transistor with pnin structure. IEEE Trans Electron Devices 58(7):2122–2126

Narang R, Saxena M, Gupta R, Gupta M (2012) Assessment of ambipolar behavior of a tunnel fet and influence of structural modifications. JSTS: J Semicond Technol Sci 12(4):482–491

Yun S, Oh J, Kang S, Kim Y, Kim JH, Kim G, Kim S (2019) F-shaped tunnel field-effect transistor (tfet) for the low-power application. Micromachines 10(11):760

Fossum J, Yang J-W, Trivedi V (2003) Suppression of corner effects in triple-gate mosfets. IEEE Electron Device Lett 24(12):745–747

Manual AU (2016) Silvaco international inc, Santa Clara, Ca USA

Tirkey S, Sharma D, Raad BR, Yadav DS (2017) A novel approach to improve the performance of charge plasma tunnel field-effect transistor. IEEE Trans Electron Devices 65(1):282–289

Imenabadi RM, Saremi M, Vandenberghe WG (2017) A novel pnpn-like z-shaped tunnel field-effect transistor with improved ambipolar behavior and rf performance. IEEE Trans Electron Devices 64 (11):4752–4758

Tirkey S, Yadav DS, Sharma D (2017) Controlling ambipolar behavior and improving radio frequency performance of hetero junction double gate tfet by dual work-function, hetero gate dielectric, gate underlap: Assessment and optimization. In: 2017 International conference on information, communication, instrumentation and control (ICICIC). IEEE, pp 1–7

Debnath RG, Baruah K, Baishya S (2020) Dc and analog/rf performance analysis of gate extended u-shaped channel tunnel field effect transistor. Microsyst Technol 26(9):2793–2799

Pandey C, Dash D, Chaudhury S (2020) Improvement in analog/rf performances of soi tfet using dielectric pocket. Int J Electron 107(11):1844–1860

Yadav DS, Sharma D, Raad BR, Bajaj V (2016) Impactful study of dual work function, underlap and hetero gate dielectric on tfet with different drain doping profile for high frequency performance estimation and optimization. Superlattices Microstruct 96:36–46

Shekhar D, Raman A (2020) Design and analysis of dual-gate misalignment on the performance of dopingless tunnel field effect transistor. Appl Phys A 126:1–9

Guenifi N, Rahi S, Larbi M (2020) Suppression of ambipolar current and analysis of rf performance in double gate tunneling field effect transistors for low-power applications. Int J Nanoparticles Nanotech 6:033

Yadav DS, Raad BR, Sharma D (2016) A novel gate and drain engineered charge plasma tunnel field-effect transistor for low sub-threshold swing and ambipolar nature. Superlattices Microstruct 100:266–273

Abraham N, James RK (2020) An improved tunnel field-effect transistor with an l-shaped gate and channel. J Comput Electron 19(1):304–309

Saurabh S, Kumar MJ (2010) Novel attributes of a dual material gate nanoscale tunnel field-effect transistor. IEEE Trans Electron Devices 58(2):404–410

Shekhar D, Raman A (2021) Tweaking the performance of dopingless nano-tfet with misaligned sandwiched dual-gate structure. Silicon 1–11

Joshi T, Singh B, Singh Y (2020) Controlling the ambipolar current in ultrathin soi tunnel fets using the back-bias effect. J Comput Electron 19(2):658–667

Kim SW, Kim JH, Liu T-JK, Choi WY, Park B-G (2015) Demonstration of l-shaped tunnel field-effect transistors. IEEE Trans Electron Devices 63(4):1774–1778

Kao K-H, Verhulst AS, Vandenberghe WG, Soree B, Magnus W, Leonelli D, Groeseneken G, De Meyer K (2012) Optimization of gate-on-source-only tunnel fets with counter-doped pockets. IEEE Trans Electron Devices 59(8):2070–2077

Anghel C, Chilagani P, Amara A, Vladimirescu A (2010) Tunnel field effect transistor with increased on current, low-k spacer and high-k dielectric. Appl Phys Lett 96(12):122104

Saurabh S, Kumar MJ (2016) Fundamentals of tunnel field-effect transistors. CRC press

Yang Z (2016) Tunnel field-effect transistor with an l-shaped gate. IEEE Electron Device Lett 37(7):839–842

Zhu Y, Hudait MK (2013) Low-power tunnel field effect transistors using mixed as and sb based heterostructures. Nanotechnol Rev 2(6):637–678

Acknowledgements

The authors would like to thank Dr. Dip Prakash Samajdar from Department of Electronics and Communication Engineering, PDPM Indian Institute of Information Technology, Design & Manufacturing, Jabalpur, Madhya Pradesh, India for providing valuable suggestions and support to carry out this research work.

Author information

Authors and Affiliations

Contributions

– Prabhat Singh: Conceptualization, data curation, formal analysis, methodology, investigation, writing – original draft.

– Dharmendra Singh Yadav: Supervision, validation, visualization, writing – review & editing

Corresponding author

Ethics declarations

The manuscript follows all the ethical standards, including plagiarism.

Consent to participate

Yes.

Consent for Publication

Yes.

Conflict of Interests

No conflicts of interest.

Additional information

Publisher’s Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Singh, P., Yadav, D.S. Design and Investigation of F-shaped Tunnel FET with Enhanced Analog/RF Parameters. Silicon 14, 6245–6260 (2022). https://doi.org/10.1007/s12633-021-01420-w

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s12633-021-01420-w