Abstract

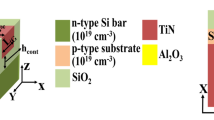

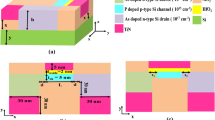

In this work, the junctionless (JL) feature is incorporated in a newly invented device called vertical super-thin body (VSTB) FET and a comparative exploration of DC and analog/RF figures of merit (FoM) is reported for various gate dielectric materials with high-k (Si3N4/HfO2) and low-k (SiO2) in this novel device through a properly calibrated Sentaurus TCAD tool. A significant minimization of short channel effects by Si3N4 and HfO2 is reflected in all the DC FoM. With respect to SiO2, off-state leakage current and on-to-off current ratio improves by five (three) orders of magnitude, whereas on current increases by 4.93 (11.83) μA for HfO2 (Si3N4). Further, using HfO2 (Si3N4) as gate dielectric instead of SiO2, induces a drop of 23.3 (13.91) mV/V in subthreshold swing. The core reason behind such beneficial impact of higher dielectric constant (εr) on DC FoM is explained through off-state energy band diagram and bulk electrostatic potential of the device. Besides, though HfO2/Si3N4 increases gate capacitance (Cgg) and gate-drain capacitance (Cgd), both Cgg/Cgd exhibits extremely low values for all the gate dielectrics. Such an attribute helps in achieving higher unit gain cut-off frequency and gain-bandwidth-product. A higher εr also influences other analog/RF parameters favorably. It is observed that compared to SiO2, HfO2 (Si3N4) enhances peak values of transconductance, intrinsic gain, transconductance frequency product, gain frequency product, and gain transconductance frequency product by 37.74 (13.16) μA, 48.08 (24.91), 0.832 (0.278) THz/V, 1.01 (0.465) THz, 34.3 (22.8) THz/V, respectively. This study is intended to establish a broader understanding about the influence of high-k gate dielectrics on the performance of JL VSTB FET.

Similar content being viewed by others

References

Skotnicki T, Hutchby JA, King T-J, Wong H-SP, Boeuf F (2005) The end of CMOS scaling: toward the introduction of new materials and structural changes to improve MOSFET performance. IEEE Circ Devices Mag 21(1):16–26. https://doi.org/10.1109/MCD.2005.1388765

Balestra F (2014) Silicon-on-insulator devices. Wiley Encyclopedia of Electrical and Electronics Engineering

Jaju V, Dalal V (2004) Silicon-on-insulator technology. EE 530 Advances in MOSFETs, pp. 1–12

Cristoloveanu S (2001) Silicon on insulator technologies and devices: from present to future. Solid State Electron 45(8):1403–1411

Zhang X, Connelly D, Takeuchi H, Hytha M, Mears RJ, Liu TK (2017) Comparison of SOI versus bulk FinFET technologies for 6T-SRAM voltage scaling at the 7−/8-nm node. IEEE Trans Electron Devices 64(1):329–332. https://doi.org/10.1109/TED.2016.2626397

Uchida K, Koga J, Takagi S-I (2003) Experimental study on carrier transport mechanisms in double- and single-gate ultrathin-body MOSFETs - Coulomb scattering, volume inversion, and δTSOI -induced scattering. IEEE International Electron Devices Meeting 2003, Washington, DC, USA, pp. 33.5.1–33.5.4. https://doi.org/10.1109/IEDM.2003.1269402

Omura Y, Konishi H, Yoshimoto K (2008) Impact of fin aspect ratio on short-channel control and drivability of multiple-gate SOI MOSFETs. J Semicond Technol Sci 8(4):302–310

Liu Y, Ishii K, Masahara M, Tsutsumi T, Takashima H, Yamauchi H, Suzuki E (2004) Cross-sectional channel shape dependence of short channel effects in fin-type double-gate metal oxide semiconductor field effect transistors. Jpn J Appl Phys 43(4S):2151

Barman KR, Baishya S (2019) Performance analysis of vertical super-thin body (VSTB) FET and its characteristics in presence of noise. Appl Phys A Mater Sci Process 125(6):401. https://doi.org/10.1007/s00339-019-2682-x

Koldiaev V, Pirogova R (2014) Vertical super-thin body semiconductor on dielectric wall devices and methods of their fabrication. U.S. Patent 8 796 085 B2

Barman KR, Baishya S (2019) An insight to the performance of vertical super-thin body (VSTB) FET in presence of interface traps and corresponding noise and RF characteristics. Appl Phys A Mater Sci Process 125(12):865. https://doi.org/10.1007/s00339-019-3165-9

Barman KR, Baishya S (2019) An architectural parametric analysis for vertical super-thin body (VSTB) MOSFET with double material gate (DMG). TENCON 2019–2019 IEEE region 10 conference (TENCON), Kochi, India, pp. 62–66. https://doi.org/10.1109/TENCON.2019.8929531

Colinge J (2012) “Junctionless transistors”, 2012 IEEE international meeting for future of Electron devices, Kansai, Osaka, pp. 1–2

Colinge JP et al. (2011) "Junctionless transistors: physics and properties" in semiconductor-on-insulator materials for Nanoelectronics applications Berlin Germany: Springer

Colinge JP, Lee CW, Ferain I, Akhavan ND, Yan R, Razavi P, Yu R, Nazarov A, Doria RT (2010) Reduced electric field in junctionless transistors. Appl Phys Lett 96(7):73–510

Kranti A, Lee C-W, Ferain I, Yu R, Akhavan ND, Razavi P, Colinge JP (2010) “Junctionless nanowire transistor (JNT): Properties and design guidelines”. Proc. IEEE 34th ESSDERC pp. 357–360

Lee C et al (2010) High-temperature performance of silicon Junctionless MOSFETs. IEEE Trans Electron Devices 57(3):620–625. https://doi.org/10.1109/TED.2009.2039093

Salmani-Jelodar M, Ilatikhameneh H, Kim S, Ng K, Sarangapani P, Klimeck G (2016) Optimum high-k oxide for the best performance of ultra-scaled double-gate MOSFETs. IEEE Trans Nanotechnol 15(6):904–910. https://doi.org/10.1109/TNANO.2016.2583411

Maity NP, Maity R, Dutta S, Deb S, Sravani KG, Rao KS, Baishya S (2020) Effects of hafnium oxide on surface potential and drain current models for subthreshold Short Channel metal-oxide-semiconductor-field-effect-transistor. Trans Electr Electron Mater 1–9. https://doi.org/10.1007/s42341-020-00181-4

Auth C et al. (2012) “A 22nm high performance and low-power CMOS technology featuring fully-depleted tri-gate transistors, self-aligned contacts and high density MIM capacitors”, 2012 Symposium on VLSI Technology (VLSIT), pp. 131–132, https://doi.org/10.1109/VLSIT.2012.6242496

Mohapatra NR, Desai MP, Narendra SG, Rao VR (2002) The effect of high-K gate dielectrics on deep submicrometer CMOS device and circuit performance. IEEE Trans Electron Devices 49(5):826–831. https://doi.org/10.1109/16.998591

Westlinder J (2004) “Investigation of novel metal gate and high-k dielectric materials for CMOS technologies”. Doctoral Thesis, Uppsala University

Panchanan S, Maity R, Baishya S, Maity NP (2020) “Modeling, simulation and analysis of surface potential and threshold voltage: application to high-K material HfO2 based FinFET”, Silicon, pp. 1–19

Panchanan S, Maity R, Baishya S, Maity NP (2021) A surface potential model for tri-gate metal oxide semiconductor field effect transistor: analysis below 10 nm channel length. Eng Sci Technol Int J 24(4):879–889

Chakraborty H, Maity R, Baishya S, Maity NP (2021) An accurate model for threshold voltage analysis of dual material double gate metal oxide semiconductor field effect transistor. Silicon 13:1851–1861. https://doi.org/10.1007/s12633-020-00553-8

Maity NP, Maity R, Baishya S (2019) An analytical model for the surface potential and threshold voltage of a double gate heterojunction tunnel FinFET. J Comput Electron 18(1):65–75

Sentaurus Device User Guide (2017) Version M-2017.09, Mountain View, CA, USA

Abe Y, Miyata N, Shiraki Y, Yasuda T (2007) Dipole formation at direct-contact HfO 2 /Si interface. Appl Phys Lett 90(17):172906. https://doi.org/10.1063/1.2731514

Baidya A, Baishya S, Lenka TR (2017) Impact of thin high-k dielectrics and gate metals on RF characteristics of 3D double gate junctionless transistor. Mater Sci Semicond Technol 71:413–420

Kawasaki H et al. (2006) Embedded Bulk FinFET SRAM Cell Technology with Planar FET Peripheral Circuit for hp32 nm Node and Beyond. 2006 Symposium on VLSI technology, 2006. Digest of Technical Papers, pp. 70–71. https://doi.org/10.1109/VLSIT.2006.1705221

Eng Y-C et al (2018) Importance of ΔVDIBLSS / (Ion/Ioff) in evaluating the performance of n-channel bulk FinFET devices. IEEE J Electron Devices So 6:207–213. https://doi.org/10.1109/JEDS.2018.2789922

Kilchytska V, Nève A, Vancaillie L, Levacq D, Adriaensen S, van Meer H, De Meyer K, Raynaud C, Dehan M, Raskin J-P, Flandre D (2003) Influence of device engineering on the analog and RF performances of SOI MOSFETs. IEEE Trans Electron Devices 50(3):577–588

Barman KR, Baishya S (2020) “Study of Temperature Effect on Analog/RF and Linearity Performance of Dual Material Gate (DMG) Vertical Super-Thin Body (VSTB) FET”. Silicon. https://doi.org/10.1007/s12633-020-00561-8

Hirpara Y, Saha R (2020) Analysis on DC and RF/analog performance in multifin-FinFET for wide variation in work function of metal gate. Silicon 13:73–77. https://doi.org/10.1007/s12633-020-00408-2

Vijayvargiya V, Vishvakarma SK (2014) Effect of drain doping profile on double-gate tunnel field-effect transistor and its influence on device RF performance. IEEE Trans Nanotechnol 13(5):974–981. https://doi.org/10.1109/TNANO.2014.2336812

Raskin J-P (2006) Tsung Ming Chung, V. Kilchytska, D. Lederer, D. Flandre. Analog/RF performance of multiple gate SOI devices: wideband simulations and characterization. IEEE Trans Electron Devices 53(5):1088–1095. https://doi.org/10.1109/TED.2006.871876

Saha R, Bhowmick B, Baishya S (2018) Temperatute effect on RF/analog and linearity parameters in DMG FinFET. Appl Phys A Mater Sci Process 124:642. https://doi.org/10.1007/s00339-018-2068-5

Saha R, Goswami R, Bhowmick B, Baishya S (2020) Dependence of RF/analog and linearity figure of merits on temperature in ferroelectric FinFET: a simulation study. IEEE Trans Ultrason Ferroelectr Freq Control 67(11):2433–2439. https://doi.org/10.1109/TUFFC.2020.2999518

Sahu PK, Mohapatra SK, Pradhan KP (2014) Impact of downscaling on analog/RF performance of sub-100 nm GS-DG MOSFET. J Microelectron Electron Components Mater 44(2):119–125

Availability of data and materials

(Not applicable)

Author information

Authors and Affiliations

Contributions

All authors contributed to the study, conception, and design.

Corresponding author

Ethics declarations

We comply with the ethical standards of this journal.

Ethics approval and consent to participate

We ensure that all the authors mentioned in the manuscript have agreed for authorship, read and approved the manuscript, and given consent for submission and subsequent publication of the manuscript.

Consent for publication

We give our consent to publish identifiable details to be published in the above Journal and Article.

Conflict of interest/competing interests

We do not have involvement in any organization or entity with any financial interest (such as honoraria; educational grants; participation in speakers’ bureaus; membership, employment, consultancies, stock ownership, or other equity interest; and expert testimony or patent-licensing arrangements), or non-financial interest (such as personal or professional relationships, affiliations, knowledge or beliefs) in the subject matter or materials discussed in this manuscript.

We declare that there is no conflict of interest in this manuscript.

Disclosure of potential conflicts of interest

Not applicable.

Research involving Human Participants and/or Animals

Not applicable.

Consent informed

We declare that this manuscript is original, has not been published before and is not currently being considered for publication elsewhere.

We confirm that the manuscript has been read and approved by all named authors and that there are no other persons who satisfied the criteria for authorship but are not listed. We further confirm that the order of authors listed in the manuscript has been approved by all of us.

We understand that the Corresponding Author is the sole contact for the Editorial process. She is responsible for communicating with the other authors about progress, submissions of revisions and final approval of proofs.

Additional information

Publisher’s Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Barman, K.R., Baishya, S. An Insight into the DC and Analog/RF Response of a Junctionless Vertical Super-Thin Body FET towards High-K Gate Dielectrics. Silicon 14, 6113–6121 (2022). https://doi.org/10.1007/s12633-021-01393-w

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s12633-021-01393-w