Abstract

The presented work investigates about the deformation of semiconductor device induced by electrochemical deposited thick copper films. It enhances thermal and electric performances allowing to use copper interconnections without formations of intermetallic layers at the interfaces with consequent reliability improvement. Nevertheless, the induced deformation strongly affects manufacturability, criticizing the integration between different process steps. Experiment based on phase-shift Moiré principle has been performed to better understand the relation between warpage and temperature. Finite element model has been developed to reproduce the phenomenon in order to address the design and the process integration optimizing workability, electrical performances and reliability.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

Thick copper electrochemical deposition (ECD) represents an attractive technology to manufacture front metallization of power semiconductor device. Compared with the nowadays common material for device front metallization, such as aluminium compounds, copper offers better electrical and thermal conductivity, which permit respectively to reduce device resistance and to improve heat dissipation providing better capabilities against electrical overload such as short-circuit. Copper metallization allows an enhanced compatibility between device fabrication (so called “Front-End” manufacturing) and final package assembly (so called “Back-End” manufacturing), improving the product process integration [2]. In fact, copper front metal enables the wire bonding of copper wire on copper device front metal (Cu–Cu), which is more reliable and more performant than Cu–Al or Au–Al systems allowing welding of homogeneous materials and avoiding intermetallic formation and growth at the interfaces [4]. The main technique to produce thick copper film on silicon substrate is the electrochemical deposition (ECD), which is a highly efficient wet process for depositing a uniform layer of metal (like copper) on wafer surface. Even if its properties make copper very attractive as device front metal, the Cu integration into the wafer manufacturing flow is a technical challenge. Deposited copper produces severe wafer warpage, which negatively affects the yield of all subsequent Front-End and Back-End processes in particular it affects the accuracy and the tolerance chain of all the photolithographic processes. The wafer warpage caused by thick Cu layer is mostly due to plastic deformation during annealing. It has been experimentally observed that warpage has no-linear trend versus temperature and that the residual wafer warpage has been generated during the mandatory annealing process. This process serves to make copper softer and to stabilize its grain size, avoiding in this way electromigration issues which can impact on interconnect reliability [3]. The scope of this work is to characterize the warpage induced by 20 µm thick Cu film on a rectangular wafer slice, according to different annealing profiles. A dedicated interferometric non-contact measurements method has been used for characterize warpage. In order to physically understand the not-linear dependency between temperature and warpage, it has been performed a differential scanning calorimetric (DSC) analysis. A finite element model (FEM) has been developed to predict the geometrically stress-curvature relation, considering material not-linearity. Numerical outcomes have been compared with the results of common analytical equations.

2 Experimental activity

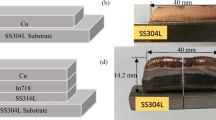

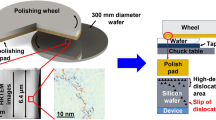

The considered test vehicles were 50 × 10 × 0.75 mm beams, made by silicon substrate 0.73 mm-thick, TiW 0.3 µm, Cu seed 0.2 µm and ECD copper 20 µm-thick. These portions have been sliced from wafer just after copper electro-deposition at room temperature, therefore copper has not been thermally treated before the deformation measurements. The measurements have been performed using an interferometric system, based on “Phase-Shift Moiré” method and described in [1]. Basically, analysed sample is illuminated by a stripped pattern, which is deformed by the sample’s surface structure. The resulting image is captured by a CCD camera, that correlates the out-of-plane deformation with xy coordinates (Fig. 1). The desired temperature profiles have been reproduced during warpage measurement, heating sample by the infrared heater and cooling with compressed air. In order to evaluate the impact of heating/cooling rate and maximum temperature, beams were annealed according to different temperature profiles. Analyses show the maximum temperature is the main factor to determine the permanent warpage, whereas the increasing in warpage, during the heating phase, stops at around 150 °C. DSC highlights an irreversible transformation happened at this temperature, which adds to the copper mechanical softening enhanced by increasing temperature.

3 Numerical approach

A Finite Element Model has been developed to calculate the warpage variation, curvature and mechanical stress due to temperature variation and morphological Copper grain growth. Discretization has been performed considering silicon substrate (thickness 730 µm) and ECD copper layer (thickness 20 µm) as 3D hexaedra elements, while TiW and seed copper films have been added in the model including specific 2D shell elements because they are much thinner than other stacked materials. Due to the symmetry of considered samples, it has been modeled only a quarter (25 × 5 × 0.75 mm instead of 50 × 10 × 0.75 mm). In order to reproduce the experimental observed not-linearity, Cu softening has been modelled. Numerical outcomes have been benchmarked with literature approaches [5] and correlated with experimental results, as shown in Figs. 3 and 4.

Warpage along cutline, shown in Fig. 3, at 150 °C, both for FEM and for experimental results

4 Conclusion

The presented approach has been shown maximum temperature as the main factor to establish residual warpage in semiconductor device with Cu ECD films, highlighting involved not-linearities and calculating warpage with numerical approach. The non-linearity is due to Copper grain growth, highlighted by physical investigation and by thermo-gravimetric (DSC) measurements. Developed methodology is used at design level to minimize warpage variation, by optimizing the ECD copper pattern layout and at process decision making for the selection of the material stack. These factors play a major role to improve the wafer manufacturability and helping the integration among Front-End/Back-End Processes.

References

Calabretta, M., Sitta, A., Oliveri, S.M., Sequenzia, G.: An integrated approach to optimize power device performances by means of stress engineering. In: International Conference on Design, Simulation, Manufacturing: The Innovation Exchange, pp. 481–491. Springer, Cham (2019)

Calabretta, M., Sitta, A., Oliveri, S.M., Sequenzia, G.: Design and process optimization of a sintered joint for power electronics automotive applications. In: International Conference on Design, Simulation, Manufacturing: The Innovation Exchange, pp. 470–480. Springer, Cham (2019)

Du, S., Li, Y.: Effect of annealing on microstructure and mechanical properties of magnetron sputtered Cu thin films. In: Advances in Materials science and Engineering (2015)

Gross, D., Haag, S., Reinold, M., Schneider-Ramelow, M., Lang, K.D.: Correlation between chip metallization properties and the mechanical stability of heavy Cu wire bonds. In: Proceedings of PCIM Europe 2015; International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management, pp. 1–8. VDE (2015)

Stoney, G.G.: The tension of metallic films deposited by electrolysis. Proc. Roy. Soc. Lond. Ser. A Contain. Pap. Math. Phys. Charact. 82(553), 172–175 (1909)

Funding

Open access funding provided by Università degli Studi di Catania within the CRUI-CARE Agreement. This paper belongs to a research path funded by Università degli Studi di Catania (PIA.CE.RI. 2020-2022 Linea 2 – Progetto Interdipartimentale GOSPEL – Codice 61722102132).

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Calabretta, M., Sitta, A., Oliveri, S.M. et al. An experimental-numeric approach to manufacture semiconductor wafer using thick copper front metallization. Int J Interact Des Manuf 15, 117–119 (2021). https://doi.org/10.1007/s12008-020-00736-y

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s12008-020-00736-y