Abstract

This study investigated the gate capacitance and off-state characteristics of 650-V enhancement-mode p-GaN gate AlGaN/GaN high-electron-mobility transistors after various degrees of gate stress bias. A significant change was observed in the on-state capacitance when the gate stress bias was greater than 6 V. The corresponding threshold voltage exhibited a positive shift at low gate stress and a negative shift when the gate stress was greater than 6 V, which agreed with the shift observation from the I–V measurement. Moreover, the off-state leakage current increased significantly after the gate stress exceeded 6 V during the off-state characterization although the devices could be biased up to 1000 V without breakdown. The increase in the off-state leakage current would lead to higher power loss.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

Introduction

AlGaN/GaN high-electron-mobility transistors (HEMTs) have been widely applied in switching power supplies because of their superior GaN-based properties.1,2,3,4,5,6,7,8,9,–10 These excellent properties include high electron mobility, a high breakdown field, and good thermal characteristics. At the interface of the AlGaN and GaN layers, a two-dimensional electron gas (2DEG) with a high concentration of electrons is formed as a device channel because of spontaneous and piezoelectric polarizations to further reduce on-resistance.11,12,13,14,15,16,17,18,–19 An enhancement-mode (E-mode) transistor is preferred in power switching circuits; therefore, AlGaN/GaN HEMTs with a p-GaN or p-AlGaN gate layer for depleting the underneath 2DEG channel are the major technology currently used to achieve E-mode operation.20,21,22,–23 If a p-type ohmic contact metal is used for the gate electrode, the gate will start to turn on at relatively low positive gate voltages and induce a high gate leakage current, thereby limiting the input gate voltage swing in E-mode operation. However, if a Schottky contact metal is used for the gate electrode, the gate leakage current can be reduced at a high positive gate voltage and the input gate voltage swing can be increased. When a positive gate bias is applied, diode D1 (formed by Schottky gate metal/p-GaN) is reverse-biased and D2 (formed by p-GaN/AlGaN/GaN) is forward-biased. At a high positive gate bias, the D1 formed at the gate metal and p-GaN dominate the gate leakage current because of the drop in reverse voltage on the Schottky diode. Several published studies have investigated the device characteristics of p-GaN gate AlGaN/GaN HEMTs, including their threshold voltage shift, leakage current, and degradation mechanisms.21,24,25,26,27,28,29,30,31,32,–33 However, prior research focused on the device I–V characteristics. The present study investigated the gate capacitance and device off-state characteristics of E-mode p-GaN gate HEMTs with Schottky gate metallization after gate stress for the first time. To use C–V measurement to investigate the p-GaN gate characteristics can further understand the Schottky gate diode and p-GaN/AlGaN/GaN diode after various gate bias stress. The off-state current measurement right after the gate bias stress is to reproduce the real on–off operation during the high-frequency switching. To understand the effect after positive gate bias if any effect on the off-state current and breakdown voltage.

Experimental Results and Discussion

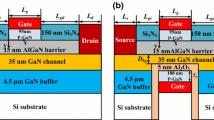

Commercially packaged 650-V-rated devices with a gate width of 118 mm were studied. E-mode p-GaN/AlGaN/GaN HEMTs were grown on 6-in. Si substrate and fabricated by Taiwan Semiconductor Manufacturing Company. The gate length and the gate-to-drain distance are 1.4 μm and 18 μm, respectively. To investigate the p-GaN gate stability, various gate positive biases were applied for 10 s before C–V and the off-state measurements.

The gate positive biases (VGS,stress) were 1, 2, 3, 4, 5, 6, 7, 8, V with VDS = 0 V. After each VGS,stress, the gate C–V (VDS = 0 V) and off-state characteristics (VGS = 0 V) were measured and compared with the without-stress measurements. After the measurement, all voltage biases were removed for 30 min before the next stress measurement to confirm if the device could be fully recovered. Figure 1 plots the measured C–V characteristics after different gate stress voltages under frequencies of 1 kHz, 10 kHz, 100 kHz, and 1 MHz.

The measured gate C–V characteristics revealed a typical off-to-on transient as the gate voltage increasing from 1 V to 3 V, indicating the threshold voltage (VTH) was approximately 2 V. Once the device was turned on, the measured capacitance remained constant. The measured capacitances in the off-state did not exhibit distinct differences; however, the capacitances measured in on-state bias conditions (for example VGS = 5 V) exhibited significant differences in the values under different gate stresses. Figure 2 shows the normalized capacitance measured at VGS = 1 V and 5 V versus various gate stresses (VG,stress) under different measurement frequencies. The normalized capacitance is the measured capacitance of each gate-stress divided by the capacitance without gate-stress. The change in the measured capacitance at VGS = 1 V was small but still demonstrated an effect from gate stress. However, a significant change was observed when the gate stress was greater than 6 V, as shown in Fig. 2b. The increase in the measured capacitance was more than 20% at low frequencies. When the device is turned on, the gate structure from the gate electrode to the 2DEG channel consists of a Schottky diode (D1) formed of gate-metal/p-GaN and a p-GaN/AlGaN/GaN diode (D2) in series, as shown in Fig. 3. As described in Ref. 23, when the VG is higher than 1.5 V, the voltage drop across D2 is almost saturated (due to the forward bias at D2) and the applied VGS is mostly across D1. Therefore, at a high positive VGS bias, the Schottky diode (D1) limits the leakage current because of reverse bias. Because the capacitance value of D1 from the depletion region is smaller than that from the forward-biased D2, the measured capacitance is the result of D1 in series with D2. Therefore, the change (increase) in Fig. 2b was attributed to the change inside D1, which was mostly in the depletion region of D1, as shown in Fig. 3c.34 Based on the two-junction model described in Ref. 34, a junction capacitor (CD1) due to the Schottky metal/p-GaN junction was added in series with the AlGaN barrier capacitor (CD2). The total capacitance value (Ctotal) is given by:

Normalized capacitance versus gate stress voltage (VGS,stress) obtained at (a) VGS = 1 V and (b) VGS = 5 V in Fig. 1 (VDS = 0 V).

The CD2 is simply calculated by using the ideal dielectric constant of the AlGaN and assumed to be constant. At VGS = 5 V and VDS = 0 V, most of the applied gate voltage drops across the depletion region in the diode D1 once the 2DEG has been formed. The small-signal capacitance CD1 is given by:

Therefore, an increase of the measured capacitance is mostly due to the change in the charge density (Qg-pGaN) within the p-GaN layer. This was mainly because of hole/electron injection into the p-GaN region after high positive gate stress and the carriers being trapped in the p-GaN region.25 The trapped carriers resulted in a change in the measured capacitance, especially in the low-frequency measurement where the trapping/detrapping time constant was long. At measurement frequencies less than 10 kHz, the effect from high positive gate stress was significant and exhibited an increase of more than 20%. Using this characterization measurement, the quality of p-GaN can be revealed when the gate is under high positive bias.

As described previously, the measured gate C–V characteristics in Fig. 1 exhibit the typical off-to-on transient as the gate voltage increased from 1 V to 3 V. To study the shift in threshold voltage (VTH) after gate stress, the peak values of ΔC versus VGS from the C–V curves in Fig. 1 were studied, and the corresponding VGS (defined as VG,peak and VTH) in the peak values of ΔC versus various gate stress voltages (VGS,stress) was derived and plotted in Fig. 4. In this figure, the VG,peak (VTH) shift is referred to as the value change of VG,peak compared with that without gate stress (VGS,stress = 0 V). The obvious trend in Fig. 4 is a negative shift at VGS,stress of 1 V, and then a positive shift before VGS,stress increases to 6 V. Once VGS,stress is greater than 6 V, a significant negative shift is observed. A higher value of − 0.23 V was obtained after positive 8-V gate stress was applied for 10 s. This observation is similar to the results in29 for a Schottky p-GaN HEMT from a typical ID–VGS characteristic. The first positive shift was related to the electron injection, which accumulated or was trapped in the p-GaN layer. The negative shift at high gate stress bias was caused by the additional hole injection, which resulted in the negative shift observed in Fig. 4.

The off-state characteristics were measured immediately after various gate stress voltages were applied. For example, the off-state leakage current ID was measured up to VDS of 1000 V at VGS = 0 V right after VGS,stress of 1 V for 10 s. After the off-state measurement, all voltage biases were removed for 30 min before the next stress measurement to confirm whether the device could be fully recovered. Figure 5 illustrates the measured off-state current versus the drain bias after various gate stress voltages. The packaged devices could be biased up to 1000 V without breakdown. The off-state current was as low as 10−8 mA/mm before 200 V, and then increased to 10−4 mA/mm at 1000 V. However, the off-state current increased significantly after the gate stress exceeded 6 V during the off-state characterization when the VDS was within 300 V. Figure 6 shows a plot of the off-state current versus various gate stress voltages (VGS,stress) at different VDS values. Clearly observed is the off-state current increasing significantly at VDS of 100 and 200 V after the VGS,stress exceeds 6 V. The increase is approximately three orders of magnitude. A possible reason is the negative shift of the threshold voltage while VGS,stress is larger than 6 V as shown in Fig. 4 because the off-state current was measured at VGS = 0 V. The voltage difference between the gate bias (0 V) and the VTH is reduced, thus the leakage current is possibly increased. Because of the negative shift in VTH at high gate stress bias was caused by the additional hole injection. The accumulated holes in the p-GaN slightly induce the electrons in the channel and cause the leakage current.

However, the impact of the gate stress bias was limited and the increase in the off-state current was small when the VDS was greater than 700 V.

Conclusions

This study investigated the gate capacitance and off-state current of 650-V E-mode p-GaN gate AlGaN/GaN HEMTs after various gate stress voltages. The changes in the measured capacitance in the off- and on-states demonstrated the different effects of gate stress bias. The measured off-state gate capacitance did not significantly change because no 2DEG was in the channel under the gate, and thus, the capacitance was small and changed little. However, the measured on-state capacitance significantly increased when the gate stress bias was greater than 6 V, especially at low measurement frequencies. Moreover, the on–off transient voltage shifted because of the gate stress bias. A negative shift was observed when the gate stress bias was greater than 6 V. Finally, the off-state current was measured after various levels of gate stress bias; the off-state current exhibited a significant increase after larger gate stress biases when the drain bias was low, which is related to the threshold voltage shift. In conclusion, the threshold voltage, gate capacitance, and off-state current changed significantly after gate stresses greater than 6 V for the studied p-GaN gate AlGaN/GaN HEMTs. This is why most commercial p-GaN gate HEMTs are unsuitable for biases greater than 6 V.

References

M. Asif Khan, A. Bhattarai, J.N. Kuznia, and D.T. Olson, Appl. Phys. Lett. 63, 1214 (1993).

U.K. Mishira, P. Parikh, and Y.-F. Wu, Proc. IEEE 90, 1022 (2002).

T. Kikkawa, Jpn. J. Appl. Phys. 44, 4896 (2005).

U.K. Mishra, L. Shen, T.E. Kazior, and Y.-F. Wu, Proc. IEEE 96, 287 (2008).

S. Maroldt, R. Quay, P. Dennler, D. Schwantuschke, M. Musser, M. Dammann, R. Aidam, P. Waltereit, A. Tessmann, and O. Ambacher, Jpn. J. Appl. Phys. 52, 08JN13 (2013).

S. Karmalkar and U.K. Mishra, IEEE Trans. Electron Devices 48, 1515 (2001).

W. Saito, Y. Takada, M. Kuraguchi, K. Tsuda, I. Omura, T. Ogura, and H. Ohashi, IEEE Trans. Electron Devices 50, 2528 (2003).

Y. Uemoto, M. Hikita, H. Ueno, H. Matsuo, H. Ishida, M. Yanagihara, T. Ueda, T. Tanaka, and D. Ueda, IEEE Trans. Electron Devices 54, 3393 (2007).

P. Godignon, X. Perpiñà, A. Pérez-Tomás, and J. Rebollo, IEEE Trans. Power Electron. 29, 2155 (2014).

T. Kachi, Jpn. J. Appl. Phys. 53, 100210 (2014).

J. Derluyna, S. Boeykens, K. Cheng, R. Vandersmissen, J. Das, W. Ruythooren, S. Degroote, M.R. Leys, M. Germain, and G. Borghs, J. Appl. Phys. 98, 054501 (2005).

N. Ikeda, Y. Niiyama, H. Kambayashi, Y. Sato, T. Nomura, S. Kato, and S. Yoshida, Proc. IEEE 98, 1151 (2010).

R. Chu, A. Corrion, M. Chen, R. Li, D. Wong, D. Zehnder, B. Hughes, and K. Boutros, IEEE Electron. Device Lett. 32, 632 (2011).

M. Ishida, T. Ueda, T. Tanaka, and D. Ueda, IEEE Trans. Electron Devices 60, 3053 (2013).

T. Ueda, M. Ishida, T. Tanaka, and D. Ueda, Jpn. J. Appl. Phys. 53, 100214 (2014).

X. Yu, J. Ni, Z. Li, J. Zhou, and C. Kong, Jpn. J. Appl. Phys. 53, 051001 (2014).

M. Agrawal, K. Radhakrishnan, N. Dharmarasu, and S.S. Pramana, Jpn. J. Appl. Phys. 54, 065701 (2015).

C.-T. Yeh, W.-K. Wang, Y.-S. Shen, and R.-H. Horng, J. Appl. Phys. 55, 05FK06 (2016).

M. Cui, Q. Bu, Y. Cai, R. Sun, W. Liu, H. Wen, S. Lam, Y.C. Liang, I.Z. Mitrovic, S. Taylor, P.R. Chalker, and C. Zhao, Jpn. J. Appl. Phys. 58, 056505 (2019).

G. Grecoa, F. Iucolanob, and F. Roccafortea, Mater. Sci. Semicond. Process. 78, 96 (2018).

M. Meneghini, O. Hilt, J. Wuerfl, and G. Meneghesso, Energies 10, 153 (2017).

D. Marcona, M. Van Hovea, B. De Jaegera, N. Posthumaa, D. Wellekensa, S. Youa, X. Kanga, T.-L. Wua, M. Willemsa, S. Stoffelsa, and S. Decouterea, Proc. SPIE 9363, 936311 (2015).

A.N. Tallarico, S. Stoffels, P. Magnone, N. Posthuma, E. Sangiorgi, S. Decoutere, and C. Fiegna, IEEE Electron. Device Lett. 38, 99 (2017).

I. Rossetto, M. Meneghini, O. Hilt, E. Bahat-Treidel, C.D. Santi, S. Dalcanale, J. Wuerfl, E. Zanoni, and G. Meneghesso, IEEE Trans. Electron Devices 63, 2334 (2016).

X. Tang, B. Li, H.A. Moghadam, P. Tanner, J. Han, and S. Dimitrijev, IEEE Electron. Device Lett. 39, 1145 (2018).

A. Stockman, F. Masin, M. Meneghini, E. Zanoni, G. Meneghes, B. Bakeroot, and P. Moens, IEEE Trans. Electron Devices 65, 5365 (2018).

L. Savadi, G. Iannaccone, S. Sicre, S. Lavanza, G. Fiori, O. Haberlen, and G. Curatola, in 48th European Solid-State Device Research Conference (ESSDERC), p. 18 (2018).

Y. Shi, Q. Zhou, Q. Cheng, P. Wei, L. Zhu, D. Wei, A. Zhang, W. Chen, and B. Zhang, in IEEE 30th International Symposium on Power Semiconductor Devices and ICs (ISPSD), p. 96 (2018).

A. Barbato, V. Padovan, O. Haeberlen, M. Silvestri, T. Detzel, G. Meneghesso, and E. Zanoni, IEEE Trans. Electron Devices 65, 2778 (2018).

A. Stockman, E. Canato, A. Tajalli, M. Meneghini, G. Meneghesso, E. Zanoni, P. Moens, and B. Bakeroot, in IEEE International Reliability Physics Symposium (IRPS), 4B.5-1 (2018).

S. Stoffels, B. Bakeroot, T.L. Wu, D. Marcon, N.E. Posthuma, S. Decoutere, A.N. Tallarico, and C. Fiegna, in 2017 IEEE International Reliability Physics Symposium (IRPS), 4B-4.1 (2017).

J. He, G. Tang, and K.J. Chen, IEEE Electron. Device Lett. 39, 1576 (2018).

Y. Shi, Q. Zhou, Q. Cheng, P. Wei, L. Zhu, D. Wei, A. Zhang, W. Chen, and B. Zhang, IEEE Trans. Electron Devices 66, 876 (2019).

T.-L. Wu, B. Bakeroot, H. Liang, N. Posthuma, S. You, N. Ronchi, and S. Stof, IEEE Electron. Device Lett. 38, 1696 (2017).

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

Conflict of interest

All authors declare that they have no conflict of interest.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Lai, YC., Zhong, YN., Tsai, MY. et al. Gate Capacitance and Off-State Characteristics of E-Mode p-GaN Gate AlGaN/GaN High-Electron-Mobility Transistors After Gate Stress Bias. J. Electron. Mater. 50, 1162–1166 (2021). https://doi.org/10.1007/s11664-020-08691-w

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11664-020-08691-w