Abstract

An improved Gilbert mixer with the current reuse and source degeneration techniques is investigated. This design and simulation carried out by considering UMC 180 nm CMOS process in the Cadence Tool 6.1.6 with 2.4 GHz. The investigation is presented with the current reuse topology by stacking both pMOS and nMOS transistors. The reduction of the power consumption is obtained due to the self-biasing of the shunt feedback resistor. An improvement in the conversion gain and linearity is shown through the source degeneration in this mixer design. The proposed design achieves the maximum conversion gain (CG) of 13.2 dB with the noise figure (NF) of 8.6 dB. The design circuit consumes 0.7 mW power from 1.2 V with the 1 dB compression point of −2.63 dBm and third-order input intercept point (IIP3) of 8.2 dBm. The chip area occupied is 0.128 × 0.180 mm2 shown in the layout design. This compact layout of the mixer helps to create an opportunity as a suitable building block for RF integrated circuit (RFIC) applications with moderately high performance in the receiver front end.

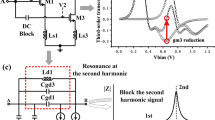

Graphic Abstract

Source degeneration resistor circuit [13]

Similar content being viewed by others

References

Leung, B. (2004). VLSI for Wireless Communication. Singapur, Malaysia: Pearson Education.

Tamilarasi, D., Ramesh, P., Krishnamoorthy, R., Bharatiraja, C., & Jayasankar, T. (2021). Design of radio frequency integrated circuit for RF to DC power converter for bio-medical application. Materials Today: Proceedings, 45, 2139–2144.

Lee, T. H. (2004). The Design of CMOS Radio Frequency Integrated Circuits. Cambridge University Press.

Rout, S.S., & Sethi, K. (2016). Design of high gain and low noise CMOS Gilbert cell mixer for receiver front end design. In: Proceedings of the 2016 International Conference on Information Technology (ICIT), PP. 1–5.

Vidojkovic, V., Tang, J. V. D., Leeuwenburgh, A., & Roermund, A. H. M. V. (2005). A low-voltage folded-switching mixer in 0.18-μm CMOS. IEEE Journal of Solid-State Circuits, 40(6), 1259–1264.

Liang, K. H., Chang, H. Y., & Chan, Y. J. (2007). A 0.5–7.5 GHz ultra low-voltage low-power mixer using bulk-injection method by 0.18-μm CMOS technology. IEEE Microwave and Wireless Components Letters, 17(7), 531–533.

Kim, M. G., An, H. W., Kang, Y. M., Lee, J. Y., & Yun, T. Y. (2012). A low-voltage, low-power, and low-noise UWB mixer using bulk-injection and switched biasing techniques. IEEE Transactions on Microwave Theory and Techniques, 60(8), 2486–2493.

Kim, J. H., An, H. W., & Yun, T. Y. (2009). A low-noise WLAN mixer using switched biasing technique. IEEE Microwave and Wireless Component Letters, 19(10), 650–652.

Rout, S.S., & Sethi, K. (2017). A high conversion gain and low flicker noise gilbert mixer design in 180 nm CMOS process. In: Proceedings of the 2017 14th IEEE India Council International Conference (INDICON), pp. 1–5.

Myoung, N. G., Choi, B. G., Park. S. S., & Park, C. S. (2005). A novel CMOS down-conversion mixer with current reuse technique. In: IEEE Microwave Conference Proceedings, APMC, China, pp. 1–4.

Chen, S., Jin, J., & Zhang, W. (2013). Low-voltage low-power folded mixer using current-reuse technical for IEEE 802.11b wireless application. IETE Journal of Research, 59(4), 415–419.

Jin, J., Wang, C., Sun, J., & Du, S. (2015). Design and simulation of novel amplifier-based mixer for ISM band wireless applications. International Journal of Circuit Theory and Applications, 43(11), 1794–1800.

Mahmou, R., & Faitah, K. (2014). High linearity, low power RF mixer design in 65nm CMOS technology. AEU-International Journal of Electronics and Communications, 68(9), 883–888.

Kalra, D., & Chaturvedi, A. (2014). A 3.1–10.6 GHz CMOS down-conversion mixer for UWB system. In: IEEE International Conference on Signal Processing and Integrated Networks (SPIN), India, pp. 561–564.

Sullivan, P. J., Xavier, B. A., & Ku, W. H. (1997). Low voltage performance of a microwave CMOS Gilbert cell mixer. IEEE Journal of Solid-State Circuits, 32(7), 1151–1155.

Gilbert, G. (1997). The MICROMIXER: A highly linear variant of the Gilbert mixer using a bisymmetric class-AB input stage. IEEE Journal of Solid-State Circuits, 32(9), 1412–1423.

Tan, G. H., Roslina, M. S., Ramiah, H., & Chong, W. K. (2013). A high-conversion gain, low-power mixer adapting current reuse technique for ZigBee application. IETE Journal of Research, 59(2), 128–131.

Lee, J. H., & Lin, Y. S. (2013). A 60-GHz CMOS down-conversion mixer with current-reused RF single-to-differential converter and integrated marchand balun. Microwave and Optical Technology Letters, 55(8), 1937–1947.

Kraimia, H., Taris, T., Begueret, J. B., & Deval, Y. (2011). A 2.4 GHz ultra-low power current-reuse bleeding mixer with resistive feedback. In: IEEE 18th International Conference on Electronics, Circuits and Systems, Lebanon, pp. 488–491.

Lee, S. G., & Choi, J. K. (2000). Current-reuse bleeding mixer. Electronics Letters, 36(8), 696–697.

Aydin, O., Yildiz, H. A., Ozoguz, S., & Toker, A. (2017). MOS-only complex filter design for dual-band GNSS receivers. AEU-International Journal of Electronics and Communications, 82, 83–92. https://doi.org/10.1016/j.aeue.2017.07.035

Rout, S. S., & Sethi, K. (2020). DTMOS based Gilbert mixer design for MICS receiver using current source helpers and switched biasing technique. Sadhana, 45(1), 1–7.

Sedighi, S., Hashemipour, O., & Dousti, M. (2016). A 2.4-GHz highly linear derivative superposition Gilbert cell mixer. Turkish Journal of Electrical Engineering and Computer Sciences, 24(2), 571–579.

Kim, M. G., & Yun, T. Y. (2014). Analysis and design of feedforward linearity-improved mixer using inductive source degeneration. IEEE Transactions on Microwave Theory and Techniques, 62(2), 323–331.

Li, Q., & Yuan, J. S. (2002). Linearity analysis and design optimisation for 0.18 μm CMOS RF mixer. IEE Proceedings-Circuits, Devices and Systems, 149(2), 112–118.

Rout, S. S., Mohapatra, S. K., & Sethi, K. (2018). Design of cascode mixer based on bulk injection and switched biasing techniques in 180 nm CMOS process for a high performance receiver front end. Journal of Low Power Electronics, 14(1), 49–56.

Acknowledgements

All simulations and implementations take place in the laboratories of Veer Surendra Sai University of Technology's Department of ETC, GIET University's Department of ECE, and KIIT University's School of Electronics Engineering. There was no support for this study from any government agency.

Funding

The authors of the work did not obtain any kind of money, grants, or in-kind assistance.

Author information

Authors and Affiliations

Contributions

Author 1 (Shasanka Sekhar Rout): Conceived and implemented the circuit employing simulation, evaluated the correctness of the findings, and produced the paper. Author 2 (S. K. Mohapatra): Conceived and carried out the analysis, calibrated the results, and oversaw the project's review, editing, and supervision. Author 3 (Kabiraj Sethi): Developed the proposed concept, verified the analytical procedures, and monitored the work's findings.

Corresponding author

Ethics declarations

Conflict of interest

The authors of this manuscript certify that they have no financial or non-financial interests (such as honoraria, educational grants, participation in speakers bureaus; membership, employment, consultancies, stock ownership, or other equity interest; and expert testimony or patent licensing arrangements), or no affiliations with or involvement in any organization or entity with any financial or non-financial interest. The authors state that the publishing of this work does not include any conflicts of interest.

Availability of Data and Material

For this research work no supplementary data and material are required.

Ethical Approval

All procedures performed in studies involving human participants were in accordance with the ethical standards of the institutional and/or national research committee and with the 1964 Helsinki declaration and its later amendments or comparable ethical standards.

Informed Consent

Informed consent was obtained from all individual participants included in the study.

Consent to Participate

The authors give full consent to participate in this research work.

Consent for Publication

The authors give full consent for publication of this research work.

Code Availability

All simulations and implementations of the design were performed using the Cadence tool in ETC Department at VSSUT, ECE Department at GIET University and the School of Electronics Engineering at KIIT University. It involves activities for schematic design, layout, verification, and simulation.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Rout, S.S., Mohapatra, S.K. & Sethi, K. Design of 2.4 GHz Improved Current Reuse Gilbert Mixer with Source Degeneration Technique. Wireless Pers Commun 122, 3875–3887 (2022). https://doi.org/10.1007/s11277-021-09115-6

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11277-021-09115-6