Abstract

Fabrication of reproducible superconducting YBa2Cu3O7−x (YBCO) thin films with T c values above 85 K on Si wafers has been realized by optimizing the thin film deposition process. Prior to the deposition of YBCO thin film on (100) p-type Si wafer, YSZ and CeO2 thin films were deposited as buffer layers by RF magnetron sputtering, and subsequently, YBCO thin film was deposited by dc magnetron sputtering. The deposition parameters such as substrate temperature, process gas pressure, Ar/O2 ratio, and power density were optimized for all layers in order to enhance the whole structure to prevent microcrack formation caused by misfits in crystal lattice parameters and thermal expansion coefficients between Si/YSZ/CeO2 and YBCO. Structural analyses were performed on YSZ and CeO2 layers, and electrical and magnetic measurements were carried out on a YBCO layer by employing XRD, SEM, resistance vs. temperature, and AC magnetic susceptibility vs. temperature measurements, respectively. The YBCO layer was also patterned as microbridges in order to test the durability of the whole Si/YSZ/CeO2/YBCO structure during the standard photolithography and wet etching process commonly used in device applications.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

In microelectronic technologies, Si wafers have been intensively used as standard substrate materials for microfabrication of semiconductor devices for decades because of their several important advantages such as low cost, chemical resistance, and good crystalline structure besides their controllable electronic properties such as intentionally doping as p- or n-type [1]. Moreover, microfabrication technology and processing steps have been developed on the silicon-based devices in semiconductor technology. Because the similar device processing steps such as photolithography and selective etching of the layers can be used for Nb-based superconducting devices, Si wafers became the standard substrate materials in conventional low- T c (critical temperature) superconducting devices [2]. However, the case is not that straightforward for the fabrication of high- T c superconducting devices on Si because of many challenges caused by the properties of high- T c materials [14–19]. Since the high-temperature superconductor (HTS) materials become superconductor above the liquid nitrogen temperature, which is quite cheap and easy to handle, it would be very useful to fabricate HTS devices on Si by bringing the main advantages of the HTS materials and Si substrates together [3]. Therefore, this became an attractive research field for many research groups.

Among the various high- T c superconductors, YBa2Cu3O7−x (YBCO) is the most extensively used material for superconducting electronic devices such as Josephson junctions, quantum interference devices, single flux quantum circuits, THz detectors, and bolometers [4–8]. These YBCO-based devices have been fabricated on either single- or bi-crystal SrTiO3 (STO), LaAlO3 (LAO), and MgO substrates with excellent superconducting properties. These substrates are very compatible with YBCO thin film in terms of their lattice constants and thermal expansion coefficients [9]. However, as it was previously mentioned, it is quite attractive to fabricate the same devices on Si substrate because it can provide a much larger area compared to STO, LAO, and MgO substrates. Additionally, STO, LAO, and MgO substrates are commonly available in 1 cm 2 sizes and become very expensive above it. Other important points of using Si wafer are the possibility of superconductor-semiconductor hybrid device application on a single chip and high- T c superconducting integrated circuit fabrication [10, 11]. Also, the Si wafers offer possibility for ultra-high frequency (THz) detectors and RF electronic applications [12, 13]. However, the deposition of superconducting YBCO thin film directly on Si wafer is not possible because of mismatch in the lattice constants and thermal expansion coefficients between YBCO and Si [14]. Another problem is the diffusion of Ba atoms into Si during the high-temperature deposition which is necessary for the YBCO crystal formation [14, 15]. In order to overcome this problem, a chemically stable buffer layer with proper crystalline structure has to be used on Si. This layer is commonly made by a Y2O3+ ZrO2 (YSZ) material which has proper crystal lattice parameters and thermal expansion coefficients with Si (Table 1) [16]. However, this single buffer layer approach does not satisfy the requirements because of yielding very low device performances. Ba atoms in YBCO react with Zr atoms in YSZ thin film by creating unwanted formation at the interface [15]. Therefore, it is predicted that depositing a very thin layer of CeO2 is also required to avoid Ba diffusion into YSZ and enhance the crystal quality of Si/YSZ/CeO2 stack, thus allowing the growth of YBCO thin films with good superconducting properties [17–19].

Although the crystalline formation required for the good quality YBCO thin films on such buffer layers has been determined, reproducible YBCO thin films with T c values above 85 K still become a challenge [17, 21, 22] by considering the process parameters. It has been recognized that, despite the standard fabrication process yet to be developed for particular process, a significant reduction has been observed in the number of publications in the recent years. Additionally, it was understood from the many research articles that there is a considerable need for superconducting YBCO devices fabricated on Si. Therefore, in order to obtain a standard fabrication process, further development is still required and has to be done. The surface properties of Si (such as amorphous native oxide formation), growth temperature, thermal properties of the layers, and finally, the structure of YBCO thin film still need to be studied in order to provide more data for the optimization of the process. By considering these, a systematic study was organized in order to fabricate superconducting YBCO thin films on (100) p-type silicon substrates. YSZ/CeO2 bilayer buffers were deposited onto Si wafer, and the superconducting properties of YBCO thin film were tested depending on the process parameters mentioned above. With our optimized process parameters, reproducible YBCO thin films were achieved with T c values above 85 K. Additionally, the stability of YBCO thin films during the patterning process was tested in order to prove device application capacity of YBCO thin film deposited on silicon wafer.

2 Experiments

Initially, YSZ, CeO2, and YBCO targets and ion gun were mounted into a multiport sputtering chamber in order to perform in situ deposition of multilayer YSZ/CeO2/YBCO trilayer on silicon wafer. Two-inch targets were purchased from the same manufacturer with 99.99 % purity. Kaufman and Robinson ion-beam etching unit was set up in order to etch native oxide layer from Si surface in vacuum before the initial layer deposited. Prior the thin film deposition process, substrates were cleaned in acetone and isopropanol baths ultrasonically for 10 min at 50 ∘C, respectively, and then rinsed in deionized (DI) water and blown out with dry N2 gas. After that, hydrogen fluoride (HF) solution was prepared with a 5:1 (DI water/HF) ratio and the wafer was dipped in for 10 min in order to remove native oxide layer and obtain bare Si wafer surface. Then, the piranha solution with a 3:1 (H3 PO 4/H2O2) ratio was prepared to get rid of chemical and metallic residuals from the Si wafer surface within 20-min chemical reactions. Subsequent dipping into HF solution was also done for 3 min until the wafer surface get dewet which confirms that there is no any oxygen atoms on the Si wafer surface; thus, oxygen molecules cannot bind themselves to Si atoms. Then, the substrates were mounted onto a heater by using silver paste in order to increase the conductivity between heater and substrates, so that it was sure the sample was reached to the desired deposition temperature. The chamber was vacuumed down to 1 × 10 −6 mbar, and the sample stage was tilted to the opposite side of the ion gun through the 360∘ tiltable sample stage at room temperature for etching the wafer surface under a 600-V beam voltage for 2 min at 4 sccm gas flow and 0.35 mTorr argon pressure. Then, the sample was heated up to 800 ∘C at 30 min. During the heating process, the vacuum level is very important. Since the Si has high affinity to oxygen atoms, higher temperatures increase the affinity which causes easy binding of oxygen atoms with Si, and therefore, an undesired SiO x layer grows on the Si wafer surface which breaks the crystal alignment for our structure. At 800 ∘C, the sample stage was tilted in front of the YSZ target and 20 mTorr Ar and 22 mTorr Ar + O2 gas pressures were introduced into the chamber by using a mass flow controller and 15-min deposition was done by applying a 40 W RF power. In the end of the deposition, temperature and pressures were kept constant, the stage was tilted in front of the CeO2 target, and 10-min deposition was carried out by applying the same parameters. After that, the temperature was decreased to 725 ∘C for YBCO deposition under 10 mbar O2 flow in 10 min and the stage was tilted once again until its surface aligned opposite to the YBCO target. The deposition was carried out under 200 mTorr Ar and 250 mTorr Ar + O2 gas pressures at a 70 W DC power for 1 h. In the end of the deposition, the system was cooled down to room temperature at 700 mbar O2 atmosphere with 5 ∘C/min cooling rate. Optimized thin film deposition parameters are given in Table 2.

AC magnetic susceptibility vs. temperature characteristics of the samples were carried out priorly because of its non-destructive/contactless and entire sample characterization property. The measurements were done according to a mutual induction method by using two identical coil systems. The primer coil was driven with a 1 V amplitude AC signal at 1 kHz constant frequency by using a lock-in amplifier, and the diamagnetic response of the sample was analysed according to the induction of AC magnetic field by a seconder coil. The measurement was carried out by fully homemade LN2 cryostat between room temperature and 77 K. Subsequent DC resistance–temperature measurement was carried out by a four-point probe technique for both thin films and microbridges. Meander-type microbridge patterns were fabricated for three samples with 4 μ m linewidth by applying UV-photolithography and wet chemical etching processes. For electrical contacts, Au wires were bonded onto YBCO contact pads directly by using a direct wire bonding technique which were developed by our research group with a wedge-wire bonder [20]. Measurements were done from room temperature to 77 K by applying 100 μ A constant DC bias current.

YSZ and CeO2 thin films were characterized in terms of structural and morphological analysis. XRD and SEM analysis were done for YSZ thin film and YSZ/CeO2 bilayer. A PANalytical-Empyrean model high-temperature XRD system was used, and the samples were scanned between 10∘ and 90∘ (2 𝜃) with a 0.02∘ step angle. SEM analysis was done by a FEI Quanta 450 field emission gun system.

3 Results and Discussion

Thin films were optimized for each layer independently in terms of substrate temperature, sputtering power, gas flow ratio, and film thicknesses. Especially, substrate temperatures and film thicknesses had to be optimized precisely in order to minimize effects of large differences on thermal expansion coefficients and crystal lattice parameters between the YBCO and CeO2/YSZ/Si multilayer structures (see Table 1) and increase the crystallinity. In some cases, the deposited YBCO thin films on CeO2/YSZ/Si could have two in-plane orientations [16]. However, at the specific temperature, epitaxial growth of YBCO thin film with single-crystal alignment is possible with 45∘ rotations of the crystal structure [15, 16, 19]. In order to find optimum values for this formation, we increased deposition temperatures for YSZ and CeO2 to 800 ∘C at which these materials gain single crystallinity and varied YBCO thin film deposition temperatures from 800 to 700 ∘C in order to obtain crackles YBCO thin film formation with the highest superconducting transition temperature. Five different deposition temperatures were used for YBCO thin films: 800, 775, 750, 725, and 700 ∘C, respectively. At 800 ∘C, almost entire of YBCO thin film was cracked and peeled off with the lower layers. As long as the deposition temperature decreased, microcracks disappeared on the thin film surface. At 725 ∘C, YBCO thin film was grown epitaxially onto CeO2/YSZ/Si structure without any surface degradation. At 700 ∘C, film surface and growth properties were also satisfactory; however, superconducting transition temperature was below 80 K which is very low and undesired. Coating different crystal structures or growth directions onto top of each other can be shown as one of the main reasons for the creation of the thin film cracks and peeling off phenomenon. In order to control these properties, deposition temperature should be optimized precisely and crystal formations of each layer should be matched. For that reason, in our experiments, different deposition temperatures were used and different crystal formations were achieved. Among which, the most suitable YBCO thin film crystal formation was obtained at 725 ∘C in order to grow on CeO2/YSZ/Si multilayer structure. As given in Table 2, three samples were prepared by applying the optimized process and the magnetic and electrical characterizations were carried out in order to confirm our optimization by means of AC magnetic susceptibility and DC resistance–temperature measurements (Figs. 1 and 2).

In Fig. 1, metallic behaviour of three YBCO thin film samples in the normal state and very sharp phase transition at T c onset at ∼91 K and zero resistance at T c offset at 85 K were obtained. Diamagnetic properties of the samples were also characterized, and as given in Fig. 2, each YBCO thin film showed very good diamagnetic transition which started at 86 K and fully magnetic field cancellation was observed at 84 K. As shown in Figs. 1 and 2, critical temperatures for three samples from two different measurements are ∼85 K. This is an important finding of our optimization process.

In order to test the durability of whole Si/YSZ/CeO2/YBCO structure and analyse the effects of photolithography and wet etching processes onto superconducting transition temperature of YBCO thin films, YBCO layers were patterned as microbridges commonly used in device applications and DC resistance–temperature measurements were applied. As shown in Fig. 3, critical temperatures for the three samples are almost the same around 85 K which is the same T c values for thin film measurements (see Figs. 1 and 3 for comparison).

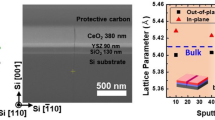

In Figs. 4 and 5, XRD analysis of YSZ/Si and CeO2/YSZ/Si structures is given, respectively, and those were deposited at 800 ∘C on (100) single-crystal Si substrates. As shown in Fig. 4, the (111) peak at 30 ∘, (100) peak at ∼35∘ , and (220) peak at 50∘ indicate the polycrystalline formation of YSZ thin film on Si wafer. The highest intensity was observed with the (111) peak at 30 ∘ showing the crystal alignment YSZ thin film which is mostly in the (111) direction. In order to decrease polycrystalline peak intensities and increase single crystallinity (mostly c-axis orientation), there are two fundamental things that can be done.s

One can increase the deposition temperature, which is not valid in this case for us because 800 ∘C is the highest deposition temperature for YSZ thin film we could reach. The latter is a lowering partial O2 pressure during deposition [15, 19]. In our case, 2 mTorr O2 was introduced into the sputtering chamber during the deposition process. According to Engang F. (2005, PhD thesis), lowering the oxygen pressure increases the intensity of (100) peak while decreasing the (111) peak intensity [15].

In Fig. 5, XRD analysis of CeO2/YSZ/Si structure is given. It is seen from the figure that CeO2 was grown in the same crystal formation with YSZ thin film, because the (111) peak at ∼28.5∘ has the highest intensity for CeO2 thin film which was the crystal growth orientation of YSZ. There is also another (220) peak seen at 48∘ which is quite narrow and intense. In Fig. 3, there is a peak at 35∘ which is the YSZ (100) peak reflected from the lower layer. Another YSZ peak supposed to be at 30∘ in the (111) direction which was quite intense in Fig. 4, but it almost disappeared after CeO2 deposition. The reason of this result might be the annealing of lower layers during the CeO2 thin film deposition at high temperatures.

In SEM images as shown in Fig. 6a, b for YSZ/Si and CeO2/YSZ/Si structures, granular and defectless surfaces are seen. In Fig. 6b, the grain size and the boundaries are seen much more clear, that is an important positive effect of CeO2 film deposition on crystal quality of the whole structure.

4 Conclusion

Superconducting YBCO thin films were fabricated on silicon substrates in the form of YBCO/CeO2/YSZ/Si multilayer structure. CeO2/YSZ bilayer was deposited on Si as buffer layers in order to minimize mismatch on lattice parameters and thermal expansion coefficients between YBCO and CeO2/YSZ/Si stack. The superconducting phase transition profile and critical temperature were characterized by means of DC resistance–temperature and AC magnetic susceptibility measurements which were applied for the three different samples that were fabricated by using exactly the same parameters in order to prove the reproducibility of our optimization. Then, the device fabrication processes were applied and the stability of the YBCO/CeO2/YSZ/Si multilayer structure and the possible changes of superconducting transition temperatures were tested. According to measurements, quite sharp phase transitions were obtained for three different samples at 85 K and any degradation on T c after device fabrication was not observed. XRD analysis and SEM micrographs show the granular and polycrystalline formation for both YSZ/Si and CeO2/YSZ/Si structures. As a result, it was understood that enhancement of the critical temperature of the YBCO is closely related with the crystal formation, thicknesses, and deposition temperature of each layer in our structure. Therefore, we concluded that further optimization is still needed to be done in order to obtain superconducting YBCO thin film with 90 K critical temperature and having single-crystal orientation by manipulating deposition parameters and film thicknesses and using another two-layer buffer which has a closer lattice parameter and thermal expansion coefficient to YBCO. With this optimization, we have planned to fabricate YBCO step-edge Josephson junctions and DC SQUIDs on Si as future works.

References

Petersen, K.E.: Silicon as a mechanical material. Proc. IEEE 70, 420–457 (1982)

Bin, M., Gaidis, M.C.: Low-noise 1 THz niobium superconducting tunnel junction mixer with a normal metal tuning circuit. Appl. Phys. Lett. 68, 1714–1716 (1996)

Grant, P.M., Sheahen, T.P.: Cost projections for high temperature superconductors. Appl. Supercond. Conference Paper, Palm Desert, CA (1998)

Navacerrada, M.A., Lucia, M.L.: Structural image of the barrier of YBCO grain boundary Josephson junction based on the analysis of the electromagnetic parameters. IEEE Trans. on Appl. Supercond. 19, 2863–2866 (1997)

Wu, C., Jhan, F., Chen, J.: Fabrication and properties of high-Tc YBCO Josephson junction and SQUID with variable thickness bridges by focused ion beam. IEEE Trans. on Appl. Supercond. 21, 375–378 (2011)

Wolf, T.: YBCO Josephson junctions and striplines for RSFQ circuits made by ion irradiation. IEEE Trans. Appl Supercond. 23(1101205), 1–3 (2013)

Probst, P., Semenov, A., Ries, M.: Nonthermal response of YBCO thin films to picosecond THz pulses. Phys. Rev. B. 85(174511), 1–8 (2012)

Il’in, K.S., Siegel, M.: Microwave mixing in microbridges made from YBCO thin films. J. Appl. Phys. 92, 361–369 (2002)

Avci, I., Tepe, M., Abukay, D.: Effect of deposition conditions on YBCO thin films by inverted cylindrical magnetron sputtering and substrate effects. Solid State Commun. 130, 357–361 (2004)

Kumar, A., Narayan, J.: Superconducting YBCO thin films on Si(100) substrates with CoSi2 buffer layers by an in situ pulsed laser evaporation method. Appl. Phys. Lett. 59, 1785–1787 (1991)

Jaekel, C., Kyas, G., Roskos, H.G.: Microwave properties and strain-induced lattice defects of c-axis-oriented YBCO thin films on silicon. J. Appl Phys. 80, 3488–3492 (1996)

Scheuring, A., Dean, P., Valavanis, A.: Transient analysis of THz-QCL pulses using NbN and YBCO superconducting detectors. IEEE Trans. THz Sci. Technol. 3, 172–179 (2013)

Prusseit, W., Corsepius, S.: Epitaxial YBCO films on silicon using combined YSZ/Y2O3 buffer layers. Phys. C 201, 249–256 (1992)

Shimakage, H., Kawakami, A., Wang, Z.: Deposition of YBCO thin films on MgO buffer layer fabricated on Si substrates. IEEE Trans. on Appl. Supercond. 9, 1645–1648 (1999)

Engang, F.: Study of epitaxial thin films of YBCO on silicon with different buffer layers. Master of Philosophy Thesis, The University of Hong Kong (2005)

Qiao, J., Yang, C.Y.: High-Tc superconductors on buffered silicon: materials properties and device applications. Mater. Sci. Eng. R14, 157–202 (1995)

Tian, Y.J., Linzen, S., Shimidl, F., Seidel, P.: Large-area YBCO Films for device fabrication. Supercond. Sci. Technol. 11, 59–62 (1998)

Tian, Y.J., Linzen, S., Schmidl, F.: On ageing and critical thickness of YBCO films on Si with CeO2/YSZ buffer layers. Thin Solid Films 338, 224–230 (1999)

Chiodoni, A.M.: Multilayers characterization for semiconductor-superconductor integration, PhD Thesis (2005)

Avci, I., Kuran, O., Uzun, Y.: Performance analysis of direct gold wire bonding on superconducting YBCO thin films and devices. IEEE Trans. Appl. Supercond. 1200206, 1–6 (2015)

Gao, J., Fu, E.G., Kang, L.: Highly heteroepitaxial thin films of YBCO grown on silicon with ECO/YSZ bi-layer buffer. Thin Solid Films 516, 6469–6475 (2008)

Mai, Z.H., Chen, X.M., Wang, Y.: Microstructures of epitaxial thin films of YBCO deposited on silicon wafers. Supercond. Sci. Technol. 16, 590–594 (2003)

Acknowledgments

This work was supported by the TÜBİTAK under the project number 114F165. The authors would like to thank Dr. Fatma Nur Tuzluca from the Erzincan University and the researchers at the Erzincan University Central Research Laboratory for the XRD and SEM analysis.

Author information

Authors and Affiliations

Corresponding author

Additional information

The work has been done in Faculty of Science, Department of Physics, Ege University.

Rights and permissions

Open Access This article is distributed under the terms of the Creative Commons Attribution 4.0 International License (http://creativecommons.org/licenses/by/4.0/), which permits unrestricted use, distribution, and reproduction in any medium, provided you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made.

About this article

Cite this article

Uzun, Y., Kuran, O. & Avci, I. Fabrication of Superconducting YBa2Cu3O7−x Thin Films on Si Wafer via YSZ/CeO2 buffer layers. J Supercond Nov Magn 30, 2335–2340 (2017). https://doi.org/10.1007/s10948-016-3846-y

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10948-016-3846-y