Abstract

In this paper, we present a comprehensive comparison study between p-n and p-i-n vertical diodes employing diverse heterojunction configurations under dark conditions. The diodes are fabricated utilizing p-PMItz as the organic semiconductor layer interfacing with different inorganic substrates, including n-Si (n-type silicon), n-4HSiC (n-type 4H silicon carbide), and incorporating an intrinsic SiO2 (silicon dioxide) layer in the p-PMItz/i-SiO2/n++-Si configuration. The current–voltage and dielectric characteristics are analyzed to discern the performance discrepancies among these diode configurations. The influence of heterojunction interfaces and band alignments on device behavior is investigated, shedding light on the charge transport mechanisms within these structures. Our findings reveal distinct trends in device characteristics for p-n and p-i-n diodes, highlighting the significance of heterojunction design in optimizing device performance. This comparative analysis offers valuable insights for the development of efficient organic–inorganic hybrid diodes tailored for various optoelectronic applications.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

Ongoing research in the field of p-n and p-i-n junctions with organic semiconductors involves the development of hybrid organic/inorganic semiconductor heterojunctions, which can expand the scope of purely organic or inorganic junctions [1]. These hybrid junctions can be used in various electronic and optoelectronic devices, such as solar cells, diodes, and transistors [2,3,4,5]. One approach to creating these hybrid junctions is through doping semiconductors, which can optimize the functionality of these devices [6, 7]. Organic semiconductor diodes fabricated using doped/undoped (high-low) homojunction structures have shown promise in providing controlled and high-quality current [8].

The concept involves positive and negative charges from ionized donors and acceptors in n-type and p-type organic semiconductors, respectively, creating a mixed i-layer co-deposited with both types of semiconductors [9]. Organic semiconductor diodes can be built in various architectures, including p-n-diodes, p-i-n-diodes, and Schottky diodes, each serving specific functions. There has been extensive research and investigation into the possible applications of multi-junction-based organic semiconductor devices, which are characterized by organic semiconductors grown on inorganic wafers [10, 11]. Increasing mobility in both vertical and lateral directions is crucial to enhance organic semiconductors' performance in complex multi-junction devices. This can be achieved by introducing structural order through organic polycrystals and single crystals, enabling band-like charge transport and maximizing charge carrier mobility [12]. Organic semiconductors are versatile materials used in various applications like OLEDs, solar cells, transistors, and sensors, with the potential for electrically driven organic lasers, overcoming challenges associated with low current densities and losses due to charge injection [13]. Overall, ongoing research in this field aims to improve the performance and functionality of electronic and optoelectronic devices by optimizing the properties of organic and hybrid semiconductor p-n and p-i-n junctions.

To describe charge transport mechanisms in diverse materials, however, there exist a number of models, including Poole–Frenkel, Schottky, and space charge limited-conduction (SCLC) mechanisms [14]. Carrier trapping centers exist in prohibited bandgaps, which have a significant impact on the electrical characteristics of semiconductor semiconductors. In the space charge limited-current model, current has a power-law dependence on applied voltage (I ∝ Vm), and this model is used to describe the electrical properties of semiconductor and insulator materials [15]. A prior work examined some surface and optoelectronic properties of phenanthroimidazole derivative (PMItz), an organic semiconductor of the p-type [16].

Overall, using of a new organic layer (p-PMItz), the device architecture of p-n and p-i-n diodes can impact their performance, making them a promising alternative to traditional inorganic diodes for device applications. The choice of electrodes and p-PMItz organic layer can also impact their current–voltage (I–V) and capacitance–voltage (C–V) characteristics, with In (indium) and Ag (silver) being commonly used for the anode and cathode, respectively. In this study, we provide an extensive comparative analysis of p-n and p-i-n vertical diodes using various heterojunction arrangements. An intrinsic SiO2 (silicon dioxide) layer is incorporated in the p-PMItz/i-SiO2/n++-Si configuration, and the diodes are manufactured using p-PMItz as the organic semiconductor layer interacting with various inorganic substrates, such as n-Si (n-type silicon) and n-4HSiC (n-type 4H silicon carbide).

2 Material and methods

The material and methods section outlines the systematic approach to developing and characterizing vertical diodes composed of p-PMItz/n-semiconductor and p-PMItz/i-SiO2/n-semiconductor heterojunctions. Conducted an extensive literature review to understand existing knowledge about vertical diodes. Identified key research gaps, challenges, and potential improvements.

-

Material Selection and Preparation:

-

Selected appropriate semiconductor material for heterojunction.

-

Synthesized p-PMItz and characterized its properties [17].

-

Prepared semiconductor material and p-PMItz in suitable forms for device fabrication.

-

-

Device Fabrication:

-

Designed the structure of vertical diodes based on p-PMItz/n-semiconductor and p-PMItz/i-SiO2/n-semiconductor heterojunctions.

-

Fabricated devices using standard semiconductor fabrication techniques, including deposition, lithography, and etching.

-

-

Characterization Techniques:

-

Implement various characterization techniques to evaluate the structural and electronic properties of the fabricated diodes.

-

Use techniques such as scanning electron microscopy (SEM), and Optical Bandgap analyze

-

-

Device Testing:

-

Set up experimental conditions to test the electronic characteristics of the diodes.

-

Measure the generated electrical signals.

-

Evaluate the diode performance parameters.

-

-

Optimization:

-

Iterate the fabrication and testing process to optimize the performance of the diodes.

-

Adjust parameters such as layer thickness, material composition, and device architecture based on the experimental results.

-

-

Data Analysis:

-

Analyze the collected data using statistical and graphical methods.

-

Compare the results with existing literature and discuss the significance of findings.

-

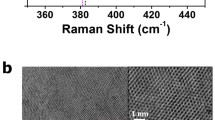

2.1 Optical bandgap of p-PMItz

To find PMItz’s bandgap, the fluctuation of (αhv)2 with energy (hν) was plotted. PMItz absorption measurements were used for this. Figure 1 shows the graph PMItz (αhν)2–(hν). Based on the information gleaned from the graph, 3.02 eV was determined to be the optical bandgap (Eg).

2.2 Experimental procedure

In this process, n-Si, i-SiO2/n++-Si, and n-4HSiC substrates were utilized to fabricate the devices. All materials underwent cleaning in an ultrasonic bath containing a soapy water solution for 10 min. Subsequently, the substrates were thoroughly rinsed with ultrapure water. i-SiO2/n++-Si substrates were not subjected to further cleaning and were dried with nitrogen gas after removal from the solution. n-Si and n-4HSiC substrates were immersed in acetone in a glass beaker and underwent ultrasonic cleaning for 10 min. Following cleaning with acetone, the n-Si and n-4HSiC substrates were transferred to a glass beaker filled with propanol and underwent another 10 min of ultrasonic cleaning. After cleaning with propanol, the surfaces of the n-Si and n-4HSiC substrates were dried with nitrogen gas, completing the substrate cleaning process.

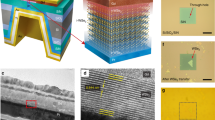

Before deposition of Ag (silver) and In (indium) contacts, about 99.9% purities, were deposited onto p-PMItz using the PVD (Physical Vapor Deposition) method. Ag contact deposition was performed using a Tungsten spoon crucible at a pressure of 5.3 × 10–5 Torr and a temperature of 21 °C. In contact deposition was carried out using a molybdenum spoon crucible at a pressure of 2.0 × 10–5 Torr and a temperature of 21 °C. The contacts were masked and cast in circular form with a diameter of approximately 0.777 mm. Six devices have been fabricated as illustrated in Fig. 2.

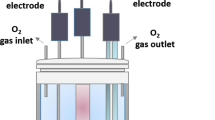

In order to analyze the electrical properties of these devices, I-V measurements were carried out at room temperature using a Keithley 2400 source meter. Figure 3 illustrates the workings of the system.

3 Results and discussion

3.1 Main electronic characteristics

The current-conduction (CC) mechanism in the semiconductor devices is dependent on many factors such as the organic film, its thickness and permittivity, homogeneity of barrier height, the level of doping atoms into semiconductor, series (Rs) and shunt (Rsh) resistances, surface states/traps, located at the interface of organic layer/semiconductor, surface cleaning of semiconductor wafer, fabrication processes and formation of electrode contacts even at in same conditions. The standard thermionic emission (TE) model was generally used using the forward bias I–V measurements to investigate the CC mechanism in these structures. However, it usually deviated from the TE model for the above reasons [18, 19].

Based on I–V measurements conducted in the ambient environment of our fabricated device, we plotted the I–V characteristics curve in dark conditions for various contacts. Figure 4 illustrates the plot depicting the I–V characteristics of the devices for both forward and reverse bias at room temperature. This confirms that the device exhibits appropriate rectifying diode-like behavior, which can be analyzed using the TE theory. According to this theory, current flow is governed by majority carriers overcoming a potential barrier, where only electrons with energy surpassing the barrier contribute to the current. By maintaining the turn-on voltage at approximately 0.3 V, which is lower than the applied bias voltage, the current increases rapidly in response to the bias voltage, indicating typical diode behavior.

As depicted in Fig. 4, the diode exhibits an exponential increase in forward bias current with voltage, whereas the reverse bias current remains low and relatively independent of voltage. The devices demonstrate good rectifying behavior under dark conditions, as illustrated in Fig. 4. These characteristics provide information about the p-PMItz/n-Si, p-PMItz/n-4HSiC and p-PMItz/i-SiO2/n++-Si heterojunctions parameters, including the ideality factor (n), barrier height (ϕBo), and reverse saturation current (Io). The I–V behaviors of organic/inorganic heterojunctions are indicated. At low voltages, these junctions exhibit characteristics similar to Schottky diodes or heterojunctions [18]. The widely recognized nearly perfect equation describing the relationship between I and V can be expressed as [18]:

In this context, \(n\) represents the ideality factor, \({I}_{O}\) signifies the reverse saturation current, \(V\) denotes the applied bias voltage, q stands for the electronic charge, equivalent to 1.602 \(\times \)10–19 \(C\), \(k\) represents the Boltzmann constant, which amounts to 1.3806 \(\times \)10–23 \(\frac{J}{K}\), \(T\) indicates the absolute temperature measured in Kelvin, \({R}_{s}\) denotes the series resistance of the diode, and the term \(I{R}_{s}\) represents the voltage drop across the \({R}_{s}\). [18]. The value of \({I}_{O}\) can be derived from the portion of the straight-line intercept of ln \(I-V\) curves at \(V=0\), and it is provided by:

Here, A represents the rectifier contact area, which is equal to \(7.85\times 1{0}^{-3}c{m}^{2}\), and A* signifies effective Richardson constant (112 A.(K.cm)−2 for n-Si and 146 A.(K.cm)−2 for n-4H-SiC. The value of the zero-bias or apparent barrier height \({\phi }_{BO}\) can be determined using Eq. (3). The n values for these diodes were also computed from the linear portion of the \(\mathit{ln}I-V\) plots, which can be expressed as follows [18]:

In Eq. 3; the d, εi, εs, Wd, and Nss quantities are the interlayer thickness, dielectric of interlayer, dielectric of semiconductor, and surface states, respectively. Consequently, the value of \({\phi }_{BO}\) is computed from Eq. 2 using the obtained values of \({I}_{O}\) and \(A\) for each diode as follows [18]:

The \({\phi }_{BO}\), n, Rs, Rsh, and rectifier ratio (RR) values were computed for the entire devices and each contact, as presented in Table 1. Among devices B, D, E, and F with p-n structure with different metal contacts, it has been observed that in devices with p-PMITz/n-Si junctions, the n and Io values of Device B are lower than Device F, and the ϕBO and RR values are higher. Better results were observed for Device B with Ag metal contact of the same junction. On the other hand, in devices with p-PMITz/n-4HSiC junctions, the ϕBO, n and Io values of Device D and Device E are seen to be close to each other and exhibit contact-based differences. It has been observed that the RR output of devices D and E is higher than the other devices, and their values show different results despite having the same junction structures. Additionally, the values of n are considerably higher than unity. On the other hand, in devices with p-PMITz/i-SiO2/n++-Si insertions, the n values of Device C are higher than in other devices, besides contact-based differences. Although it is expected that the n value should be unity in the ideal case, it is considerably different in practical applications due to the native/deposited interfacial layer, its εi and d values, Nss, doping atoms (acceptor/donor) or depletion layer width as expressed as [n = 1 + (di/εi)(qNss + εs/Wd)] [18]. The n values of inhomogeneous devices with a distribution of lower BHs or patches may be dominated by current flowing through lower barriers, leading to an increase in the current.

Additionally, it was observed that ϕBO and RR values were lower than other devices. The observed discrepancies between basic electrical parameters are usually rooted in the voltage-dependent, the used calculated method, which corresponds to different voltage ranges, barrier inhomogeneity, a special distribution of Nss and dislocations at the junction, and interfacial layer. As seen in Eq. 3, higher values of Nss, interlayer thickness, low-dielectric interlayer, and also barrier inhomogeneity yield an important increase in n value. Even if these diodes are grown under the same conditions and on the same semiconductor, they may give different results due to reasons such as the shape of the barrier, the thickness and inhomogeneity of the interfacial layer, and the inhomogeneous distribution of dopant atoms.

The parameters of Rs and Rsh are crucial for assessing device quality and impacting the performance of diodes. Diodes possess Rs and an interlayer, leading to the distribution of the total applied voltage among them and the depletion layer. Consequently, the reliability and quality of these devices are particularly associated with the interlayer, Rs and Rsh. Ideally, Rs and Rsh values are expected to be 0 and exceed 109Ω respectively, in an ideal scenario [20]. However, practical circumstances often deviate from this ideal. Various methodologies exist in research to compute \({R}_{s}\) parameters for Schottky diodes or heterojunctions, including Ohm's law, the Cheung and Cheung method utilizing forward bias \(I-V\) parameters of diodes, and Norde methods. These approaches are employed to yield reliable and valid results for \({R}_{s}\), which are subsequently compared across different diodes, with Rs and \({R}_{sh}\) parameters initially deduced from the forward bias region and the reverse bias region of the \(I-V\) parameters, respectively, utilizing Ohm's law, which are shown in Fig. 5.

3.2 Dielectric characteristics

The \(C-V-f\) and \(G-V-f\) outputs of the configuration were acquired at ambient conditions and are depicted in Fig. 6a and b. In this representation, the accumulation capacitance registered at 3 V shifts from 26.4 to 510 nF. By examining the outcomes aligned to the accumulation, depletion, and inversion regions, the capacitance of the configuration escalates with rising voltage but steadily diminishes towards the intense opposite domain. Additionally, the capacitance in the accumulation and depletion regions decreases with rising frequency. Through varying frequencies, electronic parameters such as diffuse potentials (\({V}_{D}\)), donor density (\({N}_{D}\)), and the depletion region width (WD) are computed from the C−2–V–ƒ curve. The intersection points with the voltage axis provide the built-in voltage (\({V}_{bi}\)) values, which are presented in Table 2. For a comprehensive analysis of capacitance, the C−2–V relationship is elucidated utilizing the following correlation. [18, 21]:

In this context, \({V}_{R}\), \(q\), \({\varepsilon }_{s}\), \({\varepsilon }_{0}\), and \(A\) denote the reverse bias voltage, the elementary charge, the dielectric constants of the semiconductor and vacuum, and the Schottky contact area, respectively. Upon assessment, it was observed that the \({C}^{-2}-V-f\) curves, representing capacitance versus voltage at various frequencies, exhibited linear characteristics and were almost parallel to each other within the voltage range of − 2 to 2 V. By plotting gradient lines for each frequency and obtaining their equations, the \({V}_{D}\) and the \({N}_{D}\) values are calculated based on the intersection points with the voltage axis, representing the built-in voltage \({V}_{bi}\) values, for each frequency. The \({V}_{bi}\) values of the configuration typically range from approximately 1.0–2.0 V and demonstrate increased sensitivity with higher frequencies.

The \({V}_{D}\) diffusion potential for each frequency value is inferred from \({V}_{bi}\) obtained from the \({C}^{-2}-V-f\) graph. [18]:

The WD, derived from the points where the C−2–V–ƒ curves intersect and their gradients [18]:

In theory, the Fermi level (EF) of a Schottky diode or heterojunction structure is [18]:

In this scenario, the effective density of states (\({N}_{c}\)) at the conduction band equals \(4.82 \times 1{0}^{15}{T}^{1.5}{({m}_{e}^{*}/{m}_{0})}^{1.5}\). The ratio of the effective electron mass for silicon is 1.08. Moreover, the \(\frac{kT}{q}\) represents the thermal energy [22]. Furthermore, the relationship between the barrier height \({{\phi }_{B}}_{\left(C-V\right)}\), \({V}_{D}\), \({E}_{F}\), and \(\Delta \,\phi_{B}\) is provided in Eq. 9:

Here, \(\Delta \,\phi_{B}\) represents the reduction of the image force barrier lowering and can be computed in the following manner [18]:

In Eq. 10, \({E}_{m}\) denotes the electric field and can be determined using the subsequent correlation [18]:

By utilizing the \(C-V-f\) outputs, all electronic parameters were determined using the aforementioned calculation methods and are detailed in Table 2. In this context, the \({W}_{D}\), \({{\phi }_{B}}_{\left(C-V\right)}\), \(\Delta \,\phi_{B}\) and \({E}_{m }\) parameters were noticed to rise with ascending frequency (see Fig. 6). Experimentally, the values dependent on frequency exhibit significant variation at ambient conditions. Specifically, the \({N}_{D}\), \({W}_{D}\), and \({{\phi }_{B}}_{\left(C-V\right)}\) values experience changes within the ranges of \(8.23-3.83\times 1{0}^{14}c{m}^{-3}\), 512–666 \(nm\), and 1.728–2.969 \(eV\), respectively, with increasing frequency. The higher values of \({\phi }_{B}\) can be explained by the higher intercept voltage (Vbi) values due to the high doping donor atoms and native/deposited interfacial layer.

When analyzed concerning the applied frequency (\(\omega =2\Pi f\)), Nicollian and Brews introduced the equivalent admittance characterized by the parallel capacitance (Cm) and conductance (Gm/ω) as defined in Eq. 12 [23, 24];

The Cm and Gm/ω results of Device B corresponding to the accumulation, depletion, and inversion regions are illustrated in Fig. 6a and b. The Cm and Gm/ω values demonstrate a gradual decrease towards the strong inversion region, while they indicate an increase in the strong accumulation region with increasing voltage.

As the frequency increases, the peaks of Cm and Gm/ω values diminish within the robust accumulation zone and relocate towards the area of accumulation. By employing the capacitance and conductance measured in the robust accumulation area, defined as Cma and Gma, the series resistance (Rs) can be computed using the subsequent equation [23]:

where when \({C}_{ox}\) is represented as follows when \({C}_{\text{ma}}={C}_{\text{ox}}/(1+{\omega }^{2}{R}_{s}^{2}{C}_{ox}^{2})\) is substituted within Eq. 13:

where \({\varepsilon }_{i}=11.8{\varepsilon }_{o}\) and \({\varepsilon }_{o}=8.85x1{0}^{-14}F/cm\). A represents the rectifier contact area and is equivalent to \(7.8539x1{0}^{-3}c{m}^{2}\). When utilizing the second part of the equation mentioned above, the calculated layer thickness (δ) is determined to be 412 nm at 100 kHz. Additionally, the PMItz thickness measured using SEM described in Fig. 2 is in the range of 302 nm to 410 nm while the δ value calculated from Eq. 14 is in good agreement.

Utilizing Eq. 13, the \({R}_{s}-V-f\) graph is depicted in Fig. 6c. Observationally, \({R}_{s}\) values decrease as frequency increases in the reverse biasing region. Moreover, they demonstrate voltage independence for high frequencies. The \({R}_{s}\) values vary in practice, contingent upon both frequency and applied voltage, owing to the distribution of interface trap state density (Nss). The value of Nss in the voltage range is computed in Fig. 6d. With a voltage range change from − 3 to 3 V, the Nss values, in this case, change from 1.1 × 1010 to 1.98 × 1011 cm−2 eV−1. According to these findings, Nss is located between the metal/p-PMItz and p-PMITz/n-type Si in two distinct zones.

Dielectric properties are crucial in electronic devices based on capacitors and transistors. Hence, the dielectric constant \({\varepsilon }{\prime}\), dielectric loss \({\varepsilon }^{^{\prime\prime} }\), loss angle \(\mathit{tan}\delta \), \(a.c.\) electrical conductivity \({\sigma }_{ac}\), and magnitudes of the real and imaginary parts \({M}{\prime}\) and \({M}^{^{\prime\prime} }\) of the complex electric module can be determined using the Cm and Gm/ω outputs. Relative dielectric permittivity (\({\varepsilon }^{*}\)), representing the interaction between the electric field and the material in a complex form, is expressed as follows [25, 26]:

where \({\varepsilon }{\prime}\) and \({\varepsilon }^{^{\prime\prime} }\) also denote the stored and expended energy, respectively. The real part (\({\varepsilon }{\prime}\)) of \({\varepsilon }^{*}\), in a wide range of frequencies in the strong accumulation area (\({V}_{G}>0\)) can be calculated using the following equation [24,25,26]:

where \({C}_{o}\) represents the capacitance magnitude of an empty capacitor and is determined by \({C}_{o}\)= \({\varepsilon }_{o}\) (\(\frac{A}{d}\)). In this equation, A denotes the area of the rectifier contact, and d represents the organic layer's thickness, which equals 412 nm. The imaginary part (\({\varepsilon }^{^{\prime\prime} }\)) of the complex form, depicting dielectric dissipation related to energy dissipation, is established through conductivity measurements. Dielectric dissipation peaks when \(\omega =\frac{1}{\tau }\) and must be minimized for thin film layers, significantly influencing device performance. The expression for dielectric dissipation ε'' is given as follows [25, 26]:

where Gm represents the conductivity of the structure and ω is the angular velocity. By utilizing the imaginary (\({\varepsilon }^{^{\prime\prime} }\)) and real (\({\varepsilon }{\prime}\)) parts of the permittivity, the loss angle \(\mathit{tan}\delta \) values can be calculated as follows [30]:

Figure 7 illustrates the characteristics of ε′, ε′′, and tan δ of the heterojunction structure as a function of frequency within the voltage range of − 3 V to + 3 V. In Fig. 7a, the ε′ values in the accumulation region increase with decreasing frequency up to 10 kHz. Additionally, a little change is observed in \({\varepsilon }{\prime}\) values at the inversion region. These increments are attributed to \({N}_{ss}\) surface and dipole polarizations at low frequencies up to 10 kHz, while they are caused by the \({R}_{s}\) at higher frequencies [27]. Cm and Gm/ω characteristics are measured at different frequencies.

The ε" values in Fig. 7b show a comparable peak for low frequencies (f ≤ 10 kHz) in the depletion region, peaking approximately 0.5 V. The limited number of majority carriers positioned between the bandgap change from reverse bias voltage to forward bias voltage is the cause of this phenomenon. Nss and interface polarization are responsible for such peak behaviors at low frequencies in the inversion and depletion regions of the ε'–V and ε″–V parameters [26].

In the forward bias region of Figure 7c, the loss tangent (tanδ) value increases up to 1000 kHz, while in the reverse bias region, there is little change. On the other hand, the peak values that are observed first rise and then fall at 10 kHz. The aforementioned phenomena can be explained by the produced device's capacitance and conductance values being sensitive to the series resistance and interface quality [26].

Based on ε*, the components of the complex electric modulus (M*) are divided into real (M') and imaginary (M") components as follows [28]:

The voltage-dependent M' and M" values at the wide-ranged frequency are computed and expressed in Fig. 7d and e using Eq. 19. It is evident that frequency substantially impacts the M' and M'' values in this case. Furthermore, M'' values exhibit a peak in the depletion region and a maximum value as the frequency increases.

The \(a.c.\) electrical conductivity (\({\sigma }_{ac}\)) of organic layer is a vital parameter providing insights into the material properties and is determined using the following equation [29]:

As frequency increases, Fig. 7f clearly shows an increase in σac. This increase is thought to be caused by the polarization decreasing with frequency. More carriers contribute as polarization decreases, which increases a.c. conductivity and decreases polarization, increasing σac. It is noticed that σac is voltage-independent at low frequencies and changes voltage dependently at high frequencies.

Using the organic layers in heterojuncions, the electronic characteristics of vertical diodes are developed by evaluating the dielectric characteristics in detail. Therefore, considerable research has been done on the performance of dielectric characteristics in the literature. Table 3 presents Device B's maximum dielectric constant εmax′ values based on p-PMItz/n-Si. Notably, the dielectric constant \({\varepsilon }_{max}{\prime}\) value of the p-PMItz thin film is 0.16 at 10 kHz.

3.3 Energy band diagram

Schematic energy band diagram models of p-n and p-i-n vertical devices employing diverse heterojunction configurations are presented in Fig. 8. The diodes are fabricated utilizing p-PMItz as the organic semiconductor layer interfacing with different inorganic substrates, including n-Si (n-type silicon), n-4HSiC (n-type 4H silicon carbide), and incorporating an intrinsic SiO2 (silicon dioxide) layer in the p-PMItz/i-SiO2/n++-Si configuration. Here, the device's band alignment, interlayer, and Fermi level energy are demonstrated. In previous study, the fabricated devices have a bandgap of 3.02 eV (Eg) [16]. It is shown from the band diagram that the devices are electron–hole pairs. Electrons in the conduction band and holes in the valence band are shown. This has the potential to create a flow of electrons and holes. Thus, bias was created by transporting electrons with this flow.

4 Conclusion

In conclusion, our comparative study of p-n and p-i-n vertical diodes utilizing different heterostructure configurations based on p-PMItz/n-Si, p-PMItz/n-4HSiC, and p-PMItz/i-SiO2/n++-Si sheds light on the intricacies of organic–inorganic heterojunction devices under dark conditions. Through comprehensive analysis of I-V and dielectric characteristics, we have elucidated the distinct performance attributes arising from variations in heterojunction interfaces and band alignments. We observed unique trends in device characteristics for p-n and p-i-n diodes, indicative of different charge transport mechanisms governed by the specific heterojunction configurations. The incorporation of an intrinsic SiO2 layer in the p-PMItz/i-SiO2/n++-Si configuration introduces additional complexity but offers intriguing possibilities for tailoring device properties. These findings contribute to advancing our understanding of organic–inorganic heterojunction devices and provide valuable insights for optimizing their performance in vertical diode applications. Future research directions may support further refinement of heterojunction design, investigation of device stability under various operating conditions, and exploration of novel materials and architectures to harness the full potential of organic–inorganic hybrid diodes.

Data availability

The data supporting this study’s findings is available from the corresponding author upon reasonable request.

References

M.H. Futscher, T. Schultz, J. Frisch, M. Ralaiarisoa, E. Metwalli, M.V. Nardi, P. Müller-Buschbaum, N. Koch, J. Phys. Condens. Matter 31, 064002 (2018)

C. Wang, X. Zhang, W. Hu, Chem. Soc. Rev. 49(3), 653–670 (2020)

J. Sun, K. Wang, K. Ma, J.Y. Park, Z.Y. Lin, B.M. Savoie, L. Dou, J. Am. Chem. Soc. 145(38), 20694–20715 (2023)

J. Chen, W. Zhang, L. Wang, G. Yu, Adv. Mater. 35(11), 2210772 (2023)

Z. Guo, J. Zhang, X. Liu, L. Wang, L. Xiong, J. Huang, Adv. Func. Mater. 33(46), 2305508 (2023)

D.C. Tripathi, Y.N. Mohapatra, Org. Electron. 13(9), 1680–1685 (2012)

S. Izawa, A. Perrot, J.H. Lee, M. Hiramoto, Org. Electron. 71, 45–49 (2019)

S. Kumar, D.C. Tripathi, Y.N. Mohapatra, Org. Electron. 50, 331–338 (2017)

M. Hiramoto, M. Kubo, Y. Shinmura, N. Ishiyama, T. Kaji, K. Sakai, T. Ohno, M. Izaki, Electronics 3(2), 351–380 (2014)

F. Yakuphanoglu, Physica B 388, 226–229 (2007)

M.M. Ahmed, K.S. Karimov, S.A. Moiz, IEEE Trans. Electron Devices 51, 121–126 (2004)

M. Sawatzki-Park, S.J. Wang, H. Kleemann, K. Leo, Chem. Rev. 123, 8232–8250 (2023)

K. Yoshida, J. Gong, A.L. Kanibolotsky, P.J. Skabara, G.A. Turnbull, I.D.W. Samuel, Nature 621(7980), 746–752 (2023)

K.C. Kao, W. Hwang, Electrical Transport in Solids with Particular Reference to Organic Semiconductors (Pergamon Press Ltd., Headington Hill Hall, 1981)

M.A. Lampert, P. Mark, Current Injection in Solids (Academic Press, New York, 1970)

M. Zurnacı, F. Ünal, S. Demir, M. Gür, N. Şener, İ Şener, New J. Chem. 45, 22678–22690 (2021)

M. Zurnacı, İ Şener, M. Gür, N. Şener, J. Fluoresc. 32, 1155–1169 (2022)

S.M. Sze, Physics of Semiconductor Devices, 2nd edn. (Wiley, New York, 1981)

H.H. Radamson, A. Hallén, I. Sychugov, A. Azarov, Analytical Methods and Instruments for Micro- and Nanomaterials (Springer, Berlin, 2023)

H. Ferhati, F. Djeffal, K. Kacha, A. Bendjerad, A. Benhaya, Phys. E 106, 25–30 (2019)

O. Çiçek, G. Koca, Ş Altındal, IEEE Trans. Electron Devices 69, 304–310 (2021)

C. Kittel, Introduction to Solid State Physics (Wiley, USA, 2005)

J.E. Nicollian, MOS(Metal Oxide Semiconductor Physics and Technology) (Bell Telephone Laboratories, Holmdel, 1982), pp.117–129

S.A. Yerişkin, G.E. Demir, I. Yücedag, J. Nanoelectron. Optoelectron. 14(8), 1126–1132 (2019)

V.V. Daniel, Dielectric Relaxation (Academic Press, 1967), pp.1–36

C.P. Symth, Dielectric Behaviour and Structure (McGraw-Hill, New York, 1955)

A. Chelkowski, Dielectric Physics (Elsevier, Amsterdam, 1980)

M.D. Migahed, M. Ishra, T. Fahmy, A. Barakat, J. Phys. Chem. Solids 65, 1121–1125 (2004)

P. Pissis, A. Kyritsis, Solid State Ionics 97, 105–113 (1997)

Acknowledgements

This article is derived from research conducted as part of first author's doctoral thesis at the Institute of Science, Kastamonu University.

Funding

Open access funding provided by the Scientific and Technological Research Council of Türkiye (TÜBİTAK). The paper attracts no funding and has the authors’ own funding for this paper.

Author information

Authors and Affiliations

Contributions

AAA is involved in writing original drafts, validation, formal analysis, and conceptualization. OC is involved in writing, review and editing, supervision, methodology, investigation, formal analysis, and conceptualization.HM is involved in data curation and analysis. FÜ involved in samples preparation. MZ is involved in material synthesis, and PMItz film formation. ŞA involved in final manuscript checking and supervision.

Corresponding author

Ethics declarations

Competing interests

The authors have no relevant financial or non-financial interests to disclose.

Ethical approval

Not applicable.

Informed consent

Not applicable.

Consent for publication

Not applicable.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Alarabi, A.A., Çiçek, O., Makara, H. et al. Comparison of p-n and p-i-n vertical diodes based on p-PMItz/n-Si, p-PMItz/n-4HSiC and p-PMItz/i-SiO2/n-Si heterojunctions. J Mater Sci: Mater Electron 35, 957 (2024). https://doi.org/10.1007/s10854-024-12707-0

Received:

Accepted:

Published:

DOI: https://doi.org/10.1007/s10854-024-12707-0