Abstract

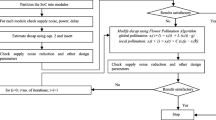

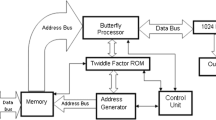

This article examines the signal integrity problem arising due to resistive drop, inductive noise and electro- migration, causing voltage fluctuations known as supply noise in an integrated circuit. Insertion of decoupling capacitor is a commonly used technique for reducing the supply noise. In this article symbiotic organism search (SOS) algorithm is used to estimate the decap. Another relevant issue addressed is the distribution of the decap over the chip. To get the best possible results in the post-layout stage pruning technique is used for partitioning and particle swarm optimization (PSO) algorithm is applied in the floorplanning stage. The purpose of this work is to reduce the supply noise without much affecting other design parameters of the chip. Simulation results show that supply noise has been reduced by up to 74.07% and the decap budget has been reduced by up to 37.4%. This approach can be used for any system-on-chip.

Similar content being viewed by others

References

Ayala HVH, Klien CE, Mariani VC, Coelho LS (2017) Multi-objective Symbiotic Organism Search Algorithm Approaches For Electromagnetic Optimization. IEEE Trans Magn 53(6):1–5. https://doi.org/10.1109/TMAG.2017.2665350

Chakraborty M, Saha D, Chakrabarti A, Bindai S (2019) A CAD Approach For Pre-layout Optimal Design And Its Post-layout Verification. Microprocess Microsyst, Elsevier 65:158–168

Chen S, Luk BL (2010) Digital IIR Filter Design Using Particle Swarm Optimization. Int J Model Identif Control, Inderscience Publishers 9(4):327–335

Das B, Mukherjee V, Das D (2016) DG Placement In Radial Distribution Network By Symbiotic Organism Search Algorithm for Real Power Loss Minimization. Appl Soft Comput 49:920–936

Das D (2005) VLSI Design, Second Edition, Oxford University Press, New Delhi.

Gudise VG, Venayagamoorthy GK (2004) FPGA Placement and Routing Using Particle Swarm Optimization, Proc. of IEEE Comp Soc Annu Symp VLSI, pp. 307–308.

Karim T (2012) On-Chip Power Supply Noise: Scaling, Suppression and Detection. Dissertation, Doctor of Philosophy (Electrical and Computer Engineering)’, University of Waterloo.

Mitra P, Bhaumik J (2019) A CAD Approach for Suppression of Power Supply Noise And Performance Analysis of Some Multi-core Processors in Pre-layout Stage. Microsyst Technol, Springer 25(5):1977–1986

Mitra P, Sarkar A (2020) Soft Computing Techniques Based CAD Approach For Power Supply Noise Reduction In System-on-Chip. J Electr Testing: Theory Appl, Springer 36(5):665–669

Pant S (2008) Design and analysis of Power Distribution Networks in VLSI Circuits. Dissertation, Doctor of Philosophy (Electrical Engineering), University of Michigan.

Shah K (2007) Power Grid Analysis in VLSI Designs. Dissertation, Master of Science (Engineering), Super Comp Educ Res Centre, Indian Institute of Science, Bangalore.

Zhao S, Roy K, Koh CK (2002) Decoupling Capacitance Allocation and Its Application to Power-Supply Noise-Aware Floorplanning. IEEE Trans Comput Aided Des Integr Circuits Syst 21(1):81–92

Acknowledgment

This work was supported by I.I.T. Kharagpur.

Author information

Authors and Affiliations

Corresponding author

Additional information

Responsible Editor: V. D. Agrawal.

Publisher’s Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Mitra, P., Bhaumik, J. & Sarkar, A. Decoupling Capacitor Estimation and Allocation using Optimization Techniques for Power Supply Noise Reduction in System-on-Chip. J Electron Test 37, 151–155 (2021). https://doi.org/10.1007/s10836-021-05931-7

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10836-021-05931-7