Abstract

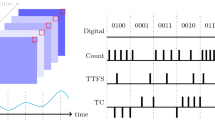

The Count Compatible Pattern Run-Length (CCPRL) coding compression method is proposed to further improve the compression ratio. Firstly, a segment of pattern in the test set is retained. Secondly, don’t-care bits are filled so as to make subsequent patterns compatible with the retained pattern for as many times as possible until it can no longer be made compatible. Thirdly, the compatible patterns are represented by symbol “0” (equal) and symbol “1” (contrary) in the codeword. In addition, the number of consecutive compatible patterns is counted and expanded into binary which indicates when the codeword ends. At last, the six largest ISCAS’89 benchmark circuits verify the proposed method, the experimental results show that the average compression ratio achieved is up to 71.73 %.

Similar content being viewed by others

References

Chandra A, Chakrabarty K (2001) System-on-a-chip test-data compression and decompression architectures based on golomb codes. IEEE Trans Comput Aided Des Integr Circ Syst 20(3):355–368

Chandra A, Chakrabarty K (2003) Test data compression and test resource partitioning for system-on-a-chip using frequency-directed run-length (fdr) codes. IEEE Trans Comput 52(8):1076–1088

Chandra A, Chakrabarty K (2003) A unified approach to reduce soc test data volume, scan power and testing time. IEEE Trans Comput Aided Des Integr Circ Syst 22(3):352–363

El-Maleh AH, Al-Abaji RH (2002) Extended frequency-directed run-length code with improved application to system-on-a-chip test data compression. In: 9th international conference on electronics, circuits and systems, vol 2. IEEE, pp 449–452

El-Maleh AH (2008) Efficient test compression technique based on block merging. IET Comput Digit Tech 2(5):327–335

Gonciari P, Al-Hashimi B, Nicolici N (2002) Improving compression ratio, area overhead, and test application time for system-on-a-chip test data compression/decompression. In: Confidential on design, automation and test in Europe. IEEE, p 604

Jas A, Ghosh-Dastidar J, Ng M-E, Nur AT (2003) An efficient test vector compression scheme using selective huffman coding. IEEE Trans Comput Aided Des Integr Circ Syst 22(6):797–806

Kavousianos X, Kalligeros E, Nikolos D (2007) Optimal selective huffman coding for test-data compression. IEEE Trans Comput 56(8):1146–1152

Lee L-J, Tseng W-D, Lin R-B, Chang C-H (2012) 2n-pattern run-length for test data compression. IEEE Trans Comput Aided Des Integr Circ Syst 31(4):644–648

Nourani M, Tehranipour MH (2005) Rl-huffman encoding for test compression and power reduction in scan applications. ACM Trans Des Autom Electron Syst 10(1):91–115

Ruan X, Katti R (2006) An efficient data-independent technique for compressing test vectors in systems-on-a-chip. In: IEEE computer society annual symposium on emerging VLSI technologies and architectures. IEEE, p 6

Tehranipoor M, Nourani M, Chakrabarty K (2005) Nine-coded compression technique for testing embedded cores in socs. IEEE Trans VLSI Syst 13(6):719–731

Touba NA (2006) Survey of test vector compression techniques. Des Test Comput IEEE 23(4):294–303

Tseng W-D, Lee L-J (2010) Test data compression using multi-dimensional pattern run-length codes. J Electron Test 26(3):393–400

Author information

Authors and Affiliations

Corresponding author

Additional information

Responsible Editor: M. Goessel

This research work was supported by the fund of NSFC(61001049), Key lab fund of ICT(CARCH201103)

Rights and permissions

About this article

Cite this article

Yuan, H., Mei, J., Song, H. et al. Test Data Compression for System-on-a-Chip using Count Compatible Pattern Run-Length Coding. J Electron Test 30, 237–242 (2014). https://doi.org/10.1007/s10836-014-5441-0

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10836-014-5441-0