Abstract

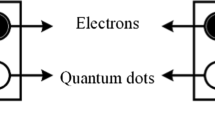

The Quantum Cellular Automata (QCA) technology was proposed in response to the limitations of CMOS technology. In addition, the full-adder cell (FAC) is a crucial part of arithmetic computing so that efficient designs can play a significant role. We designed a fault-tolerant FAC implemented on a single-layer, with no rotated or constant cells that significantly improve the design’s manufacturability. Moreover, to further simplify the manufacturing of our proposed circuit, we present a real clocking scheme that clusters the proposed design based on clock regions. Besides, the design can tolerate a single omission fault. As a result, the proposed design shows considerable complexity, area consumption, and energy dissipation improvements by almost 22.7%, 43.75%, and 21% in 1 Ek, respectively. Additionally, the proposed fault-tolerant FAC improves the complexity, area consumption, latency, and total energy dissipation by almost 22.5%, 8%, 33.33%, and 37.74% in 1 Ek compared to the cutting-edge QCA-based single-layer fault-tolerant FAC designs.

Similar content being viewed by others

Data Availability

Not applicable.

Code Availability

Not applicable.

References

Singh, G., Sarin, R.K., Raj, B.: Design and analysis of area efficient QCA based reversible logic gates. Microprocess. Microsyst. 52, 59–68 (2017)

AlKaldy, E., Majeed, A.H., Bin Zainal, M.S., Md Nor, B.: Optimum multiplexer design in quantum-dot cellular automata. Indones. J. Electr. Eng. Comput. Sci. 17, 148–155 (2020)

Ahmad, F., John, M.U., Khosroshahy, M.B., Sarmadi, S., Bhat, G.M., Peer, Z.A., Wani, S.J.: Performance evaluation of an ultra-high speed adder based on quantum-dot cellular automata. Int. J. Inf. Technol. 11, 467–478 (2019)

Abutaleb, M.: A novel power-efficient high-speed clock management unit using quantum-dot cellular automata. J. Nanopart. Res. 19, 128 (2017)

Majeed, A.H., Alkaldy, E., bin Zainal, M.S., Nor, B.M.: Synchronous counter design using novel level sensitive T-FF in QCA technology. J. Low Power Electron. Appl. 9, 27 (2019)

Moghaddam, M., Moaiyeri, M.H., Eshghi, M.: Design and evaluation of an efficient Schmitt trigger-based hardened latch in CNTFET technology. IEEE Trans. Device Mater. Reliab. 17, 267–277 (2017)

Kumar, P., Singh, S.: Optimization of the area efficiency and robustness of a QCA-based reversible full adder. J. Comput. Electron. 18, 1478–1489 (2019)

Abdoli, A.: Design flow of digital microfluidic biochips towards improving fault-tolerance, arXiv preprint arXiv:1912.08353, (2019)

Abdoli, A., Jahanian, A.: Fault-tolerant architecture and CAD algorithm for field-programmable pin-constrained digital microfluidic biochips, 2015 CSI Symposium on Real-Time and Embedded Systems and Technologies (RTEST), pp. 1-8. IEEE (2015)

Momenzadeh, M., Huang, J., Tahoori, M.B., Lombardi, F.: Characterization, test, and logic synthesis of and-or-inverter (AOI) gate design for QCA implementation. IEEE Trans. Comput. Aided Des. Integr. Circuits Syst. 24, 1881–1893 (2005)

Campos, C.A.T., Marciano, A.L., Neto, O.P.V., Torres, F.S.: A universal, scalable, and efficient clocking scheme for QCA. IEEE Trans. Comput. Aided Des. Integr. Circuits Syst. 35, 513–517 (2015)

Vankamamidi, V., Ottavi, M., Lombardi, F.: Two-dimensional schemes for clocking/timing of QCA circuits. IEEE Trans. Comput. Aided Des. Integr. Circuits Syst. 27, 34–44 (2007)

Torres, F.S., Silva, P.A., Fontes, G., Nacif, J.A., Ferreira, R.S., Neto, O.P.V., Chaves, J., Drechsler, R.: Exploration of the synchronization constraint in quantum-dot cellular automata, 2018 21st Euromicro Conference on Digital System Design (DSD), pp. 642-648. IEEE (2018)

Liu, W., Lu, L., O’Neill, M., Swartzlander, E.E.: A first step toward cost functions for quantum-dot cellular automata designs. IEEE Trans. Nanotechnol. 13, 476–487 (2014)

Lent, C.S., Tougaw, P.D.: A device architecture for computing with quantum dots, Proc. IEEE 85, 541-557 (1997)

Dysart, T.J.: Modeling of electrostatic QCA wires. IEEE Trans. Nanotechnol. 12, 553–560 (2013)

Wang, Y., Lieberman, M.: Thermodynamic behavior of molecular-scale quantum-dot cellular automata (QCA) wires and logic devices. IEEE Trans. Nanotechnol. 3, 368–376 (2004)

Danehdaran, F., Khosroshahy, M.B., Navi, K., Bagherzadeh, N.: Design and power analysis of new coplanar one-bit full-adder cell in quantum-dot cellular automata. J. Low Power Electron. 14, 38–48 (2018)

Abutaleb, M.: A novel QCA shuffle-exchange network architecture with multicast and broadcast communication capabilities. Microelectron. J. 93, 104640 (2019)

Bagherian khosroshahy, M., Sam Daliri, M., Abdoli, A., Navi, K., Bagherzade, N.: A 3D universal structure based on Molecular-QCA and CNT technologies. J. Mol. Struct. 1119, 86–95 (2016)

Shin, S.-H., Jeon, J.-C., Yoo, K.-Y.: Wire-crossing technique on quantum-dot cellular automata, NGCIT 2013, the 2nd international conference on next generation computer and information technology, pp. 52-57 (2013)

Momenzadeh, M., Ottavi, M., Lombardi, F.: Modeling QCA defects at molecular-level in combinational circuits, 20th IEEE International Symposium on Defect and Fault Tolerance in VLSI Systems (DFT’05), pp. 208-216. IEEE (2005)

Turvani, G., Riente, F., Cairo, F., Vacca, M., Garlando, U., Zamboni, M., Graziano, M.: Efficient and reliable fault analysis methodology for nanomagnetic circuits. Int. J. Circuit Theory Appl. 45, 660–680 (2017)

Srivastava, S., Sarkar, S., Bhanja, S.: Estimation of upper bound of power dissipation in QCA circuits. IEEE Trans. Nanotechnol. 8, 116–127 (2008)

Khosroshahy, M.B., Moaiyeri, M.H., Navi, K., Bagherzadeh, N.: An energy and cost efficient majority-based RAM cell in quantum-dot cellular automata. Results Phys. 7, 3543–3551 (2017)

Farazkish, R.: A new quantum-dot cellular automata fault-tolerant five-input majority gate. J. Nanopart. Res. 16, 2259 (2014)

Du, H., Lv, H., Zhang, Y., Peng, F., Xie, G.: Design and analysis of new fault-tolerant majority gate for quantum-dot cellular automata. J. Comput. Electron. 15, 1484–1497 (2016)

Goswami, M., Sen, B., Sikdar, B.K.: Design of low power 5-input majority voter in quantum-dot cellular automata with effective error resilience, 2016 Sixth International Symposium on Embedded Computing and Design, S.: (ISED), pp. 101-105. IEEE (2016)

Sun, M., Lv, H., Zhang, Y., Xie, G.: The fundamental primitives with fault-tolerance in quantum-dot cellular automata. J. Electron. Test. 34, 109–122 (2018)

Moghimizadeh, T., Mosleh, M.: A novel design of fault-tolerant RAM cell in quantum-dot cellular automata with physical verification. J. Supercomput. 75, 5688–5716 (2019)

Singh, G., Raj, B., Sarin, R.K.: Fault-tolerant design and analysis of QCA-based circuits. IET Circuits Devices Syst. 12, 638–644 (2018)

Khosroshahy, M.B., Moaiyeri, M.H., Navi, K.: Design and evaluation of a 5-input majority gate-based content-addressable memory cell in quantum-dot cellular automata, 2017 19th International Symposium on Computer Architecture and Digital Systems (CADS), pp. 1-6. IEEE (2017)

Bagherian Khosroshahy, M., Abdoli, A., Panahi, M.M.: Novel Feynman-based reversible and fault-tolerant nano-communication arithmetic architecture based on QCA technology. SN Comput. Sci. 2(6), 1–14 (2021)

Deng, F., Xie, G., Cheng, X., Zhang, Z., Zhang, Y.: CFE: a convenient, flexible, and efficient clocking scheme for quantum-dot cellular automata. IET Circuits Devices Syst. 14, 88–92 (2020)

Khosroshahy, M.B., Moaiyeri, M.H., Angizi, S., Bagherzadeh, N., Navi, K.: Quantum-dot cellular automata circuits with reduced external fixed inputs. Microprocess. Microsyst. 50, 154–163 (2017)

Azghadi, M.R., Kavehie, O., Navi, K.: A novel design for quantum-dot cellular automata cells and full adders, arXiv preprint arXiv:1204.2048 (2012)

Danehdaran, F., Angizi, S., Khosroshahy, M.B., Navi, K., Bagherzadeh, N.: A combined three and five inputs majority gate-based high performance coplanar full adder in quantum-dot cellular automata. Int. J. Inf. Technol. 1–13 (2019)

Walus, K., Dysart, T.J., Jullien, G.A., Budiman, R.A.: QCADesigner: A rapid design and simulation tool for quantum-dot cellular automata. IEEE Trans. Nanotechnol. 3, 26–31 (2004)

Ahmadpour, S.-S., Mosleh, M., Heikalabad, S.R.: An efficient fault-tolerant arithmetic logic unit using a novel fault-tolerant 5-input majority gate in quantum-dot cellular automata. Comput. Electr. Eng. 82, 106548 (2020)

Ahmadpour, S.S., Mosleh, M., Rasouli Heikalabad, S.: Robust QCA full-adders using an efficient fault-tolerant five-input majority gate. Int. J. Circuit Theory Appl. 47, 1037–1056 (2019)

Srivastava, S., Asthana, A., Bhanja, S., Sarkar, S.: QCAPro-an error-power estimation tool for QCA circuit design, 2011 IEEE international symposium of circuits and systems (ISCAS), pp. 2377-2380. IEEE (2011)

Author information

Authors and Affiliations

Contributions

All authors contributed equally to this manuscript.

Corresponding author

Ethics declarations

Conflicts of Interest/Competing Interests

There is no conflict of interest among authors.

Ethics approval

Not applicable.

Consent to Participate

All participants have provided consent to participate.

Consent for Publication

Consent for publication was obtained from all authors.

Additional information

Publisher’s Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Bagherian Khosroshahy, M., Abdoli, A. & Rahmani, A.M. Design and Power Analysis of an Ultra-high Speed Fault-tolerant Full-adder Cell in Quantum-dot Cellular Automata. Int J Theor Phys 61, 23 (2022). https://doi.org/10.1007/s10773-022-05013-0

Received:

Accepted:

Published:

DOI: https://doi.org/10.1007/s10773-022-05013-0