Abstract

This paper derives theoretical results for adaptive bias in Doherty amplifiers and presents the design and measurements of an integrated adaptive bias circuit tailored for high peak-to-average high bandwidth signals. Fundamental equations for output power, impedance, and efficiency of the complete Doherty amplifier are derived. Even with ideal transistor models, the Doherty amplifier is fundamentally nonlinear due to saturation of the main amplifier and class-C nonlinearity of the auxiliary. Increasing the transconductance of the auxiliary amplifier mitigates the distortion. Adaptive bias offers the possibility to control the output current characteristic of the auxiliary amplifier. This means that adaptive bias linearises and mitigates the need for an oversized auxiliary amplifier. Both methods, transconductance scaling and adaptive bias, are analysed and compared as well as having a band limited adaptive bias signal. The design of a multiple GHz bandwidth adaptive bias circuit is presented. To verify the circuit design and the theoretical predictions, an mmW Doherty amplifier in 22 nm CMOS-FD-SOI, utilizing the presented adaptive bias circuit, is measured and compared with and without adaptive bias. Comparison is conducted both using continuous-wave and modulated high bandwidth signals. Measured results confirm the predicted improvements by the adaptive bias as derived by the theoretical analysis.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

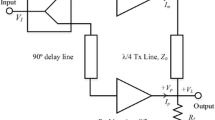

The Doherty amplifier, shown in Fig. 1, is the most well known efficient power amplifier (PA) and an absolutely brilliant construction. Even though it is close to 100 years since its invention, first publication, and patent in 1936 by Willliam H. Doherty [1, 2], it is still highly present in today’s wireless systems, and in the research for tomorrow’s. However, with the exception of two recently published papers [3] and [4], the published 5 G mmW transceivers during recent years all focus on class AB PAs to support the tough linearity requirements that follow transmissions of wideband, high peak to average (PAR), orthogonal frequency division multiplexing (OFDM) signals with high order modulations [5,6,7,8,9,10,11,12,13,14,15,16,17,18,19,20]. A growing interest for deploying adaptive bias, i.e. adjusting the bias of the power amplifier so that it follows the envelope of the modulated signal, is seen among mmW PA publications. Unfortunately, with the execption of [3], none of the PAs integrated in mmW frontends make use of the technique, but a few published standalone PAs do, and of these, some are class AB PAs [21,22,23] and some are Doherty amplifiers [24,25,26,27,28,29]. Gains brought by the adaptive bias are typically only evaluated for sinusoidal stimuli’s, and [25, 28, 29] which reports good results for modulated signals in combination with adaptive bias, do not provide any evaluation or comparison to estimate the performance with and without the adaptive bias.

Since the adaptive bias actively changes the operating point of the amplifying transistor(s) in the PA, it will affect both the linearity and the power consumption. Therefore, deploying adaptive bias on a PA operating on wideband modulated signals requires careful analysis. For instance, the adaptive bias signal must be fast enough to follow most of the envelope of the signal, and it should also provide an appropriate amount of bias increase as the input signal amplitude increases. Published amplifiers utilizing adaptive bias are typically lacking all information about bandwidth considerations/requirements. One work [28] however, does mention that the adaptive bias circuit has GHz bandwidth, but no more details or analysis are provided about how this is accomplished or what the trade-offs are.

The efficiency of the Doherty amplifier is boosted by using a class C amplifier together with a class AB, from now on referred to as the auxiliary and main amplifier. Traditionally, the conduction angle of the class C amplifier is determined by its static bias level and the input signal amplitude. Another possibility to control the conduction angle is to use adaptive bias, where the bias level depends on the input signal amplitude. This leads to some fundamental research questions. It is well known that adaptive bias can be used to linearise a single transistor stage, but what can be achieved when it comes to adaptive bias for Doherty amplifiers? Furthermore, can the Doherty amplifier benefit from adaptive bias even when using ideal linear transistor models?

To summarize, a growing interest for adaptive bias, and in particular in combination with Doherty amplifiers is observed. However, there is a lack of both an explaining theory for why and how the adaptive bias improves the Doherty amplifier, and of measurements comparing performance with and without adaptive bias. Theoretical analysis regarding the fundamental nonlinearities in a Doherty amplifiers, due to lack of output current from the class C biased auxiliary amplifier have previously been presented, for instance in [30, 31], which however do not link this built in imperfection of the Doherty amplifier to the mitigation opportunity offered by adaptive bias.

This paper has five main objectives. First, to explain through analytical derivation why a Doherty amplifier with ideal linear transistor models still produces a nonlinear output. Second, to investigate how adaptive bias can be used to linearise the system. Third, to quantify the effect of different adaptive bias non-idealities on the linearity of the Doherty amplifier. Fourth, present the design and verification of a integrated highly configurable adaptive bias circuit for an mmW Doherty PA amplifying high bandwidth high PAR OFDM signals. Fifth, to quantify benefits brought by deploying the adaptive bias on the auxiliary amplifier, by comparing the performance with that of having a static auxiliary amplifier bias, on a measured 5 G mmW PA that is integrated in a transceiver frond-end. In addition to the five main objectives, the paper also analyses the efficiency, load impedance, auxiliary amplifier conduction angle, and amplifier output currents, with and without adaptive bias.

The paper is organized as follows: A general circuit analysis of the Doherty amplifier is conducted in Sect. 2. How to select transconductance (\({\mathrm {g_m}}\)) ratio between main and auxiliary amplifier is derived in Sect. 3, and the deviation from ideal output current of the auxiliary amplifier is analysed in Sect. 4. A method to provide ideal conduction angle for the auxiliary amplifier is proposed in Sect. 5. In Sects. 6 and 7 the efficiency and distortion in a Doherty amplifier are analysed with ideal and non-ideal adaptive bias. A highly integrated 5 G mmW transceiver front-end, with a Doherty PA, and the design of the adaptive bias circuit capable of biasing the auxiliary amplifier either in a static class C or in adaptive bias mode is presented in Sect. 8. The measurement results of this are presented, analysed, and compared with the theory in Sect. 9. Finally, conclusions are drawn in Sect. 10.

2 Circuit analysis of Doherty amplifier

In the schematic of Fig. 2, the main amplifier is represented by a first current source and the auxiliary amplifier by a second current source, proportional to the first but phase shifted by 90-degrees, due to the delayed input signal of the auxiliary amplifier.

The main amplifier current is labelled \({\mathrm {I_1}}\), the auxiliary current \({\mathrm {I_2}}\), and \({\mathrm {I_3}}\) is the current that comes out from the \({\mathrm {\lambda /4}}\)-transmission line. The relation between the three currents are defined as

Now the goal is to express the impedances at the output of the main and auxiliary amplifiers as a function of d and the system load impedance \({\mathrm {R_{load}}}\). The impedance at the output of the transmission line \({\textrm{R}}\) is load modulated by \({\mathrm {I_2}}\), which gives.

Similarly, the impedance \({\mathrm {R_{aux}}}\) seen by \({\mathrm {I_{2}}}\) is load modulated by \({\mathrm {I_{3}}}\), which gives

The relation between impedance \({\mathrm {R_{main}}}\) and \({\textrm{R}}\) is given by the transmission line impedance transformation

And since we assume an ideal lossless transmission line, the power from \({\mathrm {I_1}}\) must be the same on both sides of the transmission line, which gives

Using (6) with (2), (3), and (4) gives the sought load impedances expressed in d and the system load impedance \({\mathrm {R_{load}}}\)

The main amplifier provides current at all signal levels, but the auxiliary amplifier only when the signal level is high. This can be captured by making the variable d, as used in the results above, a function of the input signal level \({\mathrm {d=f(v_{in})}}\), and set equal to zero below a threshold point, called back-off. For a symmetrical Doherty amplifier, the back-off level is located 6 dB below the maximum output power, below that point d is equal to zero, and above it d increases, and at maximum output power d is equal to 1. It is clear that the main amplifier should have a linear gain, but it is not as obvious what the gain should be for the auxiliary amplifier. Naturally, the target is to achieve a linear gain of the combined system up to saturated output power. For the symmetrical Doherty the main amplifier is designed to reach its maximum voltage amplitude at 6 dB back-off. Assuming a linear gain for the output current from the main amplifier, its power contribution will still continue to increase beyond this point as its load impedance is gradually reduced for output power levels above 6 dB back-off. However, the power delivered will no longer be linearly dependet on the input signal, instead the increase rate of the output power from the main amplifier will be lower and limited by the rate at which its load impedance is reduced. To achieve linear gain the power delivered by the auxiliary amplifier should exactly fill this gap, so that the combined output power becomes a linear amplification of the input signal. The target of the following calculations is to analytically derive how the ratio, labelled d in the analysis above, between the transconductance of the main and auxiliary amplifiers should then depend on the input signal level. For this case the transconductance is assumed to be the transconductance of the fundamental harmonic, \({\mathrm {h_{1}}}\). The output power from the main amplifier is then directly given by (10), assuming the voltage amplitude not being saturated.

Having \({\mathrm {d=0}}\) gives a linear output power

The output power from the auxiliary amplifier is

Combining (10) and (12) and using \({\mathrm {c=d/(Z_0/R_{load}-d)}}\) from (6)

For the case of a symmetrical Doherty, \({\mathrm {Z_{0}=2R_{load}}}\) and \({\mathrm {gm_{aux_{h1}}=d \cdot gm_{main_{h1}}}}\), which gives

Now using (6) but expressing d in c, gives

Which after some simplification becomes

After further simplifications it becomes

Which is equal to the linear output power \({\mathrm {P_{out}}}\) from (11). And since the output power is independent of d, the results proves that any ratio d between main and auxiliary will provide a linear Doherty. However, this is only true as long as the output of the main amplifier does not compress in voltage, and not any ratio guarantees that. The question then becomes, how should d gradually be increased to achieve a linear characteristic, combined with a hard maximum output voltage level of the main amplifier? For high efficiency, the voltage amplitude of the main amplifier should also be constant and close to the maximum for signal levels above back-off. This means that the load impedance of the main amplifier should be inversely proportional to the input voltage above back-off. Such a requirement could be expressed as

and again using (6) gives

For the symmetrical Doherty, where \({\mathrm {Z_{0}=2R_{load}}}\), \(\mathrm {{I_2}}\) becomes

As indicated by (22), after the auxiliary amplifier kicks in its output current \(\mathrm {{I_2}}\) should increase linearly with the input signal level, but with twice the slope of the main amplifier in a symmetric Doherty amplifier. This guarantees that the main amplifier output voltage stays constant at increased input signal levels.

3 Sizing of main and auxiliary amplifiers

In this section the transconductance \({\mathrm {g_m}}\) ratio of the main and auxiliary amplifiers is determined for ideal Doherty operation. To facilitate the discussion, Fig. 3 illustrates some key measures of the auxiliary amplifier and its signals, that is the gate-to-source voltage, drain current, threshold voltage \({\mathrm {V_{th}}}\), max drain current \({\mathrm {I_{max}}}\), conduction angle \({\mathrm {2\Phi }}\), overdrive voltage \({\mathrm {v_{od}}}\), and max input voltage \({\mathrm {v_{in}}}\).

In this paper, an ideal transistor model is used, and the reason for that is to separate effects originating from transistor imperfections from fundamental behaviour of the Doherty amplifier, shown also with ideal transistors. The ideal transistor model used is a voltage controlled current source with output current equal to \({\mathrm {v_{ov}g_m}}\), where the overdrive voltage \({\mathrm {v_{ov}=0}}\) for \({\mathrm {v_{in} \le V_{th}}}\) and \({\mathrm {v_{ov}=v_{in}-V_{th}}}\) for \({\mathrm {v_{in} > V_{th}}}\), as long as the drain voltage is below maximum voltage. When output current is large enough to produce voltage larger than the maximum voltage, the output current is reduced so that the drain voltage reaches the maximum voltage level. For an amplifier modelled like this, \({\mathrm {I_{max}}}\) is equal to the maximum overdrive voltage of the input signal multiplied by the transconductance \({\mathrm {g_{m}}}\). The bias level of the auxiliary amplifier is below the threshold voltage and controls when it starts to conduct current, which is set to occur at 6 dB back-off input signal amplitude, giving

At max input signal, the conduction angle in Fig. 3 is equal to \({\mathrm {2\pi /3}}\), and the auxiliary amplifier should then together with the main amplifier drive the load with full voltage swing, which will provide a value for the required transconductance \({\mathrm {g_{m}}}\) and in turn give the maximum drain current \({\mathrm {I_{max}}}\). Furthermore, at max output power, main and auxiliary amplifiers should contribute with equal amount of fundamental signal current to the load. The fundamental current as a function of the conduction angle and \({\mathrm {I_{max}}}\) is found in [32] and repeated in (24).

At maximum input signal both main and auxiliary amplifier should drive a signal current equal to \({\mathrm {V_{dd}/2R_{load}}}\), obtained from (4) and (3) with \({\mathrm {c=1}}\). This gives a closed expression for the required \({\mathrm {g_{m}}}\) by combining (23) with (24) and solving for \({\mathrm {g_{m}}}\).

For the class B biased main amplifier \({\mathrm {v_{od_{max}}=V_{in_{max}}}}\) and thus, with the conduction angle \({\mathrm {2\Phi =\pi }}\) it becomes

For the class C biased auxiliary amplifier \({\mathrm {v_{od_{max}}=V_{in_{max}}/2}}\) and thus, with the conduction angle \({\mathrm {2\Phi =2\pi /3}}\) it becomes

The ratio \({\mathrm {\gamma }}\) of transconductance for the main and the auxiliary amplifiers for conduction angle \({\mathrm {2\pi /3}}\) is calculated in (28) and plotted for various conduction angles in Fig. 4.

It should be noted that in a traditional Doherty amplifier with fixed bias, the maximum conduction angle cannot be set freely, but be determined by the back-off level. Setting the class C amplifier to turn on at a back-off level of 6 dB will result in a maximum conduction angle equal to \({\mathrm {2\pi /3}}\).

4 Auxiliary amplifier output current deviation from ideal performance

The conduction angle of the class C amplifier is zero below back-off and above back-off it is \({\mathrm { 2\Phi = 2 \cdot arccos(v_{in_{BO}}/v_{in})}}\). A linearly increasing output current with signal amplitude is required from the auxiliary amplifier for an overall linear system and optimal Doherty efficiency. The fundamental output current from the auxiliary amplifier is given by (29).

The first part of the expansion has the desired linear behaviour, with \({\mathrm {I_{aux}}}\) being proportional to overdrive voltage. However, the second part introduces non-linearity, due to the conduction angle being dependent on the overdrive voltage, see Fig. 5.

Studying Fig. 5 it becomes evident that a challenging part of the design of a Doherty amplifier is to control the output current from the auxiliary amplifier. Simply applying a bias level and an input signal that turns on the auxiliary amplifier at the back-off level will produce an output current that differs significantly from the wanted ideal case. Since the dashed curve is below the solid curve the main amplifier will go into voltage compression and the output power delivered by both the main and auxiliary amplifiers will be reduced. Naturally this results in nonlinear distortion since the output signal will deviate from linear amplification. If we for some reason would have a region where the dashed curve would be above the solid curve, for instance if we choose to adjust the bias so that the input signal turns on the auxiliary amplifier at a lower input signal level, i.e. before the main amplifier goes into compression, the load modulation would instead lower the impedance at the output of the main amplifier too much, resulting in reduced efficiency. That case would, however, still produce a linear output, since the reduction of the output power delivered from the main amplifier would be filled up exactly by the increase in power from the auxiliary amplifier, as derived in (16).

5 Adaptive bias

A method to produce the ideal conduction angle and overdrive voltage for \({\mathrm {I_2}}\) to satisfy (22), is to apply a signal dependent bias level, typically called adaptive bias. In Fig. 5 the difference between ideal \({\mathrm {I_2}}\) and the \({\mathrm {I_2}}\) obtained directly from the class C biased auxiliary amplifier does not seem that large. In a sense, this is true, and the deviation, as will be shown later, is of minor concern for this case. However, this is for an auxiliary/main ratio of \({\mathrm {\gamma =2.56}}\), which can be considered high. For implementation purposes, at least for high frequency applications, such a large scaling ratio is limiting and troublesome. Parasitic capacitances are increased, chip area increases, bandwidth is reduced, and efficiency drops due to increased losses, and so on. Some of these drawbacks could perhaps be acceptable if the increased size would result in an increased output power. Unfortunately, however, the auxiliary amplifier only delivers the same amount of output power as the 2.56 times smaller main amplifier. Using a reduced scaling ratio \({\mathrm {\gamma }}\) with fixed auxiliary bias, the bias level must be increased and thereby the auxiliary amplifier turns on earlier, which limits the efficiency boost and the whole reason for using a Doherty amplifier. Also for this problem, the adaptive bias offers a solution. It is then possible to freely choose the back-off level with a smaller \({\mathrm {\gamma }}\), but still delivering the \({\mathrm {I_2}}\) current needed for linear output power. To investigate the effect of the adaptive bias, the equations for impedance levels and output powers were modified taking a dynamic bias level into account, changing both \({\mathrm {I_{max}}}\) and the conduction angle. Using the equations in Sect. 2 combined with the the possibility to freely choose the overdrive voltage for the auxiliary amplifier via the use of adaptive bias, plots for output currents, powers, and voltages using size ratio \({\mathrm {\gamma =2.56}}\) and \({\mathrm {\gamma =1}}\) with and without ideal adaptive bias, are shown in Fig. 6 below. As can be seen, solid curves, for ideal adaptive bias, give ideal Doherty amplifier behaviour, regardless of size ratio. Without adaptive bias, it is clear that using a large sized auxiliary amplifier \({\mathrm {\gamma =2.56}}\) compared to \({\mathrm {\gamma =1}}\) mitigates the deviation from ideal Doherty behaviour. For instance, the saturated power for \({\mathrm {\gamma =1}}\) is reduced by more than 3 dB, but for \({\mathrm {\gamma =2.56}}\) the saturated output power is equal to the ideal Doherty case. However, this disregards all practical difficulties with having an oversized auxiliary amplifier.

Dashed curves: no adaptive bias. Solid curves: ideal adaptive bias. Upper Left: Currents \({\mathrm {I_1}}\) and \({\mathrm {I_2}}\) for \({\mathrm {\gamma =2.56}}\) and \({\mathrm {\gamma =1}}\). Upper Right: Output powers for \({\mathrm {\gamma =2.56}}\). Output powers. Lower Left: Output powers for \({\mathrm {\gamma =1}}\). Lower Right: Voltage levels for \({\mathrm {\gamma =2.56}}\) and \({\mathrm {\gamma =1}}\)

6 Efficiency of Doherty amplifier

Ignoring losses in the output combination network, the efficiency of a Doherty amplifier only depends on the efficiency of the main and auxiliary amplifiers. For output powers below back-off, the auxiliary amplifier is turned off and the efficiency is simply determined by the main amplifier, which here is assumed to be biased in class B. For output power above back-off, the main amplifier is load modulated by the auxiliary so that it has constant and maximum output voltage swing, which means that it operates at maximum class B efficiency of \({\mathrm {\pi /4=78.5\%}}\). The auxiliary amplifier is biased in class C and its efficiency is determined by its conduction angle [32]. For conduction angle \({\mathrm {2\pi /3}}\) and with full output voltage swing the efficiency of the auxiliary amplifier becomes \({\mathrm {89.7\%}}\). When backing down the output signal from the auxiliary PA its efficiency will scale linearly with the ratio of the output voltage and the supply voltage as expressed in (30).

For a linear Doherty amplifier the output voltage is proportional to the input voltage, see Fig. 6 lower right. Even so, the conduction angle at back-off is not straight forward, since the adaptive bias was used to adjust the conduction angle for linear output. It is therefore necessary to find the conduction angle of the auxiliary amplifier, for ideal Doherty performance, in the region between back-off and maximum output power. The power consumption is obtained from [32], combined with (23) for \({\mathrm {I_{max}}}\)

And the power in the fundamental harmonic is acquired from (24), combined with the load impedance of the auxiliary amplifier, and again (23) for \({\mathrm {I_{max}}}\).

Which would indicate that the auxiliary output power is a 2-dimensional function depending on both conduction angle and input voltage. By introducing the adaptive bias we can control the conduction angle. However, for any output power that the auxiliary amplifier produces at a given input voltage, only one conduction angle exists, or the other way around. The adaptive bias will alter both conduction angle and overdrive voltage at the same time, not independently. Figure 7 shows the efficiency of the Doherty amplifier for auxiliary/main size ratios \({\mathrm {\gamma =2.56}}\) and \({\mathrm {\gamma =1}}\) with and without adaptive bias.

7 Distortion in Doherty amplifier

7.1 Amplitude distortion for single tone input signal

Without the use of adaptive bias to produce the desired \({\mathrm {I_2}}\) current from the auxiliary amplifier, the Doherty amplifier will, even with ideal transistor models, deviate from linear amplification. On a theoretical level the distortion can be largely mitigated by the method of increasing the size of the auxiliary amplifier versus the main amplifier. Since the analysis carried out in this paper uses ideal transistor models, no phase distortion will be generated and only amplitude-to-amplitude (AM-AM) distortion is considered. Figure 8 shows AM-AM, which is directly derived from the output power of Fig. 6 upper right and lower left, for two different \({\mathrm {\gamma }}\)-ratios with and without ideal adaptive bias.

As expected, the use of ideal adaptive bias provides a linear output. It is also evident that a large size ratio reduces the AM-AM, keeping compression below 0.6 dB, for \({\mathrm {\gamma =2.56}}\), whereas for equal size main and auxiliary (\({\mathrm {\gamma =1}}\)) the compression exceeds 3 dB.

7.2 Ideal adaptive bias signal for modulated inputs

The source of the adaptive bias signal is the envelope of the modulated signal, which is equal to \({\mathrm {\sqrt{(I^2+Q^2)}}}\), where I and Q are the two base-band signals representing the real and imaginary part of the complex modulated signal. Each of the I and Q signals has a bandwidth that is half of the instantaneous bandwidth at the carrier frequency (RF-IBW). The envelope has bandwidth expansion due to the nonlinear function from IQ-data to envelope. In addition to this, the adaptive bias signal is a nonlinear function of the envelope, which is shown for the two cases \({\mathrm {\gamma =2.56}}\) and \({\mathrm {\gamma =1}}\) in Fig. 9.

To provide a time domain example of an adaptive bias signal, used to linearise equal sized main and auxiliary amplifiers, i.e. \({\mathrm {\gamma =1}}\), a short segment of the envelope and corresponding adaptive bias signal for a 7.5 dB peak-to-average (PAR) OFDM signal is depicted in Fig. 10.

As can be seen some sharp, i.e. high frequency, corners are present in the adaptive bias signal, and a fast Fourier transform (FFT) was used to investigate the frequency content of the adaptive bias signal, see Fig. 11.

As can be seen energy spreads over wider bandwidth than occupied by the original I-Q signal, but most energy is still below the RF-IBW of the output signal.

7.3 Amplitude distortion with modulated non-ideal adaptive bias

Without adaptive bias the Doherty amplifier suffers from amplitude distortion due to the non-ideal output current \({\mathrm {I_2}}\) from the auxiliary amplifier, leading to compression in the main amplifier regardless of size ratio \({\mathrm {\gamma }}\). But the problem is much more prominent for low size ratios, which could already be seen in Fig. 8 for single-tone AM-AM distortion. A measure for total compressive distortion (TCD), being very similar, but not identical, to error vector magnitude (EVM), is defined in (33) to evaluate the impact the compressive behaviour has on a modulated signal.

where \({\mathrm {G_{lin}}}\) is the linear non compressive gain, i.e. the small signal gain. TCD should be interpreted as the (compressive) power of the deviation from the wanted linear signal, normalized to the power of the wanted linear signal. Differences between TCD and EVM is that EVM is only calculated at the symbol points, and with a linear gain adjustment that minimizes EVM. EVM is also limited to inband distortion, whereas TCD also takes out of band distortion into account. In this context where we want to estimate how much imperfections a PA adds to a signal, the TCD is thus better suited. Figure 12 shows how TCD depends on the size ratio \({\mathrm {\gamma }}\) without any adaptive bias. The expected result with a more linear output signal for higher \({\mathrm {\gamma }}\) is obtained. In addition, as the PA compresses more at large input signals, the average output power (\({\mathrm {P_{avg}}}\)) also decreases as \({\mathrm {\gamma }}\) is reduced. However, since the high peaks in the OFDM signal occur quite rarely the effect on the average output power is rather limited.

Adding adaptive bias can mitigate the amplitude distortion, but the effect will depend on bandwidth limitations. At the very least, it will suffer from a \({\mathrm {1^{st}-order}}\) low-pass filtering by the output impedance of the adaptive bias generation circuit and the capacitive load it must drive. A popular technique to reduce the input capacitance and improve the reverse isolation, at the carrier frequency, of a differential amplifier, is to use neutralizing capacitors to cancel out \({\mathrm {C_{gd}}}\) of the common source (CS) transistors, as depicted in Fig. 13.

For common mode signals, however, like the adaptive bias, the input capacitance is increased by the neutralizing capacitors rather than decreased. Ignoring all capacitors, except for \({\mathrm {C_{gs}}}\) and \({\mathrm {C_{gd}}}\), the common mode input capacitance can be expressed as

\({\mathrm {G_{BB}}}\) is the gain at base-band frequencies, here estimated to \({\mathrm {G_{BB}\approx -g_{m_{CS}}/g_{m_{CG}}=-1}}\). This gives an input capacitance of \({\mathrm {C_{input_{CM}}=2C_{gs}+8C_{gd}}}\), which results in a rather large capacitive load for the adaptive bias circuit. A low bandwidth adaptive bias signal will make the Doherty amplifier deviate from linear amplification and thereby create distortion. To assess the severity of the problem, an ideal adaptive bias signal for linear amplification of a high PAPR modulated signal, for various \({\mathrm {\gamma -ratios}}\), was filtered through \({\mathrm {1^{st}-order}}\) low-pass filters with different bandwidths. Figure 14 shows the time domain adaptive bias signal from lower Fig. 10 compared to its filtered version.

This is a rather realistic filter scenario considering that an adaptive bias circuit will have an output impedance driving a capacitive load. The actual bandwidth (BW) of the low pass filter depends on design parameters like amount of current spent in the adaptive bias generation circuit and the size and design of the PA affecting the capacitive load. Incorrect bias for the auxiliary amplifier, which is the outcome of non-ideal adaptive bias, can result in two things. Firstly, when the adaptive bias level is lower than it should be, the Doherty output power compresses. Secondly, when the adaptive bias level is higher than it should be, it load modulates the main amplifier more than necessary causing loss in efficiency. Figure 15 shows how TCD increases with reduced low-pass filter cut-off frequency.

8 Adaptive bias test circuit

8.1 Adaptive bias test circuit system architecture

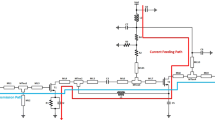

To validate the theory, a Doherty amplifier integrated in a 5 G mmW transceiver circuit in a 22 nm FD-SOI CMOS process was designed, fabricated, and measured. The details about the circuit, measurement setup, and measurement results can be found in [3]. For convenience, the circuit architecture, die photo, and PCB photo are reproduced here, see Fig. 16. The transmitter uses two IQ-mixers for frequency upconversion and generation of the required 90-degree phase shift between the input signals to the main and auxiliary amplifiers. To boost the gain, both input signals are then amplified by pre-power amplifiers (PPAs). A current combined Doherty PA, consisting of a main and auxiliary amplifier and an output combining network, drives a 50 \(\Omega\) load via a balun, which provides impedance transformation and differential to single ended signal conversion. A transmit receive switch (TRX-switch) is also included in the architecture.

8.2 Adaptive bias test circuit design

The Doherty amplifier has identical size (\(g_m\)) of the main and auxiliary amplifiers, i.e. \(\gamma =1\), and a highly programmable adaptive bias circuit is designed and connected to the gate of the CS transistor of the auxiliary amplifier. The adaptive bias circuit is designed to fulfill the four requirements needed to effectively linearise the Doherty amplifier as stated in [3]. These four requirements are, (1) control of the DC level, i.e. the small-signal operating point of the input transistors, (2) effective control of the starting point for the bias level increase w.r.t. the input signal level, (3) control the increase rate after the starting point, and (4) ability to drive the output load, in this case the common mode input impedance of the CS-stage of the auxiliary amplifier, such that the bias signal tracks the envelope of the signal with little phase lag and amplitude variation over the bandwidth of the signal envelope.

Figure 17 shows a detailed schematic of the adaptive bias circuit designed. The target is to independently control the parameters according to requirements (1)–(3) above while still supporting the bandwidth requirement. A digitally controlled current source \(I_0\), combined with either a current mirror or a 1 k \(\Omega\) resistor produces a DC level used to set the small-signal operating point of the differential input transistors of the auxiliary PA. To operate the adaptive bias in constant GM mode for linearisation of an amplifier biased in class A, AB, or B the current mirror is selected and for class C mode operation, which is the case for the auxiliary amplifier of a Doherty PA, the 1 k \(\Omega\) resistor is selected. Since the small-signal operation point, suitable for class C mode operation, should be well below \(V_{th}\) an additional 20 \(\upmu \hbox {A}\) combined with a 10 k \(\Omega\) resistor produces a voltage off-setted by 200 mV for a voltage level suitable to use as input to an operational amplifier (OP-amp).

Two PMOS transistors with combined output signal implements a rectifying pair and produces a current \(I_{rect}\) that depends on the RF signal amplitude. Controlling the gate bias level of the rectifying pair controls at what RF amplitude \(I_{rect}\) will start to increase i.e. the turn on point of the adaptive bias. Current \(I_{rect}\) is then transformed into a voltage through a tunable resistor \(R_{1}\), which is used to control the slope of the increase of the adaptive bias voltage after the turn on. A straightforward method to combine the small-signal DC level with the amplitude dependent part of the adaptive bias signal that is produced by the rectifying pair is proposed in [21] which also is from the same first and last author. However, when adjusting the large signal settings, i.e. the turn on point and slope settings, an undesired effect is that the small-signal DC level changes, which makes it more difficult to find optimum settings for a particular use case and/or power amplifier design. Settings for the adaptive bias, i.e. the small and large signal settings, must be adjusted for optimal performance for each sample, and also when changes in operating frequency or temperature occur.

8.3 Orthogonalizing large and small signal settings

The unwanted impact on the DC-level is due to that when changing the settings for turn on point and slope it has an affect on the DC-voltage output from the rectifying pair, even for zero or low RF signal amplitudes. Ideally the DC-level should be unaffected by the large signal settings. In [21] changing the large signal adaptive bias setting results in about 75 mV of small-signal DC level changes. However, these changes were at a bias level above the threshold voltage. In the proposed design the aim is to have a small signal DC-level quite far below the threshold voltage to properly turn-off the class C biased auxiliary amplifier, which with a similar design as in [21] would result in a relatively larger DC-level change when the output current from the rectifying pair changes or resistor \(R_1\) is changed.

To orthogonalize the large and small signal settings the small signal DC-level is controlled by a low frequency negative feedback loop, which regulates the output voltage of a common drain (CD) stage (node \(DC_{out-replica}\)), identical to the CD stage driving the output load, but downscaled in size and driven by an identical replica of the rectifying pair, to the same voltage as the desired DC-level (node \(PA_{DC-ref}\)). The replica has no RF input signal and therefore it captures the undesired effects that the large signal settings would have on the small-signal DC level. An OP-amp controls a transistor with output current \(I_{dc-ctrl}\), that compensates for the undesired DC-level changes. A copy of the \(I_{dc-ctrl}\) current is then fed to the rectifying pair which has the RF-input signal connected to it and is used to drive the CS input transistors of the auxiliary amplifier. As long as the rectifying pair is well matched to its replica the proposed method is expected to largely suppress output DC-level variations when adjusting the large signal settings.

To guarantee stability of the DC-level negative feedback loop, a rather large capacitor (0.85 pF) is added, realizing a capacitive narrowbanding compensation. Another problem that arises is that when a large RF signal is present, a quite large 2nd-harmonic is present in nx1 and the turn on control nodes, and to avoid that it leaks back and affects the output signal from the DC-replica, two low pass filters (LPF) are added. One LPF is added between the output signal of the OP-amp and the current source transistor, which produces \(I_{dc-ctrl}\) in the rectifying pair, and one LPF is added between the rectifying pair and the resistive ladder (indicated as an controllable voltage source in Fig. 17) producing the voltage reference for the turn on control of the rectifying pair.

8.4 Adaptive bias high bandwidth design considerations

For effective linearisation, the adaptive bias signal must be able to follow the envelope of the modulated signal and must drive the common mode input capacitance which is estimated in (34). The auxiliary amplifier used here has a simulated common mode input capacitance of \(1.4-1.8\,\)pF including parasitic capacitances, depending on the bias level.

The rectifying pair drives a resistively loaded common drain (CD) buffer, wide enough to provide a low output impedance, to be capable of driving the common mode input capacitance with a sufficiently large bandwidth. Since the circuit does not offer any possibility to measure a high bandwidth adaptive bias signal, the performance is verified by simulations of the adaptive bias circuit and measurements on the quality of the modulated PA output signal. A two tone simulation, which gives an envelope with the beat frequency of the two RF input tones, that the adaptive bias should follow, was conducted with varying tone separation. Compared to the OFDM-signal the envelope of the two tone simulation is rather extreme, since all the energy is located at the edges of the band, whereas for the OFDM-signal the energy is evenly distributed over the bandwidth. At 1.6 GHz tone separation the magnitude of the adaptive bias signal has dropped by < 1.3 dB and the phase lags by 41 degrees, compared to the magnitude and phase of the adaptive bias signal for a low tone separation frequency.

However, a perhaps more illustrative result of how well the adaptive bias follows the envelope of high bandwidth modulated signals is shown in Fig. 18, which compares post layout simulation results of the adaptive bias circuit output signal with the theoretically derived ideal adaptive bias signal, using the envelope of an OFDM signal of 0.4–3.2 GHz modulation BW, when driving the auxiliary PA. The ideal adaptive bias signal is derived using \(\gamma =1\) and is identical to the results shown in Figs. 9 and 10. As can be seen in Fig. 18, for large signal levels and low bandwidths the simulated adaptive bias signal tracks the desired theoretical adaptive bias signal closely. For low signal levels, i.e. for envelopes below 0.5 V, where the adaptive bias signal ideally is zero there is a larger deviation. This, however, is not a a severe issue and is not expected to cause any linearity degradation. Normalizing the time axis makes it possible to visualize how the amplitude and phase depend on the bandwidth, and as can be seen, even for a very high bandwidth (3.2 GHz) only minor deviations occur.

8.5 Adaptive bias power consumption

The absolute majority of the power consumption of the adaptive bias circuit comes from the CD buffer driving the auxiliary PA, and to reduce its power consumption it is supplied by 0.8 V, while the other parts of the adaptive bias circuit are supplied by 1 V. When the adaptive bias circuit is operating with a high PAR signal at full input power, the CD buffer power consumption will be set by the average voltage level of the CS input stage (\(<\,200\,\hbox {mV}\)), which can be seen in Fig. 18, and the 50 \(\Omega\) resistor. In average the complete power consumption becomes about 4 mW of the adaptive bias circuit.

9 Measurement results

The test circuit was measured in detail in [3] and optimal adaptive bias settings were identified. Identical settings were used for both continuous wave (CW) and modulated signal measurements. In this section, the theoretical results, as presented in this paper, derived using a simplified ideal transistor model suitable for hand calculations, is compared with measurement results from two different samples. The test circuit does not offer any possibility to measure the output current, output power, or power consumption of the individual main and auxiliary amplifiers, instead the combined output power and power consumption of the Doherty amplifier were analysed.

9.1 CW-tone measurements

Figure 19 shows measured output power, AM-AM, and adaptive CS gate bias voltage to the auxiliary amplifier, when stimulated with a CW tone of increasing input power, for two different samples. The measurement was repeated with a static auxiliary class C bias, i.e. turned off adaptive bias. The theoretical predictions from Figs. 6, 8, and 9 for \(\gamma =1\) are then normalised to the same output power level and plotted in the same figure, both with and without adaptive bias. Considering that the theoretical models use highly simplified frequency agnostic transistor models with zero output current below \(V_{th}\) and an output current \(I_{out}\) equal to \(g_m(V_{gs}-V_{th})\) as long as \(I_{out}R_{Load}<V_{dd}\), the predictions show good agreement with the presented measurement results at 26.5 GHz, both for the output power, see Fig. 19 Upper, and for AM-AM, see Fig. 19 Middle. The test circuit is equipped with a low frequency output to measure the adaptive CS gate bias voltage to the auxiliary amplifier when the PA is operating with constant envelope signals, and this measured output voltage from the adaptive bias circuit is shown in Fig. 19 Lower.

To validate that the negative feedback loop effectively controls the small-signal bias level such that the bias level does not change too much when changing the large signal settings (turn-on point and slope), the measured small signal bias level is plotted in Fig. 20. The result shows a variation of about 26 mV when changing the two registers, which is about one third of the reported small-signal bias level variation in [21].

Figure 21 illustrates orthogonality of the two large signal controls, slope and turn-on point. When changing the turn-on point the slope should ideally be unaffected, and vice versa. The turn-on point is defined as when the adaptive bias level has increased by 5 mV, and the slope is defined as the slope of the adaptive bias signal at the point in the middle (on a logarithmic scale) between the turn-on point and the maximum input signal. For completely orthogonal control, the measurements should result in straight vertical lines.

9.2 Modulated signal measurements

Modulated measurements were performed to validate the high frequency performance of the adaptive bias circuit. Figure 22 shows measured results of the key parameters EVM, PA drain efficiency (DE), and adjacent channel leakage ratio (ACLR) for 12 dBm average output power for sample 1 and 10 dBm average output power for sample 2 with 1600 MHz modulation BW, with and without adaptive bias, i.e. with static class C bias.

Sample 1 (left column) and sample 2 (right column), measured performance at PA output with modulated 5 G NR 16QAM-OFDM signals for 1600 MHz BW using optimized adaptive bias signal for the auxiliary amplifier (upper row) and compared with static class C bias for the auxiliary amplifier (lower row). Pilot symbols are shown for sample 1 in cyan and purple color. Average value for the modulated signal EVM, PA DE, ACLR, and output power are stated in the figure

Figure 23 compares measurement results for signals with different modulation bandwidth of 100 MHz, 200 MHz, 400 MHz, 800 MHz, 1600 MHz. As can be seen, both inband and out of band linearity (EVM and ACLR) are significantly improved (about 2 dB) by the adaptive bias, at a very small expense of efficiency (about 0.3 \(\%\)-units) for all bandwidths, which is in line with the predictions of the simulated performance of the adaptive bias generation circuit in [3].

To investigate the amplitude dependency of the performance improvement that the adaptive bias brings, a 400 MHz modulated 16-QAM signal was measured, in Fig. 24 both for sample 1 and sample 2, at different output power levels. The results clearly show that for low output power levels the adaptive bias does not affect the results, but as the peaks of the high PAR input signal starts to exceed the B.O. level, the adaptive bias starts to linearise the output signal.

Figure 25 shows PA DE vs transmitter EVM for different signal BW using adaptive bias, and compares this to a static bias with different levels for a fixed BW (400 MHz) signal, in both cases with OFDM modulation. As expected, the static bias increase improves EVM at the expense of PA DE, whereas the adaptive bias improves EVM without reducing PA DE as the signal BW is reduced.

10 Conclusion

Analytical derivations show that for ideal Doherty operation the fundamental frequency output current from the auxiliary amplifier must increase linearly for input amplitudes above the back-off level. Even with ideal transistor models, the Doherty amplifier will therefore produce a nonlinear output signal or a reduced efficiency, due to the nonlinear increase of the output current from the auxiliary amplifier. Two mitigation techniques are identified. First, increase the transconductance, i.e. \({\mathrm {g_m}}\), of the auxiliary amplifier compared to the main amplifier. Second, control the auxiliary amplifier by dynamically adjusting the bias level so that the desired output current level is achieved. Ideally, this makes it possible to adjust the back-off level, produce a linear auxiliary output current, and avoid to increase the size of the auxiliary amplifier. The adaptive bias signal, however, suffers from bandwidth expansion both due to its origin from the envelope signal and the nonlinear function that produces it from the envelope. Therefore, generating the adaptive bias signal can be challenging. Analytical calculations in combination with simulated bias signals, reveal that even with rather non-ideal adaptive bias signals, however, significant improvements in AM-AM, saturated output power, and efficiency, can be achieved. For instance, an ideal adaptive bias signal filtered through a 1st-order low pass filter with a cut-off frequency that is just \({\mathrm {25\%}}\) of the modulated RF signal bandwidth, suppresses amplitude distortion by more than 6 dB of a 7.5 dB PAR OFDM modulated signal. Similar linearity improvement can be achieved by doubling the size, i.e. \({\mathrm {g_m}}\), of the auxiliary amplifier. The design of a highly configurable adaptive bias circuit is presented and analysed in detail, for CW-tone as well as for modulated signals. Simulations show that it is possible to generate an adaptive bias signal that quite closely tracks an ideal theoretically calculated adaptive bias signal consuming as little as 4 mW power. Measurements also confirm that design strategies for orthogonalizing the control settings for small-signal bias level, turn-on point, and slope for the adaptive bias where successful. CW-tone and modulated signal measurements on two samples of a Doherty PA with equally sized main and auxuiliary amplifiers confirm the presented theory. The adaptive bias increases the 1 dB compression point by > 3dB. EVM and ACLR are improved by about 2 dB at a very small expense in efficiency. Signal measurements with different BW confirm that the integrated adaptive bias generating circuit can successfully track the envelope of the signal, improving the linearity of the output signal, at a very low efficiency degradation. Finally, the impact of a static bias increase of the class C biased auxiliary amplifier is measured and compared with the gains brought by the adaptive bias for different bandwidths.

Data availability

No datasets were generated or analysed during the current study.

References

Doherty, W. H. (1936). A new high efficiency power amplifier for modulated waves. Proceedings of the Institute of Radio Engineers, 24(9), 1163–1182. https://doi.org/10.1109/JRPROC.1936.228468

Doherty, W.H. (1936). Amplifier. US Patent 2210028A.

Elgaard, C., Özen, M., Westesson, E., Mahmoud, A., Torres, F., Reyaz, S. B., Forsberg, T., Akbar, R., Hagberg, H., & Sjöland, H. (2024). Efficient wideband mmW transceiver front end for 5G base stations in 22-nm FD-SOI CMOS. IEEE Journal Solid-State Circuits, 59(2), 321–336. https://doi.org/10.1109/JSSC.2023.3282696

Jung, J., Lee, J., Kang, D., Kim, J., Lee, W., Oh, H., Park, J.-H., Kim, K., Lee, D.-H., Lee, S., Lee, J.H., Kim, J.H., Kim, Y., Kim, T., Park, S., Park, S., Baek, S., Suh, B., Oh, S., Lee, D., Son, J., & Yang, S.-G. (2023). A 39 GHz 2\(\times\)16-Channel Phased-Array Transceiver IC With Compact, High-Efficiency Doherty Power Amplifiers. In IEEE Radio Frequency Integrated Circuits Symposium (RFIC) (pp. 273–276). https://doi.org/10.1109/RFIC54547.2023.10186130

Shakib, S., Elkholy, M., Dunworth, J., Aparin, V., & Entesari, K. (2019). A wideband 28-GHz transmit-receive front-end for 5G handset phased arrays in 40-nm CMOS. IEEE Transactions on Microwave Theory and Techniques, 67(7), 2946–2963. https://doi.org/10.1109/TMTT.2019.2913645

Mondal, S., Singh, R., & Paramesh, J. (2019). 21.3 A Reconfigurable Bidirectional 28/37/39GHz Front-End Supporting MIMO-TDD, Carrier Aggregation TDD and FDD/Full-Duplex with Self-Interference Cancellation in Digital and Fully Connected Hybrid Beamformers. In IEEE International Solid-State Circuits Conference (ISSCC) (pp. 348–350). https://doi.org/10.1109/ISSCC.2019.8662468

Park, J., Lee, S., Lee, D., & Hong, S. (2019). A 28GHz 20.3%-Transmitter-Efficiency 1.5\(^\circ\)-Phase-Error Beamforming Front-End IC with Embedded Switches and Dual-Vector Variable-Gain Phase Shifters. In IEEE International Solid-State Circuits Conference (ISSCC) (pp 176–178). https://doi.org/10.1109/ISSCC.2019.8662512

Gao, L., & Rebeiz, G. M. (2020). A 22–44-GHz phased-array receive beamformer in 45-nm CMOS SOI for 5G applications with 3–3.6-dB NF. IEEE Transactions on Microwave Theory and Techniques, 68(11), 4765–4774. https://doi.org/10.1109/TMTT.2020.3004820

Pang, J., Li, Z., Kubozoe, R., Luo, X., Wu, R., Wang, Y., You, D., Fadila, A. A., Saengchan, R., Nakamura, T., Alvin, J., Matsumoto, D., Liu, B., Narayanan, A. T., Qiu, J., Liu, H., Sun, Z., Huang, H., Tokgoz, K. K., … Okada, K. (2020). A 28-GHz CMOS phased-array beamformer utilizing neutralized bi-directional technique supporting dual-polarized MIMO for 5G NR. IEEE Journal of Solid-State Circuits, 55(9), 2371–2386. https://doi.org/10.1109/JSSC.2020.2995039

Tang, X., Liu, Y., Mangraviti, G., Zong, Z., Khalaf, K., Zhang, Y., Wu, W.-M., Chen, S.-H., Debaillie, B., & Wambacq, P. (2021). Design and analysis of a 28 GHz T/R front-end module in 22-nm FD-SOI CMOS technology. IEEE Transactions on Microwave Theory and Technique, 69(6), 2841–2853. https://doi.org/10.1109/TMTT.2021.3059891

Pang, J., Li, Z., Luo, X., Alvin, J., Saengchan, R., Fadila, A. A., Yanagisawa, K., Zhang, Y., Chen, Z., Huang, Z., Gu, X., Wu, R., Wang, Y., You, D., Liu, B., Sun, Z., Zhang, Y., Huang, H., Oshima, N., … Okada, K. (2021). A CMOS dual-polarized phased-array beamformer utilizing cross-polarization leakage cancellation for 5G MIMO systems. IEEE Journal of Solid-State Circuits, 56(4), 1310–1326. https://doi.org/10.1109/JSSC.2020.3045258

Yin, Y., Ustundag, B., Kibaroglu, K., Sayginer, M., & Rebeiz, G. M. (2021). Wideband 23.5–29.5-GHz phased arrays for multistandard 5G applications and carrier aggregation. IEEE Transactions on Microwave Theory and Techniques, 69(1), 235–247. https://doi.org/10.1109/TMTT.2020.3024217

Zhu, W., Wang, J., Zhang, X., Lv, W., Liao, B., Zhu, Y., & Wang, Y. (2021). A 24-28-GHz four-element phased-array transceiver front end with 21.1%/16.6% Transmitter Peak/OP1dB PAE and subdegree phase resolution supporting 2.4 Gb/s in 256-QAM for 5-G communications. IEEE Transactions on Microwave Theory and Techniques, 69(6), 2854–2869. https://doi.org/10.1109/TMTT.2021.3071600

Yi, Y., Zhao, D., Zhang, J., Gu, P., Chai, Y., & Liu, H. (2022). A 24-29.5-GHz highly linear phased-array transceiver front-end in 65-nm CMOS supporting 800-MHz 64-QAM and 400-MHz 256-QAM for 5G new radio. IEEE Journal of Solid-State Circuits, 57(9), 2702–2718. https://doi.org/10.1109/JSSC.2022.3169588

Sadhu, B., Paidimarri, A., Lee, W., Yeck, M., Ozdag, C., Tojo, Y., Plouchart, J.-O., Gu, X., Uemichi, Y., Chakraborty, S., Yamaguchi, Y., Guan, N., & Valdes-Garcia, A. (2022). A 24-to-30GHz 256-Element Dual-Polarized 5G Phased Array with Fast Beam-Switching Support for \(>\)30,000 Beams. In IEEE International Solid-State Circuits Conference (ISSCC) (vol. 65, pp. 436–438). https://doi.org/10.1109/ISSCC42614.2022.9731778

Sadhu, B., Tousi, Y., Hallin, J., Sahl, S., Reynolds, S., Renström, O., Sjögren, K., Haapalahti, O., Mazor, N., Bokinge, B., Weibull, G., Bengtsson, H., Carlinger, A., Westesson, E., Thillberg, J.-E., Rexberg, L., Yeck, M., Gu, X., Friedman, D., & Valdes-Garcia, A. (2017). 7.2 A 28GHz 32-element phased-array transceiver IC with concurrent dual polarized beams and 1.4 degree beam-steering resolution for 5G communication. In IEEE International Solid-State Circuits Conference (ISSCC) (pp. 128–129). https://doi.org/10.1109/ISSCC.2017.7870294

Dunworth, J.D., Homayoun, A., Ku, B.-H., Ou, Y.-C., Chakraborty, K., Liu, G., Segoria, T., Lerdworatawee, J., Park, J.W., Park, H.-C., Hedayati, H., Lu, D., Monat, P., Douglas, K., & Aparin, V. (2018). A 28GHz Bulk-CMOS dual-polarization phased-array transceiver with 24 channels for 5G user and basestation equipment. In IEEE International Solid-State Circuits Conference (ISSCC) (pp. 70–72). https://doi.org/10.1109/ISSCC.2018.8310188

Pang, J., Wu, R., Wang, Y., Dome, M., Kato, H., Huang, H., Tharayil Narayanan, A., Liu, H., Liu, B., Nakamura, T., Fujimura, T., Kawabuchi, M., Kubozoe, R., Miura, T., Matsumoto, D., Li, Z., Oshima, N., Motoi, K., Hori, S., … Okada, K. (2019). A 28-GHz CMOS phased-array transceiver based on LO phase-shifting architecture with gain invariant phase tuning for 5G new radio. IEEE Journal of Solid-State Circuits, 54(5), 1228–1242. https://doi.org/10.1109/JSSC.2019.2899734

Verma, A., Bhagavatula, V., Singh, A., Wu, W., Nagarajan, H., Lau, P.-K., Yu, X., Elsayed, O., Jain, A., Sarkar, A., Zhang, F., Kuo, C.-C., McElwee, P., Chiang, P.-Y., Guo, C., Bai, Z., Chang, T., Mann, A., Rydin, A., Zhao, X., Lee, J., Yoon, D., Yao, C.-W., Lu, S.I., Son, S.W., & Cho, T.B. (2022). A 16-Channel, 28/39GHz Dual-Polarized 5G FR2 Phased-Array Transceiver IC with a Quad-Stream IF Transceiver Supporting Non-Contiguous Carrier Aggregation up to 1.6GHz BW. In IEEE International Solid-State Circuits Conference (ISSCC) (vol. 65, pp. 1–3). https://doi.org/10.1109/ISSCC42614.2022.9731664

Pang, J., Zhang, Y., Li, Z., Tang, M., Liao, Y., Fadila, A.A., Shirane, A., & Okada, K. (2022). A Power-Efficient 24-to-71 GHz CMOS Phased-Array Receiver Utilizing Harmonic-Selection Technique Supporting 36dB Inter-Band Blocker Rejection for 5G NR. In IEEE International Solid-State Circuits Conference (ISSCC) (vol. 65, pp. 434–436). https://doi.org/10.1109/ISSCC42614.2022.9731619

Elgaard, C., Andersson, S., Caputa, P., Westesson, E., & Sjöland, H. (2019). A 27 GHz Adaptive Bias Variable Gain Power Amplifier and T/R Switch in 22nm FD-SOI CMOS for 5G Antenna Arrays. In IEEE Radio Frequency Integrated Circuits Symposium (RFIC) (pp. 303–306). https://doi.org/10.1109/RFIC.2019.8701819

Chappidi, C.R., Sharma, T., Liu, Z., & Sengupta, K. (2020). Load Modulated Balanced mm-Wave CMOS PA with Integrated Linearity Enhancement for 5G applications. In IEEE IEEE/MTT-S International Microwave Symposium (IMS) (pp. 1101–1104). https://doi.org/10.1109/IMS30576.2020.9224038

Jin, Y., & Hong, S. (2021). A 24-GHz CMOS power amplifier with dynamic feedback and adaptive bias controls. IEEE Microwave and Wireless Components Letters, 31(2), 153–156. https://doi.org/10.1109/LMWC.2020.3038041

Chen, S., Wang, G., Cheng, Z., Qin, P., & Xue, Q. (2017). Adaptively biased 60-GHz Doherty power amplifier in 65-nm CMOS. Microwave and Wireless Components Letters, 27(3), 296–298. https://doi.org/10.1109/LMWC.2017.2662011

Nguyen, H.T., Chi, T., Li, S., & Wang, H. (2018). A 62-to-68ghz linear 6gb/s 64qam cmos doherty radiator with 27.5%/20.1% pae at peak/6db-back-off output power leveraging high-efficiency multi-feed antenna-based active load modulation. In 2018 IEEE International Solid-State Circuits Conference - (ISSCC) (pp. 402–404). https://doi.org/10.1109/ISSCC.2018.8310354

Nguyen, H.T., & Wang, H. (2019). A Coupler-Based Differential Doherty Power Amplifier with Built-In Baluns for High Mm-Wave Linear-Yet-Efficient Gbit/s Amplifications. In IEEE Radio Frequency Integrated Circuits Symposium (RFIC) (pp. 195–198). https://doi.org/10.1109/RFIC.2019.8701814

Zhang, H., Zhan, R.-Z., Li, Y. C., & Mou, J. (2020). High efficiency Doherty power amplifier using dual-adaptive biases. IEEE Transactions on Circuits and Systems I: Regular Papers, 67(8), 2625–2634. https://doi.org/10.1109/TCSI.2020.2977770

Zong, Z., Tang, X., Khalaf, K., Yan, D., Mangraviti, G., Nguyen, J., Liu, Y., & Wambacq, P. (2021). A 28-GHz SOI-CMOS Doherty power amplifier with a compact transformer-based output combiner. IEEE Transactions on Microwave Theory and Techniques, 69(6), 2795–2808. https://doi.org/10.1109/TMTT.2021.3064022

Pashaeifar, M., Vreede, L. C. N., & Alavi, M. S. (2022). A millimeter-wave CMOS series-Doherty power amplifier with post-silicon inter-stage passive validation. IEEE Journal of Solid-State Circuits, 57(10), 2999–3013. https://doi.org/10.1109/JSSC.2022.3175685

Colantonio, P., Giannini, F., Giofrè, R., & Piazzon, L. (2009). The AB-C Doherty power amplifier. Part I: theory. International Journal of RF and Microwave Computer-Aided Engineering, 19, 293–306.

Colantonio, P., Giannini, F., Giofrè, R., & Piazzon, L. (2009). High Efficiency RF and Microwave Solid State Power Amplifiers, 1st edn. IntechOpen

Cripps, S. C. (1999). RF power amplifiers for wireless communications (1st ed.). Artech House.

Funding

Open access funding provided by Lund University.

Author information

Authors and Affiliations

Contributions

Christian Elgaard is the initiator of the idea to analytically analyse the basic operation of a Doherty amplifier, and to analyse the impact of using adaptive bias to linearise the output current from the class C biased auxiliary amplifier. Christian Elgaard also did the analytical circuit derivations and produced the resulting plots, and the supporting measurements and comparisons with the theory. Christian Elgaard compiled the manuscript. Henrik Sjöland provided valuable feedback during the whole process and with emphasis on finalizing the manuscript.

Corresponding author

Ethics declarations

Conflict of interest

The authors declare no Conflict of interest.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Elgaard, C., Sjöland, H. Analysis and design of a GHz bandwidth adaptive bias circuit for an mmW Doherty amplifier. Analog Integr Circ Sig Process 120, 39–58 (2024). https://doi.org/10.1007/s10470-024-02288-7

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-024-02288-7