Abstract

In this paper, the electrochemical etching process is used for surface modification of the p-Si wafer, named as porous silicon (PS), in the metal–semiconductor (MS) type Schottky diode (SD) with a structure of Al/p-Si. Five regions of PS wafer with different etching rates are selected for comparison of them which are called P2, P3, P4, and P5 (P1 is the reference area without porosity). The morphological, structural, and electrical properties of the PS used in the MS-type SD are investigated using field-emission scanning electron microscope (FE-SEM) images, energy dispersive X-ray (EDX) analysis, and current–voltage (I–V) characteristics, respectively. The FE-SEM images show a meaningful effect on the porosity. The EDX spectrum demonstrates the importance of the chemical effects in addition to the physical changes in the porosity process of the p-Si wafer. The reverse-saturation current (I0), ideality factor (n), barrier height at zero-bias (ΦB0), and series/shunt electrical resistances are also computed and compared. Some of these parameters (n, Rs, BH) are determined using different methods, namely Thermionic emission (TE), Cheung functions, and modified Norde, and they exhibit strong agreement with each other. The energy-dependent profiles of surface states (Nss) are estimated from the I–V data by considering the voltage dependence of ΦB (V) and n(V). All the experimental findings indicate that the etching process of the p-Si wafer significantly influences the electrical performance of the Al/p-Si Schottky diode by increasing the extent of etching.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

In recent years, the primary challenges in metal–semiconductor (MS) type contacts or Schottky diodes (SDs), whether with or without a native or grown interlayer, revolve around enhancing their performance. This involves reducing parameters such as Rs, Nss, leakage current, while simultaneously increasing the rectifying rate (RR = IF/IR at sufficiently high forward and reverse bias voltages), shunt resistance (Rsh), and barrier height (BH). The structural characteristics and electrical properties of these devices typically rely on factors like surface preparation, the nature of the interlayer at the metal/semiconductor interface, BH, doping levels, operating frequency, applied voltage, and temperature [1,2,3,4,5,6]. Therefore, in the last five decades, especially semiconductor nanostructures have been considered much attention because of their physical and chemical properties to improve their performance [7,8,9,10]. Among these inorganic materials (Si, Ge, GaAs, InP, CdS/CdTe), Si is one of the oldest and has low-cost, high stability, but unwanted high leakage current and Nss. Due to its unique properties, it is used in many applications in various fields, especially in electronics and semiconductor device fabrication technology, yet [11,12,13,14]. The unique characteristics of the Si are more evident when its dimensions are reduced. By deceasing the size and dimension of Si, its physical and chemical properties change due to the quantum confinement effect [15, 16].

Utilizing Si nanostructures instead of traditional antireflection (AR) layers presents a compelling alternative due to their unique light-trapping capabilities, particularly in the realm of photovoltaic devices. Si nanostructures have the potential to enhance light absorption over a broad spectrum range by exploiting various optical effects, such as light trapping, scattering, and resonance phenomena. Unlike conventional AR coatings that operate based on interference effects and are limited to specific wavelengths, Si nanostructures offer a more versatile and efficient means of managing light at the nanoscale. By leveraging the design flexibility and tunability of Si nanostructures, tailored optical properties can be achieved to maximize light absorption in photovoltaic applications, thereby improving overall device performance and efficiency [17,18,19,20].

There are various methods used for the manipulation of Si nanostructures to change its physical properties such as doping by other materials [21, 22] which is thermal annealing [23, 24], plasma treatment [25, 26], and electrochemical etching [8, 9]. The preparation of Si nanostructures, including Silicon Nanowires (SiNWs) and Silicon Nanorods (SiNRs) on the surface of silicon, has captured the interest of scientists. These nanostructures exhibit unique properties and have shown great potential for various applications in nanotechnology and electronics [27,28,29,30]. One of these types of manipulations is to create porosity in the Si structure and the production of PS. PS is a dielectric material composed of silicon dioxide (SiO2) and air, which has a structural heterogeneity much smaller than normal light wavelength [31]. Among these methods, electrochemical etching is one of the most widely used methods for the surface treatment of Si wafers. In this method, the surface morphology of the samples has changed with the condition of the electrochemical etching [32]. The surface treatment contains the formation of porosity in the structures of the Si semiconductors have different applications such as nonlinear optics [33], biology [34], solar cells (SCs) [35], fabrication of Bragg-reflectors [36], microelectronics [37], waveguides [38], optical filter [39], gas sensors [40], photoluminescence devices in the visible region [41], energy [42], drug industry [43], biotechnology [44], and some other complex optical devices due to its high surface-to-volume ratio, high reactivity, luminescence properties at room temperature, and its adaptive nature [45]. There are several studies on the optical and structural applications of PS reported by researchers [46,47,48].

Furthermore, the electrical characteristics and energy-dependent interface states of Schottky diodes (SDs), whether with or without an interlayer, have received substantial attention due to their significance in technological applications. An increase in the dielectric constant leads to a higher capacity for storing electronic charges or energy, resulting in the reduction of numerous factors such as Nss, Rs, and dislocations [14, 15]. Consequently, recent research efforts have focused on manipulating the modification of electronic and transport properties in conventional MS-type SDs by incorporating various interlayers with high-dielectric materials. This approach aims to mitigate leakage current, ideality factor (n), Nss, and series resistance (Rs), ultimately enhancing the device’s overall performance [49,50,51,52]. To our knowledge, the study of the electrophysical properties of PS structures has not been seriously investigated in detail and so nonclarified yet. In this research, we aimed that are conducted to control the main electrophysical parameters of the Al/p-Si (MS) structures by modifying the surface morphology of p-Si using the etching process. For this aim, the p-Si surface is divided into 5 partition with various porosity P1 to P5 areas. The surface morphology and structural analysis are investigated by recording the FE-SEM images and EDX spectrum, respectively. Moreover, the I–V measurements are performed in a wide voltage range (± 1.5 V). The main electronic features of the MS-type SD with a structure of Al/p-Si that its semiconductor has been poroused are calculated by the TE, Cheung functions, and modified Norde techniques. The energy-dependent Nss profile are obtained at P2, P3, P4, and P5 with different degree of porosity. The influence of the electrophysical etching process of the p-Si wafer on the electric response of Al/p-Si SD will be thoroughly discussed.

2 Experimental details

2.1 Materials, preparation, and instruments

A p-type double-side polished (100)-oriented p-Si wafers with a specific resistivity of 1–10 Ω cm were used to prepare porous silicon. The Si substrate was utilized along with a 50% HF solution, distilled water, and 99.99% ethanol. The process involved the electrochemical etching of silicon in the HF solution, leading to the partial dissolution of Si. It is vital to investigate and comprehend the influence of various factors that govern this process. The choice of electrolyte is crucial in the formation of porous silicon, with HF typically used in concentrations up to 50% in distilled water. After rinsing the samples with ethanol to eliminate any dirt, they were immersed in a diluted (50%) Hydrofluoric acid (HF) solution for 15 min to remove any native oxide layer. Subsequently, the samples were rinsed with ethanol again and left to dry in the ambient atmosphere for a few minutes. They were then stored immersed in plastic containers filled with methanol to prevent the reformation of oxide layers on their surfaces. Each sample was placed at the bottom of a Teflon singlet anodizing system and secured by a support material sheet, acting as the Anode, while a platinum mesh rod was positioned perpendicular to the Si surface at a distance of 1 cm, serving as the cathode. HF circulation during the etching process contributes to achieving good depth uniformity and enhances safety. A lateral geometry approach for porous silicon formation has been proposed, where a contact is deposited on the surface where the porous silicon will be formed. This method promotes lateral rather than depth-wise porous silicon formation, resulting in flat porous silicon/Si interfaces. Understanding the various factors influencing the electrochemical etching process is essential for producing uniform and high-quality porous silicon layers with desirable properties for diverse applications.

The prepared porous Si was utilized as an MS-type Schottky diode (SD) without any initial contact. To evaluate the surface morphology of the treated p-Si wafer, FE-SEM analysis was performed using the TeScan-Mira III instrument from Czech Republic. Electrical measurements were conducted on the sample using the Keithley 2450 Source-meter I–V characteristics system from the USA, spanning a broad range of applied bias voltages (± 1.5 V) at room temperature.

2.2 FE-SEM and EDX analysis

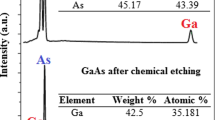

Figure 1 presents a schematic depiction of distinct porous silicon regions, illustrating their connection to FE-SEM images of porous silicon (PS) with varying degrees of p-Si surface etching, along with their corresponding EDX spectra. In this figure, the area P1 is related to the normal silicon region without manipulation, and the areas P2 to P5 correspond to the regions of the least to the highest amount of the etching process performed on the surface of the p-Si wafer, respectively.

As seen from Fig. 1, by increasing the amount of etching process, the porosity increase, so that the average value of porosity size has changed from 300 nm for the least amount of etching (P2) up to 2 μm for the maximum amount of etching (P5). The mean size of a different region of silicon is introduced in Table 1.

It is obvious that the oxygen species is the second sharp peak in the EDX spectrum after the Si peak. It indicates that the porosity process has a significant chemical effect in addition to the physical changes of the p-Si surface.

3 Results and discussion

The semi-logarithmic forward and reverse bias I–V characteristics of the different regions (P2–P5) of a p-type silicon wafer are shown in Fig. 2a.

The essential electrical characteristics, including I0, n, ΦB0, Rs, and Rsh of the manufactured MS-type Schottky diode (SD), are derived from the forward and reverse bias current–voltage (I–V) measurements using conventional thermionic emission (TE) theory. The expression describing the forward bias I–V relationship in terms of TE theory for V ≥ 3kT/q is provided as follows [53, 54]:

The terms before the square brackets are the I0 quantity which is obtained from the linear part of Ln(I)–V plot, A* is the effective Richardson constant, and other terms in Eq. 1 are well-known parameters of the MS-type SD explained elsewhere [53, 54]. The values of I0 for the P2, P3, P4, and P5 regions were found as 99.8 nA, 62.3 nA, 13.4 nA, and 15.2 nA, respectively. The n value is determined as the reciprocal of the slope derived from the linear portion of the natural logarithm of the current (I) versus voltage (V) plot, as illustrated below [53]:

Hence, the value of ΦB0 can be computed by utilizing the determined values of I0 and the surface area (A) of the Schottky diode (SD), as shown by [54]:

As shown in Fig. 2a, the P1 region without the etching process has almost an ohmic behavior, and gradually, by increasing the amount of the etching process, the I–V plot of the P2 to P5 regions exhibits rectifier behavior and these plots have a good linear region in the large bias voltage at intermediate bias region. The least rectifier rate (RR = IF/IR at ± 1.5 V) was found as 25.5 for the P2 region with the least porosity, and the highest RR was found to be 47.2 for P4 and its amount is 9.7 related to P5 region. In addition, the values of n were computed as 2.6, 2.5, 2.4, and 2.7 for the P2, P3, P4, and P5 regions, respectively. The values of n for each porous region are higher than the ideal case (n = 1), indicating that it deviates from standard thermionic emission (TE) theory. These higher values of n are attributed to the existence of a native SiO2 insulator layer, barrier height inhomogeneity at the MS junction, and Nss at the Al/p-Si interface [5, 49].

The series resistance (Rs) in Schottky diodes typically arises from various factors, including the formation of rectifying/ohmic contacts on the semiconductor, the bulk resistance of the semiconductor material, the contact points established by the probe wires connected to the Schottky contact, and dislocations occurring within the semiconductor’s bandgap. However, the actual values of Rs and Rsh are representative of sufficiently high forward and reverse biases, respectively. Different methodologies are employed to quantify Rs, each associated with distinct voltage regimes. Consequently, Rs is calculated using Ohm’s law, Cheung, and Norde techniques, and the results are compared. As a result, the values of I0, n, ΦB0, Rs, Rsh, and RR for various regions of porous silicon (PS) are presented in Table 2 for reference.

As shown in Table 2, P4 has the least n and I0, and the highest Rs, Rsh, RR, and ΦB0. Therefore, increasing the etching process (up to the P4 region) improves the quality of the MS-type SD and after that, the performance of the MS-type SD decreased with increasing porosity. Both Rs and Rsh values increase by increasing porosity. Increasing the Rsh value reduces and enhances the leakage current and the rectifying ratio of the MS-type SD. As shown in Table 2, the higher values of n and Rs indicate the deviation of ideal case or standard TE theory due to the formation of many Nss and inhomogeneity of BH at the MS junction [55,56,57,58,59,60].

As per the models established by Cheung [59], the series resistance (Rs) can be determined using the equations provided, based on the sufficiently high forward bias I–V data [59]:

In Eqs. 4a and 4b, the parameter IRs represents the voltage drop across the series resistance (Rs) in the MS-type SD. The expressions for dV/dln(I) and H(I) are derived from the I–V characteristics data. The experimental plots depicting dV/dln(I) and H(I) as functions of current (I) for various porous silicon (PS) regions are presented in Fig. 3.

Upon fitting the curve to a linear model and employing Eq. 4a, both Rs and n can be determined from the slope and the intercept of the fitted line. Likewise, the second Cheung function is employed to compute Rs and ΦB0 values, extracting them from the slope and intercept of H(I)–I plots.

Additionally, the Rs and ΦB0 values are able to be computed using Norde method developed by Bohlin for higher value of n as [47]:

In Eq. 5, γ represents a dimensionless integer that should be chosen to be greater than n. Following this approach, Rs and ΦB values can be determined by utilizing the minimum value of the F(V) function (refer to Fig. 4) and the corresponding voltage and current values. This is achieved by applying the following relationships [47]:

Consequently, the results for Rs, n, and ΦB acquired through the utilization of Cheung’s and Norde’s methods are presented in Table 3. As demonstrated in Table 3, the calculated values of BH obtained from the Norde and Cheung techniques exhibit a strong agreement, whereas the Rs values do not align due to the different voltage regions employed. Notably, unlike the Norde method, the Cheung function is exclusively applied to the concave portion of the forward bias I–V curve [61,62,63].

The formation of Nss during fabrication and the order in the periodic lattice also have remarkable influence on the performance of the SDs like Rs. Energy dependence of them can be calculate from the I–V data using following relations given by Roderick [54]:

Moreover, the energy dependence of Nss with respect to the bottom of the valance (EV) at the surface of p-Si wafer is given as [54]:

Thus, the Nss in terms of (EV − Ess) for p-type semiconductor can obtained as follow [13]:

In this context, δ represents the interlayer thickness, WD denotes the width of the depletion layer, εi = 3.8ε0 stands for the permittivity of SiO2, εs = 11.8 ε0 signifies the permittivity of silicon, and ε0 represents the permittivity of vacuum. Thus, Nss vs (Ess − Ev) profile at different regions of PS are obtained using Eqs. 8a–9b and introduced in Fig. 5.

As shown in Fig. 5, the energy values of the Nss at P2, P3, P4, and P5 regions are in the range of 0.42 eV − Ev to 0.67 eV − Ev. The magnitude of Nss at 0.42 eV − Ev are 1.8 × 1013 eV−1 cm−2, 2.7 × 1013 eV−1 cm−2, 3.1 × 1013 eV−1 cm−2, and 3.6 × 1013 eV−1 cm−2, and its value at 0.67 eV − Ev are 8.6 × 1012 eV−1 cm−2, 9.9 × 1012 eV−1 cm−2, 1.6 × 1013 eV−1 cm−2, and 1.9 × 1013 eV−1 cm−2 at P2, P3, P4 and P5 regions of PS, respectively. Since the interlayer is inherently identical across all regions, the Nss magnitude remains approximately consistent throughout. But the energy dependence of the Nss at different regions is different. At low porosity region (P2), the density of interface states decreased with increasing energy, while in high porosity region (P5), with increasing energy, the Nss decreased and then increased again after a minimum value.

4 Conclusions

The effect of etching process on the morphological, structural, and electrical features of the porous p-Si (PS) used in the MS-type SD was investigated using I–V measurement in the voltage range of ± 1.5 V at room temperature. For this aim, five regions of PS wafer with different etching rate were selected for comparison of them which are called P1, P2, P3, P4 and P5. Firstly, surface morphology was investigated by FE-SEM images and experimental results show meaningful effect on the porosity. Moreover, the sharpened peak after the Si peak in the EDX spectrum was related to the oxygen, indicating that the chemical effects are as crucial as physical changes in the porosity process on the p-Si surface. Secondly, the key electrical parameters, including I0, n, ΦB0, Rs, and Rsh, were computed and juxtaposed using standard TE (thermionic emission) theory, Cheung functions, and modified Norde functions, each pertaining to distinct voltage ranges. The energy-dependent profiles of interface states (Nss) were likewise derived from forward bias I–V data, taking into account the voltage-dependent variations of ΦB(V) and n(V). All the results obtained collectively indicate that the electrophysical etching process of the p-Si wafer within the context of the MS-type Schottky diode (SD) significantly influences its electrical performance by amplifying the extent of the etching process.

Data availability

The data that support the findings of this study are available from the corresponding author, [Y-B], upon reasonable request.

References

H. Sharma, S.N. Sharma, G. Singh, S. Shivaprasad, Effect of ratios of Cd: Se in CdSe nanoparticles on optical edge shifts and photoluminescence properties. Phys. E: Low-dimens. Syst. Nanostruct. 31, 180–186 (2006)

S. Baskoutas, A.F. Terzis, Size-dependent band gap of colloidal quantum dots. J. Appl. Phys. 99, 013708 (2006)

S. Kolahi, S. Farjami-Shayesteh, Y. Azizian-Kalandaragh, Comparative studies on energy-dependence of reduced effective mass in quantum confined ZnS semiconductor nanocrystals prepared in polymer matrix. Mater. Sci. Semicond. Process. 14, 294–301 (2011)

Y. Azizian-Kalandaragh, A. Khodayari, Z. Zeng, C.S. Garoufalis, S. Baskoutas, L.C. Gontard, Strong quantum confinement effects in SnS nanocrystals produced by ultrasound-assisted method. J. Nanopart. Res. 15, 1388 (2013)

Y. Azizian-Kalandaragh, N. Alizadeh-Siakeshi, Comparison of quantum confinement effect on the reduced effective mass of CdSe nanocrystals prepared by different methods. J. Optoelectron. Adv. Mater. 16, 345–350 (2014)

B. Akin, G. Pirgholi-Givi, J. Farazin, Y. Azizian-Kalandaragh, Ş. Altindal, Utilization of Al2O3/PVP nanocomposite as an interfacial layer for Schottky structures. 2019 thirteenth international congress on artificial materials for novel wave phenomena (metamaterials) (IEEE, 2019), p. X-017–X-019

U. Woggon, Optical Properties of Semiconductor Quantum Dots (Springer, Berlin, 1997)

S.V. Zabotnov, S.O. Konorov, L.A. Golovan, A.B. Fedotov, V.Y. Timoshenko, A.M. Zheltikov, P.K. Kashkarov, Modification of cubic susceptibility tensor in birefringent porous silicon. Phys. Status Solidi 202, 1673–1677 (2005)

V.Y. Gayvoronsky, M. Kopylovsky, Y.V. Gromov, S. Zabotnov, N. Piskunov, L. Golovan, V.Y. Timoshenko, P. Kashkarov, G. Fang, C. Li, Enhancement of two-photon absorption in anisotropic mesoporous silicon. Laser Phys. Lett. 5, 894 (2008)

M. Bruchez, M. Moronne, P. Gin, S. Weiss, A.P. Alivisatos, Semiconductor nanocrystals as fluorescent biological labels. Science 281, 2013–2016 (1998)

A. Werber, H. Zappe, Tunable, membrane-based, pneumatic micro-mirrors. J. Opt. A: Pure Appl. Opt. 8, S313 (2006)

H. Kudo, T. Sawada, E. Kazawa, H. Yoshida, Y. Iwasaki, K. Mitsubayashi, A flexible and wearable glucose sensor based on functional polymers with soft-MEMS techniques. Biosens. Bioelectron. 22, 558–562 (2006)

H.-P. Chou, M.A. Unger, S.R. Quake, A microfabricated rotary pump. Biomed. Microdevice 3, 323–330 (2001)

A.B. Uluşan, A. Tataroğlu, Y. Azizian-Kalandaragh, Ş Altındal, On the conduction mechanisms of Au/(Cu2O-CuO–PVA)/n-Si (MPS) Schottky barrier diodes (SBDs) using current–voltage–temperature (I–V–T) characteristics. J. Mater. Sci.: Mater. Electron. 29, 159–170 (2018)

V. Lehmann, U. Gösele, Porous silicon formation: a quantum wire effect. Appl. Phys. Lett. 58, 856–858 (1991)

J. Farazin, G. Pirgholi-Givi, Y. Azizian-Kalandaragh, Wettability measurement, optical characteristics, and investigation of the quantum confinement effect of ZnS-scotch tape nanocomposite films prepared by successive ionic layer adsorption and reaction (SILAR) method. Phys. B: Condens. Matter 564, 94–103 (2019)

A.F. Ahmed, M.R. Abdulameer, M.M. Kadhim, F.A. Mutlak, Plasma parameters of Au nano-particles ablated on porous silicon produced via Nd-YAG laser at 355 nm for sensing NH3 gas. Optik 249, 168260 (2022)

Q.K. Hammad, A.N. Ayyash, F.A. Mutlak, Improving SERS substrates with Au/Ag-coated Si nanostructures generated by laser ablation synthesis in PVA. J. Opt. 52, 1528–1536 (2023)

N.H. Harb, F.A. Mutlak, Production and characterization of porous silicon via laser-assisted etching: effect of gamma irradiation. Optik 246, 167800 (2021)

D.H. Jwied, U.M. Nayef, F.A. Mutlak, Synthesis of C: Se nanoparticles via laser ablated with magnetic field on porous silicon for gas sensor applications. Optic 242, 167207 (2021)

X. Tang, G. Wen, Y. Song, Stable silicon/3D porous N-doped graphene composite for lithium-ion battery anodes with self-assembly. Appl. Surf. Sci. 436, 398–404 (2018)

A. Lyuleeva, P. Holzmüller, T. Helbich, M. Stutzmann, M.S. Brandt, M. Becherer, P. Lugli, B. Rieger, Charge transfer doping in functionalized silicon nanosheets/P3HT hybrid material for applications in electrolyte-gated field-effect transistors. J. Mater. Chem. C 6, 7343–7352 (2018)

B. Macco, J. Melskens, N.J. Podraza, K. Arts, C. Pugh, O. Thomas, W.M. Kessels, Correlating the silicon surface passivation to the nanostructure of low-temperature a-Si: H after rapid thermal annealing. J. Appl. Phys. 122, 035302 (2017)

M. Kim, M. Abbott, N. Nampalli, S. Wenham, B. Stefani, B. Hallam, Modulating the extent of fast and slow boron-oxygen related degradation in Czochralski silicon by thermal annealing: evidence of a single defect. J. Appl. Phys. 121, 053106 (2017)

M. Wiegand, M. Reiche, U. Gösele, Time-dependent surface properties and wafer bonding of O2-plasma-treated silicon (100) surfaces. J. Electrochem. Soc. 147, 2734–2740 (2000)

A. Descoeudres, L. Barraud, S. De Wolf, B. Strahm, D. Lachenal, C. Guérin, Z. Holman, F. Zicarelli, B. Demaurex, J. Seif, Improved amorphous/crystalline silicon interface passivation by hydrogen plasma treatment. Appl. Phys. Lett. 99, 123506 (2011)

Z. Huang, H. Fang, J. Zhu, Fabrication of silicon nanowire arrays with controlled diameter, length, and density. Adv. Mater. 19, 744–748 (2007)

Y. Cui, L.J. Lauhon, M.S. Gudiksen, J. Wang, C.M. Lieber, Diameter-controlled synthesis of single-crystal silicon nanowires. Appl. Phys. Lett. 78, 2214–2216 (2001)

F.M. Ross, J. Tersoff, M.C. Reuter, Sawtooth faceting in silicon nanowires. Phys. Rev. Lett. 95, 146104–146108 (2005)

L. Boarino, D. Imbraguglio, E. Enrico, N. De Leo, F. Celegato, P. Tiberto, N. Pugno, G. Amato, Fabrication of ordered silicon nanopillars and nanowires by self-assembly and metal-assisted etching. Phys. Status Solidi A 208, 1412–1416 (2011)

O. Bisi, S. Ossicini, L. Pavesi, Porous silicon: a quantum sponge structure for silicon based optoelectronics. Surf. Sci. Rep. 38, 1–126 (2000)

S. Zabotnov, A. Ezhov, M. Lastovkina, V. Panov, V.Y. Timoshenko, P. Kashkarov, Formation of nanoparticles on the silicon surface under the effect of femtosecond laser pulses. Semiconductors 41, 998–1001 (2007)

L.T. Canham, Properties of Porous Silicon (Institution of Electrical Engineers, London, 1997)

R. Collins, P. Fauchet, M. Tischler, Phys. Today, 24 (January 1997); LC Kimerling, KD Kolenbrander, J. Michel, and J. Palm. Solid State Phys. 50, 333 (1997)

C.J. Oton, M. Ghulinyan, Z. Gaburro, P. Bettotti, L. Pavesi, L. Pancheri, S. Gialanella, N. Capuj, Scattering rings as a tool for birefringence measurements in porous silicon. J. Appl. Phys. 94, 6334–6340 (2003)

V. Agarwal, J. Del Rıo, Tailoring the photonic band gap of a porous silicon dielectric mirror. Appl. Phys. Lett. 82, 1512–1514 (2003)

P. Yang, R. Yan, M. Fardy, Semiconductor nanowire: what’s next? Nano Lett. 10, 1529–1536 (2010)

P. Ferrand, R. Romestain, J. Vial, Photonic band-gap properties of a porous silicon periodic planar waveguide. Phys. Rev. B 63, 115106 (2001)

C. Mazzoleni, L. Pavesi, Application to optical components of dielectric porous silicon multilayers. Appl. Phys. Lett. 67, 2983–2985 (1995)

L. Pavesi, C. Mazzoleni, A. Tredicucci, V. Pellegrini, Controlled photon emission in porous silicon microcavities. Appl. Phys. Lett. 67, 3280–3282 (1995)

Y. Zhou, P. Snow, P.S.J. Russell, Strong modification of photoluminescence in erbium-doped porous silicon microcavities. Appl. Phys. Lett. 77, 2440–2442 (2000)

R. Dubey, D. Gautam, Fabrication and characterization of porous silicon layers for applications in optoelectronics. Opt. Quantum Electron. 41, 189 (2009)

P. Calcott, K. Nash, L. Canham, M. Kane, D. Brumhead, Identification of radiative transitions in highly porous silicon. J. Phys.: Condens. Matter 5, L91 (1993)

G. Barillaro, A. Diligenti, F. Pieri, F. Fuso, M. Allegrini, Integrated porous-silicon light-emitting diodes: a fabrication process using graded doping profiles. Appl. Phys. Lett. 78, 4154–4156 (2001)

S. Dhanekar, S. Jain, Porous silicon biosensor: current status. Biosens. Bioelectron. 41, 54–64 (2013)

H. Föll, M. Christophersen, J. Carstensen, G. Hasse, Formation and application of porous silicon. Mater. Sci. Eng.: R.: Rep. 39, 93–141 (2002)

A. Efimova, A. Eliseev, V. Georgobiani, M. Kholodov, A. Kolchin, D. Presnov, N. Tkachenko, S. Zabotnov, L. Golovan, P. Kashkarov, Enhanced photon lifetime in silicon nanowire arrays and increased efficiency of optical processes in them. Opt. Quantum Electron. 48, 232 (2016)

A. Sokolov, V.Y. Timoshenko, A. Semenov, A. Pastushenko, T. Nychyporuk, V. Lysenko, Increase in the lifetime of a photon and in the efficiency of Raman scattering and second-harmonic generation processes in porous silicon carbide. JETP Lett. 101, 793–797 (2015)

A. Barkhordari, S. Özçelik, Ş Altındal, G. Pirgholi-Givi, H. Mashayekhi, Y. Azizian-Kalandaragh, The effect of PVP: BaTiO3 interlayer on the conduction mechanism and electrical properties at MPS structures. Phys. Scr. 96, 085805 (2021)

Ş Altındal, A. Barkhordari, S. Özçelik, G. Pirgholi-Givi, H.R. Mashayekhi, Y. Azizian-Kalandaragh, A comparison of electrical characteristics of Au/n-Si (MS) structures with PVC and (PVC: Sm2O3) polymer interlayer. Phys. Scr. 96, 125838 (2021)

Ö. Sevgili, I. Tasçioglu, S. Boughdachi, Y. Azizian-Kalandaragh, S. Altindal, Examination of dielectric response of Au/HgS-PVA/n-Si (MPS) structure by impedance spectroscopy method. Phys. B: Condens. Matter 566, 125–135 (2019)

A. Barkhordari, H.R. Mashayekhi, P. Amiri, Ş Altındal, Y. Azizian-Kalandaragh, Role of graphene nanoparticles on the electrophysical processes in PVP and PVP: ZnTiO3 polymer layers at Schottky diode (SD). Semicond. Sci. Technol. 38, 075002 (2023)

S.M. Sze, Semiconductor Devices: Physics and Technology (Wiley, Singapore, 2008)

E. Rhoderick, R. Williams, Metal-Semiconductor Contacts (Clarendon Press, Oxford, 1988)

Y. Azizian-Kalandaragh, Preparation of lead oxide nanostructures in presence of polyvinyl alcohol (PVA) as capping agent and investigation of their structural and optical properties. J. Semicond. Technol. Sci. 18, 91–99 (2018)

S. Demirezen, Ş Altındal, Y. Azizian-Kalandaragh, A.M. Akbaş, A comparison of Au/n-Si Schottky diodes (SDs) with/without a nanographite (NG) interfacial layer by considering interlayer, surface states (Nss) and series resistance (Rs) effects. Phys. Scr. 97, 055811 (2022)

Ş Karataş, Ş Altındal, M. Ulusoy, Y. Azizian-Kalandaragh, S. Özçelik, Temperature dependence of electrical characteristics and interface state densities of Au/n-type Si structures with SnS doped PVC interface. Phys. Scr. 97, 095816 (2022)

A. Di Bartolomeo, F. Giubileo, G. Luongo, L. Iemmo, N. Martucciello, G. Niu, M. Fraschke, O. Skibitzki, T. Schroeder, G. Lupina, Tunable Schottky barrier and high responsivity in graphene/Si-nanotip optoelectronic device. 2D Mater. 4, 015024 (2016)

Z. Hosseini, Y. Azizian-Kalandaragh, S. Sobhanian, G. Pirgholi-Givi, M. Kouhi, Comparison of capacitance-frequency and current–voltage characteristics of Al/CdS-PVP/p-Si and Al/p-Si structures. Phys. B: Condens. Matter 640, 413836 (2022)

N. Hamdaoui, D. Tlili, Y. Azizian-Kalandaragh, B. Zaidi, S. Zemni, A. Ahmed Akl, L. Beji, Effect of Ni-doping on the structural, magnetic, and electronic properties of La0.2Sr0.8MnO3 perovskite. J. Mater. Sci.: Mater. Electron. 32, 1–14 (2021)

M. Ulusoy, Ş Altındal, Y. Azizian-Kalandaragh, S. Özçelik, Z. Mirzaei-Kalar, The electrical characteristic of an MIS structure with biocompatible minerals doped (Brushite+ Monetite: PVC) interface layer. Microelectron. Eng. 258, 111768 (2022)

H. Card, E. Rhoderick, Studies of tunnel MOS diodes I. Interface effects in silicon Schottky diodes. J. Phys. D: Appl. Phys. 4, 1589 (1971)

B. Akin, J. Farazin, Ş Altındal, Y. Azizian-Kalandaragh, A comparison electric-dielectric features of Al/p-Si (MS) and Al/(Al2O3: PVP)/p-Si (MPS) structures using voltage–current (V–I) and frequency–impedance (f–Z) measurements. J. Mater. Sci.: Mater. Electron. 33, 21963–21975 (2022)

Funding

Open access funding provided by the Scientific and Technological Research Council of Türkiye (TÜBİTAK).

Author information

Authors and Affiliations

Contributions

Yosef Badali: conceptualization, methodology, writing, reviewing and editing, data analyzing, Yashar Azizian-Kalandaragh: reviewing, methodology, writing, reviewing and editing, data analyzing.

Corresponding author

Ethics declarations

Conflict of interest

The authors declare no financial or commercial conflict of interest.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Badali, Y., Azizian-Kalandaragh, Y. The influence of the physicochemical processes on the electrical response of Al/p-Si structure with etched surface. Appl. Phys. A 130, 243 (2024). https://doi.org/10.1007/s00339-024-07393-y

Received:

Accepted:

Published:

DOI: https://doi.org/10.1007/s00339-024-07393-y