Abstract

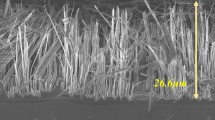

This article focused on the electrical characterization of silicon nanowires Schottky barriers following structural analysis of nanowires grown on p-type silicon by Metal (Ag) Assisted Chemical Etching (MACE) method distinguished by their different etching time (5 min, 10 min, 25 min). The silicon nanowires (SiNWs) are well aligned and distributed almost uniformly over the surface of a silicon wafer. In order to enable electrical measurement of the silicon nanowires device, Schottky barriers were performed by depositing Al on the vertically aligned silicon nanowires arrays. The electrical properties of the resulting Al/SiNWs diodes were characterized by current voltage I-V and capacity voltage C-V measurements. Unlike the conventional Schottky diode, asymmetrical current-voltage I-V characteristic has been observed with a rectification ratio <4. The metal-semiconductor-metal (M-S-M) model was used to analyze the I-V characteristics by including two Schottky barriers at the interface between metal and silicon nanowires. The electron transport behavior is explained by the thermionic field emission method (TFE) which adds the effect of the tunneling current compared to the conventional thermionic emission theory. The capacitance-voltage C-V characteristics of silicon nanowires depend on the bias voltage showing that the samples have an obvious space charge region. Symmetric behavior also appears in the C –V curves that confirm the MSM model.

Similar content being viewed by others

Data Availability

Raw data and material are available on request.

References

Adachi MM, Anantram MP, Karim KS (2013) Core-shell silicon nanowire solar cells. Sci Rep 3(1):1–6

Amri C et al (2016) Effect of acid vapor etching on morphological and opto-electric properties of flat silicon and silicon nanowire arrays: a comparative study. Superlattices Microstruct 91:278–289

Amri C et al (2017) Effect of silver-assisted chemical vapor etching on morphological properties and silicon solar cell performance. Mater Sci Semicond Process 63:176–183

Card HC, Rhoderick EH (1971) Studies of tunnel MOS diodes I. Interface effects in silicon Schottky diodes. J Phys D: Appl Phys 4(10):1589

Chang CY, Sze SM (1970) Carrier transport across metal-semiconductor barriers. Solid State Electron 13(6):727–740

Cheung SK, Cheung NW (1986) Extraction of Schottky diode parametersfromforwardcurrent-voltage characteristics. Appl Phys Lett 49(2):85–87

Cho WM, Lin YJ, Chang HC, Chen YH (2013) Electronic transport for polymer/Si-nanowire arrays/n-type Si diodes with and without Si-nanowire surface passivation. Microelectron Eng 108:24–27

Elogail Y, Kasper E, Gunzer F, Shaker A, Schulze J (2016) Investigation of capacitance voltage characteristics of strained Si/SiGe n-channel MODFET varactor. Solid State Sci 56:73–78

Garnett EC, Tseng YC, Khanal DR, Wu J, Bokor J, Yang P (2009) Dopant profiling and surface analysis of silicon nanowires using capacitance–voltage measurements. Nat Nanotechnol 4(5):311–314

Geppert DV, Cowley AM, Dore BV (1966) Correlation of metal-semiconductor barrier height and metal work function; effects of surface states. J Appl Phys 37(6):2458–2467

Gunawan O, Guha S (2009) Characteristics of vapor–liquid–solid grown silicon nanowire solar cells. Sol Energy Mater Sol Cells 93(8):1388–1393

Hu L, Chen G (2007) Analysis of optical absorption in silicon nanowire arrays for photovoltaic applications. Nano Lett 7(11):3249–3252

Kuo CH, Wu JM, Lin SJ (2013) Room temperature-synthesized vertically aligned InSb nanowires: electrical transport and field emission characteristics. Nanoscale Res Lett 8(1):1–8

Lichtenberger D, Ellmer K, Schieck R, Fiechter S, Tributsch H (1994) Structural, optical and electrical properties of polycrystalline iron pyrite layers deposited by reactive dc magnetron sputtering. Thin Solid Films 246(1–2):6–12

Naik BN, Agarwal L, Tripathi S (2017) Microstructural and electrical characterization of Pt/Si nanowires Schottky diode grown by metal assisted chemical etching method. Int J Thin Fil Sci Tec 6(3):107–111

Onuma T et al (2014) Polarized Raman spectra in β-Ga2O3 single crystals. J Cryst Growth 401:330–333

Qi Y et al (2014) Electron transport characteristics of silicon nanowires by metal-assisted chemical etching. AIP Adv 4(3):031307

Qi Y, Wang Z, Zhang M, Wang X, Ji A, Yang F (2014) Electron transport characteristics of silicon nanowires by metal-assisted chemical etching. AIP Adv 4(3):031307

Ranga P et al (2019) Si-dopedβ-(Al0. 26Ga0. 74) 2O3 thin films and heterostructures grown by metalorganic vapor-phase epitaxy. Appl Phys Express 12(11):111004

Sarpatwari K et al (2010) Extracting the Schottky barrier height from axial contacts to semiconductor nanowires. Solid State Electron 54(7):689–695

Sermage B, Essa Z, Taleb N, Quillec M, Aubin J, Hartmann JM, Veillerot M (2016) Electrochemical capacitance voltage measurements in highly doped silicon and silicon-germanium alloys. J Appl Phys 119(15):155703

Svizhenko A, Leu PW, Cho K (2007) Effect of growth orientation and surface roughness on electron transport in silicon nanowires. Phys Rev B 75(12):125417

Taşdemir İH, Vural Ö, Dökme İ (2016) Electrical characteristics of p-Si/TiO2/Al and p-Si/TiO2-Zr/Al Schottky devices. Philos Mag (Abingdon) 96(16):1684–1693

Thelander C et al (2006) Nanowire-based one-dimensional electronics. Mater Today 9(10):28–35

Thor E et al (2001) Deep-level transient spectroscopy of dislocation-related defects in epitaxial multilayer structures. Appl Phys 90(5):2252–2256

Wang W, Li D, Tian M, Lee YC, Yang R (2012) Wafer-scale fabrication of silicon nanowire arrays with controllable dimensions. Appl Surf Sci 258(22):8649–8655

Zhang ZY, Jin CH, Liang XL, Chen Q, Peng LM (2006) Current-voltage characteristics and parameter retrieval of semiconducting nanowires. Appl Phys Lett 88(7):073102

Zhang C et al (2017) Fabrication of ultra-low antireflection SiNWs arrays from mc-Si using one step MACE. J Mater Sci – Mater El 28(12):8510–8518

Zhu M et al (2010) Effect of interfacial layer and series resistance on electrical characteristics for the PtSi/p-SiNWs Schottky diode. Physica E Low Dimens Syst Nanostruct 43(1):515–520

Acknowledgments

We wish to acknowledge the support of the authors in offering suggestions and encouragement, testing new versions.

Funding

No funding was received to assist with the preparation of this manuscript.

Author information

Authors and Affiliations

Contributions

Ahlem Rouis and Neila Hizem designed and performed the experiments, analyzed the results and prepared figures and wrote the manuscript.

Adel Kalboussi andMohamed Hassen supervised the entire research, coordinated with authors.

Corresponding author

Ethics declarations

Not applicable.

Consent to Participate

All authors voluntarily agree to participate in this research study.

Consent for Publication

In accordance with the copyright transfer or open access rules.

Conflict of Interest

Authors declare no conflict of interest.

Additional information

Publisher’s Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Rouis, A., Hizem, N., Hassen, M. et al. Electrical Properties of Silicon Nanowires Schottky Barriers Prepared by MACE at Different Etching Time. Silicon 14, 4731–4737 (2022). https://doi.org/10.1007/s12633-021-01261-7

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s12633-021-01261-7