Abstract

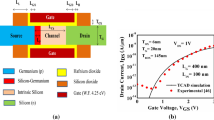

The charge-plasma based dopingless (DL) tunnel field effect transistor (TFET) is considered as an emerging TFET structure resulting from its immunity against random dopant fluctuations and not requiring high thermal budgets and expensive annealing methods for fabrication. But, temperature sensitivity is a major concern to predict the reliability of a device as the bandgap of semiconductor material changes under the influence of temperature variations when used in a system. Therefore, in this manuscript, the effect of variations in temperature (200–500 K) are investigated on the analog/RF and linearity characteristics of a Si/Ge hetero-junction (HJ) asymmetric double gate (ADG) DLTFET and abbreviated as HJ-ADG-DLTFET in the entire manuscript. In this context, Silvaco ATLAS simulator is used to evaluate DC and Analog/RF performance parameters such as \(I_{D}-V_{G}\) characteristics, transconductance (\(g_{m}\)), cut off frequency (\(f_{T}\)) and transconductance generation factor (TGF) considering effect of temperature variations. Furthermore, linearity parameters such as second- and third-order voltage intercept point (\(\mathrm{VIP}_{2}, \mathrm{VIP}_{3}\)), 1-dB compression point, third-order input-interception point (\(\mathrm{IIP}_{3}\)) and intermodulation distortion \((\mathrm{IMD}_{3})\) are also evaluated considering temperature variations as these FoM are significant for linear and analog/RF applications.

Similar content being viewed by others

References

A.C. Seabaugh, Q. Zhang, Low-voltage tunnel transistors for beyond CMOS logic. Proc. IEEE 98(12), 2095–2110 (2010)

B.R. Raad, D. Sharma, P. Kondekar, K. Nigam, D.S. Yadav, Drain work engineered doping-less charge plasma TFET for ambipolar suppression and RF performance improvement: a proposal. Des. Investig. IEEE Trans. Electron Devices 63(10), 3950–3957 (2016)

S. Kumar, K.S. Singh, K. Nigam, V.A. Tikkiwal, B.V. Chandan, Dual Material dual-oxide double gate TFET for improvement in DC Characteristics, analog/RF and linearity performance. Appl. Phys. A Mater. Sci. Process. 125(5), 353 (2019)

X. Duan, J. Zhang, S. Wang, Y. Li, S. Xu, Y. Hao, A high-performance gate engineered InGaN dopingless Tunnel FET. IEEE Trans. Electron Devices 65(3), 1223–1229 (2018)

J. Patel, D. Sharma, S. Yadav, A. Lemtur, P. Suman, Performance improvement of nano-wire TFET by hetero-dielectric and hetero-material: at device and circuit level. Microelectron. J. 85, 72–82 (2019)

D.B. Abdi, M.J. Kumar, In built \(N^{+}\) pocket p-n-p-n tunnel field-effect transistor. IEEE Electron Device Lett. 35(12), 1170–1172 (2014)

M.R. Tripathy, A.K. Singh, A. Samad, S. Chander, K. Baral, P.K. Singh, S. Jit, Device and Circuit-level assessment of GaSb/Si hetero-junction vertical Tunnel-FET for low-power applications. IEEE Trans. Electron Devices 67, 3 (2020)

P.N. Kondekar, K. Nigam, S. Pandey, D. Sharma, Design and analysis of polarity controlled electrically doped tunnel FET with bandgap engineering for analog/RF applications. IEEE Trans. Electron Devices 64(2), 412–418 (2017)

M.J. Kumar, S. Janardhanan, Doping-less tunnel field effect transistor: design and investigation. IEEE Trans. Electron Devices 60(10), 3285–3290 (2013)

P.K. Verma, S.K. Gupta, An improved analog/RF and linearity performances with small-signal parameter extraction of virtually doped recessed Source/Drain dopingless junctionless transistor for Radio-frequency applications. Silicon (2020)

M.A. Raushan, N. Alam, M.J. Siddiqui, Dopingless tunnel field effect transistor with oversized back gate: proposal and Investigation. IEEE Trans. Electron Devices 65(10), 4701–4708 (2018)

N. Kumar, A. Raman, Low voltage charge-plasma based dopingless tunnel field effect transistor?: analysis and optimization. Microsyst. Technol. 26(4), 1343–1350 (2020)

S. Sharma, B. Kaur, Performance investigation of asymmetric double-gate dopingless tunnel FET with Si/Ge heterojunction. IET Circuits Devices Syst. 14(5), 695–701 (2020)

S. Datta, H. Liu, V. Narayanan, Tunnel FET technology: a reliability perspective. Microelectron. Reliab. 54(5), 861–874 (2014)

A.E. Islam, Current status of reliability in Extended and beyond CMOS devices. IEEE Trans. Mater. Device Reliab. 16(4), 647–666 (2016)

Y. Varshni, Temperature dependence of energy gap in semiconductors. Physica 34(1), 149–154 (1967)

S. Saurabh, M.J. Kumar, Fundamentals of tunnel field effect transistor (CRC Press, 2016, Ist edn.), pp. 1–291

R. Narang, M. Saxena, R.S. Gupta, M. Gupta, Impact of temperature variations on the device and circuit performance of tunnel FET: a simulation study. IEEE Trans. Nanotechnol. 12(6), 951–957 (2013)

K. Boucart, A.M. Ionescu, Double gate tunnel FET with high-\(\kappa\) dielectric. IEEE Trans. Electron Devices 54(7), 1725–1733 (2007)

W. Shockley, W.T. Read, Statistics of the recombination of holes and electrons. Phys. Rev. 87(5), 835–842 (1952)

J.A. McDonald, Proving they can take the heat. III-Vs Rev. 9(5), 63–67 (1996)

A. Osman, M. Osman, Investigation of high temperature effects on MOSFET transconductance (\(g_{m}\)), in Proc. 4th Int. High Temp. Electron. Conf. (HITEC), 301–304, (2002)

S. Yadav, D. Sharma, B.V. Chandan, A novel hetero-material gate-underlap electrically doped TFET for improving DC/RF and ambipolar behavior. Superlattices MIcrostruct. 117, 9–17 (2018)

M.R.U. Shaikh, S.A. Loan, Drain-engineered TFET with fully suppressed ambipolarity for high-frequency application. IEEE Trans. Electron Devices 66(4), 1628–1634 (2019)

J. Robertson, High dielectric constant oxides. Eur. Phys. J. Appl. Phys. 28, 265–291 (2004)

A. Singh, S. Chaudhury, C. Pandey, Design and analysis of high-\(\kappa\) silicon nanotube tunnel FET device. IET Circuits Devices Syst. 13(8), 1305–1310 (2019)

ATLAS Device Simulation Software, Silvaco Int (Santa Clara, CA, 2014)

B. Rajasekharan, R.J.E. Hueting et al., Fabrication and characterization of the charge plasma diode. IEEE Electron Device Lett. 31(6), 528–530 (2010)

M.J. Kumar, K. Nadda, Bipolar charge-plasma transistor: a novel three terminal device. IEEE Trans. Electron Devices 59(4), 962–967 (2012)

H. Ye, J. Yu, Germanium epitaxy on silicon. Sci. Technol. Adv. Mater. 15(2), 024601 (2014)

P.Y. Wang, B.Y. Tsui, Experimental demonstration of p-channel germanium epitaxial tunnel layer (ETL) tunnel FET with high tunneling current and high ON/OFF ratio. IEEE Electron Device Lett. 36(12), 1264–1266 (2015)

Q. Xie, S. Deng, M. Schaekers et al., Germanium surface passivation and atomic layer deposition of high-k dielectrics: a tutorial review on Ge-based MOS capacitors. Semicond. Sci. Technol. 27(7), 074012 (2012)

J. Widiez, J. Lolivier, M. Vinet, Experimental evaluation of gate architecture influence on DG SOI MOSFETs performance. IEEE Trans. Electron Devices 52(8), 1772–1779 (2005)

R.W. Johnson, A. Hultqvist, S.F. Bent, A brief review of atomic layer deposition: from fundamentals to applications. Mater. Today 17(5), 236–246 (2014)

J.P. Kim, W.Y. Choi, J.Y. Song, S.W. Kim, J.D. Lee, B.G. Park, Design and fabrication of asymmetric MOSFETs using a novel self-aligned structure. IEEE Trans. Electron Devices 54(11), 2969–2974 (2007)

R. Lin, Q. Lu, P. Ranade et al., An adjustable work function technology using Mo gate for CMOS devices. IEEE Electron Device Lett. 23, 49–51 (2002)

J. Madan, R. Chaujar, Temperature associated reliability issues of heterogeneous gate dielectric gate all around Tunnel FET. IEEE Trans. Nanotechnol. 17(1), 41–48 (2018)

J. Min, L.D. Wang, J. Wu, P.M. Asbeck, Analysis of temperature dependent effects on I–V characteristics of heterostructure tunnel field effect transistors. IEEE J. Electron Devices Soc. 4(6), 416–423 (2016)

R. Saha, B. Bhowmick, S. Baishya, Temperature effect on RF/ analog and linearity parameters in DMGFinFET. Appl. Phys. A Mater. Sci. Process. 124, 642 (2018)

P. Ghosh, S. Haldar, R.S. Gupta, M. Gupta, An investigation of linearity performance and intermodulation distortion of GME CGT MOSFET for RFIC design. IEEE Trans. Electron Devices 59(12), 3263–3268 (2012)

B. Razavi, Microelectronics (Prentice-Hall, New York, 1998)

E. Datta, A. Chattopadhyay, A. Mallik, Y. Omura, Temperature dependence of analog performance, linearity and harmonic distortion for a ge-source tunnel FET. IEEE Trans. Electron Devices 67(3), 810–815 (2020)

K. Vanlalawmpuia, B. Bhowmick, Optimization of a hetero-structure vertical tunnel fet for enhanced electrical performance and effects of temperature variation on rf/linearity parameters. Silicon 13(1), 155–166 (2021)

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Sharma, S., Basu, R. & Kaur, B. Insights into temperature influence on analog/RF and linearity performance of a Si/Ge heterojunction asymmetric double gate dopingless TFET. Appl. Phys. A 127, 392 (2021). https://doi.org/10.1007/s00339-021-04541-6

Received:

Accepted:

Published:

DOI: https://doi.org/10.1007/s00339-021-04541-6